FPGAの基礎 – 第5部:Intel(Altera)のFPGAの概要

DigiKeyの北米担当編集者の提供

2020-05-07

編集者メモ:RISC、CISC、グラフィックスプロセッサとFPGAの組み合わせ、FPGA単独、またはファブリックの一部としてハードプロセッサコアを強化するFPGAによって最適な処理ソリューションが得られることがよくあります。しかし、設計者の多くはFPGAの機能、その発展の過程や使い方をよく知りません。 FPGAの基礎シリーズは複数のパートで構成されており、第1部では、FPGAの概要について紹介し、第2部ではLattice SemiconductorのFPGA製品に焦点を当て、第3部ではMicrochip Technologyが(その子会社であるMicrosemi Corporationを通じて)提供しているFPGAデバイスファミリと設計ツールを重点的に取り上げました。 第4部では、Xilinxのコンポーネントおよびツールの詳細を紹介しました。この第5部では、Alteraの製品について取り上げます。AlteraはIntelによって買収され、現在はIntelのProgrammable Solutions Group部門となっています(以降、この記事ではIntelの名前を使用します)。

第1部で説明したように、フィールドプログラム可能ゲートアレイ(FPGA)は、単体で使用しても異種アーキテクチャの中で使用しても重要なコンピューティング資産となることができる多くの特性を備えています。しかし、多くの設計者は、FPGAの機能やこれらのデバイスを設計に取り込む方法を十分に理解していません。この状況を解決するための1つの方法は、大手ベンダーが提供しているFPGAアーキテクチャとその関連ツールについて理解を深めることです。

高度なFPGAオプションの概要

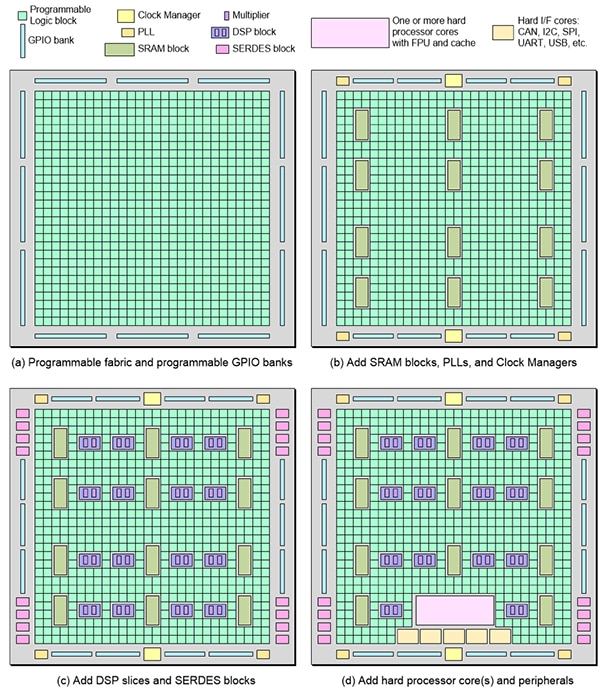

市場にはさまざまな種類のFPGAが出回り、それぞれに異なる機能が組み合わされています。FPGAの中心となるのがプログラム可能ファブリックです。これは、ロジックエレメント(LE)とも呼ばれるプログラム可能な論理ブロックの配列として表されます(図1(a))。次のFPGAファブリックの拡張には、ブロックRAM(BRAM)と呼ばれるSRAMのブロック、位相ロックループ(PLL)、クロックマネージャなどが含まれています(図1(b))。デジタル信号処理(DSP)ブロック(DSPスライス)と高速シリアライザ/デシリアライザ(SERDES)ブロックを追加することもできます(図1(c))。

図1:プログラム可能ファブリックと構成可能な汎用IO(GPIO)のみが含まれる最も簡易なFPGA(a)、基盤であるこのファブリックをSRAMブロック、PLL、クロックマネージャで拡張する各種アーキテクチャ(b)、DSPブロックとSERDESインターフェース(c)、およびハードプロセッサコアと周辺機器(d)。(画像提供:クリーブ・"マックス"・マックスフィールド氏)

図1:プログラム可能ファブリックと構成可能な汎用IO(GPIO)のみが含まれる最も簡易なFPGA(a)、基盤であるこのファブリックをSRAMブロック、PLL、クロックマネージャで拡張する各種アーキテクチャ(b)、DSPブロックとSERDESインターフェース(c)、およびハードプロセッサコアと周辺機器(d)。(画像提供:クリーブ・"マックス"・マックスフィールド氏)

CAN、I2C、SPI、UART、USBなどの周辺機器へのインターフェース機能はプログラム可能ファブリックにソフトコアとして実装できますが、多くのFPGAではハードコアとしてシリコンに組み込まれています。同様に、マイクロプロセッサをプログラム可能ファブリックにソフトコアとして、またはシリコンにハードコアとして実装できます(図1(d))。ハードプロセッサコアを備えたFPGAは、システムオンチップ(SoC)FPGAと呼ばれます。各FPGAが提供する機能、特長、性能、処理能力は、対象となる市場やアプリケーションに応じて異なります。

Intel(Alteraを買収)、Efinix、Lattice Semiconductor、Microchip Technology(AtmelおよびMicrosemiを買収)、およびXilinxなど、多数のFPGAベンダーが存在します。

これらのベンダーはすべて複数のFPGAファミリを提供しています。SoC FPGAを提供するベンダーや、人工知能(AI)および機械学習(ML)アプリケーション向けにデバイスを提供するベンダー、宇宙で使用される放射線耐性デバイスを提供するベンダーもあります。それぞれ異なるリソースを提供する多くのファミリが存在するため、作業に最適なデバイスをすぐに選択するのは難しい場合があります。

Intel FPGAおよびSoC FPGAの紹介

Intelが提供するプログラム可能デバイス製品の性能および機能は、標準的なものから極めて高いものまで、従来型のFPGAからSoC FPGA(1つまたは複数のセキュリティ強化されたプロセッサコアを備えたFPGAプログラム可能ファブリック)まで多岐にわたります。

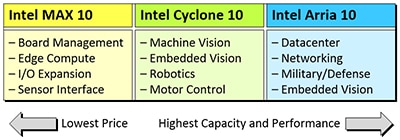

Intelは、現行の製品ポートフォリオにMax 10、Cyclone 10、およびArria 10(図2)など、5種類のFPGAファミリを用意しています。また、非常に高性能のStratix 10、そして最新かつ最先端のAgilexも提供しています。

図2:Intelの5つのFPGAファミリのうち、3つ(最も価格の安い(Max 10)ものから最も性能およびパフォーマンスが高い(Arria 10)まで)が対象としている用途および市場(基板管理およびI/O拡張から組み込みビジョンおよび軍事/防衛まで)。Stratix 10および新しいAgilexデバイスはパフォーマンスがさらに強化されている(画像提供:クリーブ・"マックス"・マックスフィールド氏)

図2:Intelの5つのFPGAファミリのうち、3つ(最も価格の安い(Max 10)ものから最も性能およびパフォーマンスが高い(Arria 10)まで)が対象としている用途および市場(基板管理およびI/O拡張から組み込みビジョンおよび軍事/防衛まで)。Stratix 10および新しいAgilexデバイスはパフォーマンスがさらに強化されている(画像提供:クリーブ・"マックス"・マックスフィールド氏)

Intel Max 10 FPGAには、FPGAの構成を保持するオンチップNORフラッシュメモリが組み込まれています。別の製品ファミリはSRAMベースの構成セルを備えており、電源投入時にオンボードの外部メモリやシステム内の他の場所から(外部プロセッサの制御下など)構成を読み込みます。MAX 10ファミリを除くすべてのIntel FPGAファミリは、統合化され、セキュリティ強化されたマイクロプロセッサシステムとともにFPGAまたはSoC FPGAとして利用できます。

MAX 10 FPGAの統合化された機能には、A/Dコンバータ(ADC)および単体のチップに2つのイメージを保存し、それらのイメージ間で動的に切り替えることができるデュアル構成フラッシュなどがあります。また、Nios IIソフトコア組み込みプロセッサのサポート、DSPブロック、およびソフトDDR3メモリコントローラなどもMAX 10 FPGAの特色です。

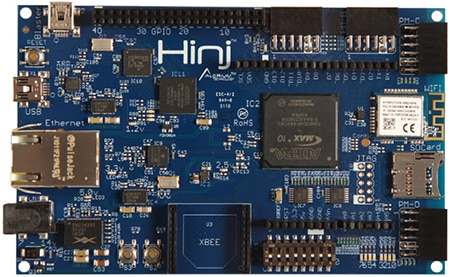

MAX 10ポートフォリオの代表的なデバイスは、論理素子/セル数16,000、総RAMビット562,176、および入力/出力(I/O)数130の10M16SCU169I7Pです。MAX 10に最適な評価ボードはEK-10M08E144です。もう1つは、Alorium Technology, LLCのFPGA IoTセンサハブキットであるHINJKIT(図3)です。HINJKITの非常に興味深い点は、そのMAX 10 FPGAにAlorium TechnologyのAVR対応8ビットマイクロコントローラが組み込まれているため、Arduino IDEとともに使用できることです。このボードは、サードパーティのIoTキャリヤボード、モジュール、アクセサリとの非常に柔軟な連携を実現します。

図3:HINJKITはAloriumのMAX 10 FPGA開発プラットフォームで、サードパーティのIoTキャリヤボード、モジュール、アクセサリとの非常に柔軟な連携を実現。(画像提供:Alorium Technology)

図3:HINJKITはAloriumのMAX 10 FPGA開発プラットフォームで、サードパーティのIoTキャリヤボード、モジュール、アクセサリとの非常に柔軟な連携を実現。(画像提供:Alorium Technology)

IntelのCyclone 10 GX FPGAは、12.5ギガバイト(Gbyte)のトランシーバベースの機能、1.4ギガビット/秒(Gbit/s)の低電圧差動信号(LVDS)、および最大1,866メガビット/秒(Mbit/s)のデータレートのための最大72ビット幅のDDR3 SDRAMインターフェースを備えています。Cyclone 10 GX FPGAは、マシンビジョン、ビデオ接続、スマートビジョンカメラなどの広帯域幅性能アプリケーション向けに最適化されています。

一方、Cyclone 10 LP FPGAは、I/O拡張、センサフュージョン、モータ/モーション制御、チップ対チップブリッジング、および制御などの低い静電力かつ低コストのアプリケーションに最適化されています。GXおよびLPデバイスファミリはどちらも垂直マイグレーションに対応しており、設計者はあるデバイスで設計を開始し、後から隣接する密度にマイグレーションできます。

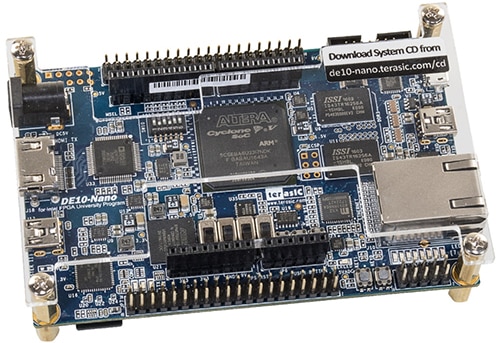

Cyclone 10ポートフォリオの代表的な製品は、論理素子/セル数6,272、総RAMビット276,480、および入力/出力(I/O)数176の10CL006YU256A7Gです。P0496 DE10-NANO Cyclone V SE SoCキット(図4)、P0553 TSoM Cyclone V SE評価ボード(この製品もCyclone V SoC FPGAを基盤としています)、およびP0581 TSoM Cyclone V SE FPGA評価ボード(いずれもTerasic Incの製品)など、さまざまな開発ボードおよび評価ボード、およびモジュールを利用することができます(これらのボードに搭載されているCyclone V FPGAは以前の世代のCyclone 10ファミリであることに注意してください)。

図4:低価格のP0496 DE10-NANO開発キットは堅牢なハードウェア設計プラットフォームで、この開発キットを利用することにより、ユーザーはCyclone FPGAに対する実験と評価を行うことができます。(画像提供:Terasic Inc.)

図4:低価格のP0496 DE10-NANO開発キットは堅牢なハードウェア設計プラットフォームで、この開発キットを利用することにより、ユーザーはCyclone FPGAに対する実験と評価を行うことができます。(画像提供:Terasic Inc.)

TSMCの20ナノメートル(nm)プロセステクノロジを基盤としているArria 10デバイスでは、デュアルコアのArm Cortex-A9 MPCoreハードプロセッサシステム(HPS)と、セキュリティ強化されている浮動小数点DSPブロックが使用されたプログラム可能ファブリックが組み合わされています。組み込みの高速トランシーバ、ハードメモリコントローラ、およびプロトコルインテレクチャルプロパティ(IP)コントローラが緊密に統合された1つのパッケージに含まれていることもArria 10デバイスの特性です。

Arria 10ポートフォリオの代表的なデバイスは、論理素子/セル数220,000、総RAMビット13,752,320、および入力/出力(I/O)数240の10AX022C4U19E3SGです。このFPGAを使用した開発に最適なのが、IntelのDK-DEV-10AX115S-A Arria 10 GX FPGA評価ボードです(図5)。このボードを使用することにより、開発者はArria 10をベースにしたPCI Express(PCIe)3.0の設計の開発およびテスト、DDR4、DDR3、QDR IV、およびRLDRAM IIIの各メモリで構成されたメモリサブシステムの開発およびテスト、そしてIntelのパートナーが提供するFMCメザニンカードと連携するFPGAメザニンカード(FMC)コネクタを使用した、モジュール式かつスケーラブルな設計の開発を行うことができます。

図5:DK-DEV-10AX115S-A Arria 10 GX FPGA開発キットは、包括的な設計環境を実現。この環境には、PCIeベースの設計、メモリサブシステム、FMCカードを基盤としたシステムの開発およびテストに必要な、あらゆるハードウェアおよびソフトウェアが搭載されています。(画像提供:Intel)

図5:DK-DEV-10AX115S-A Arria 10 GX FPGA開発キットは、包括的な設計環境を実現。この環境には、PCIeベースの設計、メモリサブシステム、FMCカードを基盤としたシステムの開発およびテストに必要な、あらゆるハードウェアおよびソフトウェアが搭載されています。(画像提供:Intel)

Intel Stratix 10 FPGAおよびSoC FPGAの特性は、Intel Hyperflex FPGAアーキテクチャが使用されていることです。このデバイス製品ラインで使用されているFPGAは、最大10 TFLOPSの浮動小数点性能および28.3Gbit/s(GX)~57.8Gbit/sをサポートするトランシーバ(5Gの通信、クラウドコンピューティング、ネットワーク仮想化、光伝送ネットワークの帯域幅の需要に対応するための、最大144のトランシーバレーン)を備えた、高スループットのシステムのニーズに対応します。機種の異なるものでは、毎秒16ギガ転送(GT/s)で最大x16構成のPCIe Gen4インターフェース、および一部のIntel Optane DCパーシステントメモリをサポートする新しいメモリコントローラが搭載されているのものもあります。

Stratix 10ラインを使用した開発をサポートするのが、IntelのDK-DEV-1SGX-L-A Stratix 10 GX FPGA評価ボード(図6)です。このボードを使用することにより、設計者はStratix 10をベースにしたPCI Express(PCIe)3.0の設計の開発およびテスト、DDR4、DDR3、QDR IV、およびRLDRAM IIIの各メモリで構成されたメモリサブシステムの開発およびテスト、そしてやはりIntelのパートナーが提供するFMCメザニンカードと連携するFPGAメザニンカード(FMC)コネクタを使用した、モジュール式かつスケーラブルな設計の開発を行うことができます。

図6:DK-DEV-1SGX-L-A Stratix 10 GX FPGA評価ボードは、包括的な設計環境を実現。この環境には、PCIeベースの設計、メモリサブシステム、FMCカードを基盤としたシステムの開発およびテストに必要な、あらゆるハードウェアおよびソフトウェアが搭載されています。(画像提供:Intel)

図6:DK-DEV-1SGX-L-A Stratix 10 GX FPGA評価ボードは、包括的な設計環境を実現。この環境には、PCIeベースの設計、メモリサブシステム、FMCカードを基盤としたシステムの開発およびテストに必要な、あらゆるハードウェアおよびソフトウェアが搭載されています。(画像提供:Intel)

IntelのFPGAおよびSoC FPGAを使用した設計および開発

FPGAに関する本シリーズの第1部では、このようなデバイスを設計する従来の方法は、エンジニアがVerilogやVHDLなどのハードウェア記述言語(HDL)を使用して、レジスタ転送レベル(RTL)と呼ばれる抽象化レベルで設計意図を取り込む方法であると述べました。このRTL記述は、最初に必要に応じて動作をシミュレーションで検証します。次に合成ツールがその記述を引き継ぎ、FPGAの構成(プログラミング)に使用する構成ファイルを生成します。

抽象化の次のステップでは、C/C++などのプログラミング言語を使用するか、またはSystemC(イベント駆動型シミュレーションインターフェースを可能にするC++のクラスおよびマクロのセット)などの特別な実装により、設計の意図を取り込みます。これらは、それぞれプレーンC++構文を使用して記述された並行プロセスのシミュレーションを容易にします。このような記述は、通常のプログラムのように実行することで分析してプロファイルし、次にハイレベル合成(HLS)エンジンに渡してRTLを出力し、それを通常の合成エンジンに供給することができます。

概念においてさらにハイレベルの抽象化はOpen CL(Open Computing Language)です。Open CLは、異種プラットフォームで実行されるプログラムを記述するためのフレームワークです。FPGAに加えて、これらのプラットフォームには中央処理装置(CPU)、グラフィックス処理ユニット(GPU)、デジタル信号プロセッサ(DSP)、その他のプロセッサおよびハードウェアアクセラレータが組み込まれています。OpenCLは、これらのデバイスをプログラムするためのプログラミング言語(C99およびC++11に基づく)に加えて、プラットフォームを制御し、このコンピューティングデバイス上でプラットフォームを実行するためのアプリケーションプログラミングインターフェース(API)を指定します。

Intel FPGAおよびSoC FPGAの場合、ユーザーは、すべての製品ファミリを対象とした設計を、Intel Quartus Prime設計ソフトウェアを使用して開発します。このソフトウェアには、Quartus Primeプロエディション、Quartus Primeスタンダードエディション、Quartus Primeライトエディションの3つのバージョンが用意されています。プロおよびスタンダードエディションには有料のライセンスが必要ですが、ライトエディションは無料でダウンロードすることができます。

プロエディションは、Agilex、Stratix 10、Arria 10、およびCyclone 10 GXデバイスファミリ、そして次世代のFPGAおよびSoC FPGAの高度な機能をサポートするために最適化されており、スタンダードエディションはCyclone 10 LPデバイスファミリに加えて以前のデバイスファミリを広範にサポートします。また、無料でダウンロードすることができ、ライセンス不要のライトエディションは、量産デバイスファミリへのエントリポイントとしてご利用いただくのに最適です。

Intelは、Intel DSP Builder、Intel High Level Synthesis(HLS)コンパイラ、およびIntel FPGA SDK for OpenCLなど、他にも非常に多様な設計ツールやリソースを提供しています。

また、Intel Distribution of the OpenVINOツールキットも便利です。このツールキットを利用することで、開発者は人工知能(AI)、コンピュータビジョン、オーディオ、音声、および言語アプリケーションを作成し、エッジからクラウドに至るまでディープラーニングインターフェースを実現することができます。FPGAと同様に、このツールキットも、共通のAPIを利用して、IntelのアーキテクチャおよびAIアクセラレータ(CPU、iGPU、Intel Movidius Vision Processing Unit(VPU)、およびIntel Gaussian & Neural Accelerator(GNA))を対象とした異種間での実行に対応しています。このツールキットは、Cyclone V GT FPGAを基盤とするOpenVINOスターターキットによってサポートされています。

結論

プロセッサとFPGAの組み合わせ、FPGA単独、またはファブリックの一部としてハードプロセッサコアを強化するFPGAによって最適な処理ソリューションが実現されることがよくあります。FPGAは1つのテクノロジとしてここ数年で急速に進化しており、柔軟性、処理速度、および電力における多くの設計要件に対応し、インテリジェントインターフェースからマシンビジョンや人工知能まで幅広いアプリケーションに活用することができます。

Intelのプログラム可能なデバイス製品は、低域から超広域、従来型のFPGAからSoC FPGAと、非常に多様です。これらのデバイスを使用した設計を作成するために、Intelやその他のサードパーティは、ハードウェア開発者、ソフトウェア開発者、そして人工知能やコンピュータビジョンシステムのクリエーターのニーズに対応する、強力な開発キットおよびツールのスイートを提供しています。

参考情報

免責条項:このウェブサイト上で、さまざまな著者および/またはフォーラム参加者によって表明された意見、信念や視点は、DigiKeyの意見、信念および視点またはDigiKeyの公式な方針を必ずしも反映するものではありません。