FPGAの基礎 – 第1部:FPGAとは何か、なぜ必要なのか?

DigiKeyの北米担当編集者の提供

2019-11-14

RISC、CISC、グラフィックスプロセッサとFPGAの組み合わせ、FPGA単独、またはファブリックの一部としてハードプロセッサコアを強化するFPGAによって最適な処理ソリューションが得られることがよくあります。一方で、多くの設計者はFPGAの機能、その進化の過程や使い方をよく知りません。この記事は5部構成で、第1部ではFPGAの基礎について説明し、大手プロバイダが提供しているソリューション例を紹介します。第2部、第3部、第4部、第5部では、Lattice Semiconductor、Microchip、AlteraおよびXilinxが提供するFPGAデバイスファミリと設計ツールに焦点を当てます。

設計者は、すべてのアプリケーション要件に対応する最適なコンピューティングソリューションを提供するシステムの設計方法を常に模索しています。多くの場合、最適なソリューションにはフィールドプログラマブルゲートアレイ(FPGA)が必要ですが、多くの設計者はこれらのデバイスの機能や取り込み方法に関する知識を十分に持っていません。

この記事では、FPGAを活用できる設計シナリオについて簡単に説明します。次に、FPGA機能の基礎を説明し、興味深いFPGAソリューションと開発キットを紹介します。

FPGAを使用する理由

コンピューティングアプリケーションの範囲は幅広く、市販のマイクロプロセッサ(MPU)やマイクロコントローラ(MCU)、市販のグラフィックス処理ユニット(GPU)、FPGA、カスタムのシステムオンチップ(SoC)デバイスなど、対応できる最適なアプローチはそれぞれ異なります。どれを使うべきか判断するには、アプリケーション要件と考慮事項を綿密に確認していく必要があります。

たとえば、5G基地局のような最新のテクノロジを利用している場合、設計者はその基盤となる標準やプロトコルが進化し続けている点を考慮する必要があります。つまり、設計者は独自に管理できない仕様の変化に、すばやく効率的に対処できなければなりません。

同様に、システムが現場に導入された後に生じる標準やプロトコルの変更にも柔軟に対応する必要があります。また、システム機能の予期しないバグやシステムセキュリティの欠陥に対応したり、既存の機能を修正したり、システムの寿命を延ばすために新機能を追加できる能力も必要です。

通常、SoCで最高のパフォーマンスが実現されますが、この方法は高額で時間もかかります。さらに、チップのファブリックに実装されているアルゴリズムは基本的に「シリコンに固定」されています。この特有の柔軟性の欠如が、前述の考慮事項で問題となります。最適なパフォーマンスと柔軟性のスイートスポットを見つけるためには、他の方法が必要です。その方法は、FPGA、マイクロプロセッサ/マイクロコントローラとFPGAの組み合わせ、またはファブリックの一部としてハードプロセッサコアを強化するFPGAによって実現されることがよくあります。

FPGAとは何か?

利用者によってFPGAの用途が異なるため、この質問に簡単に答えることはできません。また、さまざまな種類のFPGAがあり、それぞれに異なる機能が組み合わされています。

FPGAの中心で、いわば「FPGAらしさ」を特徴づけているのは、プログラマブルファブリックです。これは、プログラマブル論理ブロックの配列として表されます(図1a)。これらの論理ブロックそれぞれに、ルックアップテーブル(LUT)、マルチプレクサ、レジスタなどの要素の集合が含まれています。これらはすべて必要に応じて機能するよう構成(プログラミング)できます(図2)。

図1:プログラマブルファブリックと構成可能なGPIOのみ含まれる最も簡易なFPGA(a)、基盤のファブリックをSRAMブロック、PLL、クロックマネージャで拡張する各種アーキテクチャ(b)、DSPブロックとSERDESインターフェース(c)、およびハードプロセッサコアと周辺機器(d)。(画像提供:Clive "Max" Maxfield氏)

図1:プログラマブルファブリックと構成可能なGPIOのみ含まれる最も簡易なFPGA(a)、基盤のファブリックをSRAMブロック、PLL、クロックマネージャで拡張する各種アーキテクチャ(b)、DSPブロックとSERDESインターフェース(c)、およびハードプロセッサコアと周辺機器(d)。(画像提供:Clive "Max" Maxfield氏)

図2:これらの論理ブロックそれぞれに、ルックアップテーブル(LUT)、マルチプレクサ、レジスタなどの要素の集合が含まれています。これらはすべて必要に応じて機能するよう構成(プログラミング)できます。(画像提供:Clive "Max" Maxfield氏)

図2:これらの論理ブロックそれぞれに、ルックアップテーブル(LUT)、マルチプレクサ、レジスタなどの要素の集合が含まれています。これらはすべて必要に応じて機能するよう構成(プログラミング)できます。(画像提供:Clive "Max" Maxfield氏)

多くのFPGAは、4入力論理関数を実装できる4入力LUTを使用しています。一部のアプリケーションで採用されている幅広いデータパスをより適切にサポートするために、6、7、または8入力のLUTを提供するFPGAもあります。LUTからの出力は直接、論理ブロック出力と、マルチプレクサ入力のいずれかに接続されています。マルチプレクサへの他の入力は論理ブロック入力に直接接続されています(e)。マルチプレクサを構成してこれらの入力のいずれかを選択できます。

マルチプレクサからの出力はレジスタ入力を供給します。エッジトリガフリップフロップまたはレベルセンシティブラッチ(この場合でも、FPGA内でラッチとして非同期ロジックを使用することは推奨されません)として機能するように各レジスタを構成できます。各レジスタのクロック(またはイネーブル)をアクティブハイまたはアクティブロウに設定できます。同様に、セット/リセット入力のアクティブレベルも設定できます。

これらの論理ブロックは、「プログラマブル相互接続の海」に浮かぶ「プログラマブルロジックの島」と考えることができます。相互接続を構成して、任意の論理ブロックからの出力を他の論理ブロックの入力に接続できます。同様に、FPGAのプライマリ入力を任意の論理ブロックの入力に接続し、任意の論理ブロックからの出力を使用してデバイスからプライマリ出力を駆動できます。

プライマリ汎用入出力(GPIO)に関して、これらはバンク(グループ)で表されます。各バンクは異なるインターフェース標準(LVCMOS、LVDS、LVTTL、HSTL、SSTLなど)をサポートするように構成できます。さらに、入力のインピーダンスを出力のスルーレートとして構成することもできます。

次のFPGAファブリックの拡張には、ブロックRAM(BRAM)と呼ばれるSRAMのブロック、位相ロックループ(PLL)、クロックマネージャなどが含まれています(図1b)。デジタル信号処理(DSP)ブロック(DSPスライス)も追加できます。これらには、構成可能なマルチプレクサと、積和演算(MAC)演算を実行できる構成可能な加算器が含まれています(図1c)。

もう1つの一般的なFPGA機能である高速SERDESブロックは、ギガビットシリアルインターフェースをサポートできます。すべてのFPGAが前述の機能をすべてサポートしているわけではないことに注意してください。各FPGAが提供する機能は、対象となる市場やアプリケーションに応じて異なります。

FPGAのプログラマブルファブリックを使用して、任意の論理関数や必要な関数の集合、プロセッサコア、または複数のコアも実装することができます。これらのコアがプログラマブルファブリックに実装されている場合は、「ソフトコア」と呼ばれます。それに対し、一般的にSoC FPGAと呼ばれるFPGAには、1つ以上の「ハードコア」プロセッサが含まれます。これらのプロセッサはシリコンに直接実装されます(図1d)。これらのハードプロセッサコアには浮動小数点ユニット(FPU)とL1/L2キャッシュが含まれる場合があります。

同様に、CAN、I2C、SPI、UART、USBなどのペリフェラルインターフェース機能はプログラマブルファブリックにソフトコアとして実装できますが、多くのFPGAではハードコアとしてシリコンに組み込まれています。通常、プロセッサコア、インターフェース機能、プログラマブルファブリック間の通信は、AMBAやAXIなどの高速バスを使って行われます。

1985年にXilinxから販売されたFPGAには、8 x 8配列のプログラマブル論理ブロックのみが(RAMブロック、DSPブロックなどはない)含まれていました。それに比べ、現在の高速FPGAには数十万の論理ブロック、数千のDSPブロック、および数メガビットのRAMを含めることができます。合計すると、数千万のゲート(2入力NANDゲート)に該当する数十億のトランジスタが含まれる場合があります。

代替構成テクノロジ

論理ブロックの機能および相互接続のルーティングは、構成セルによって決まります。構成セルは0/1(オフ/オン)スイッチとして視覚化できます。これらのセルは、GPIOインターフェース標準、入力インピーダンス、出力スルーレートなどの構成にも使用できます。FPGAに応じて、これらの構成セルは次の3つのテクノロジのいずれかを使用して実装できます。

- アンチヒューズ:これらの構成セルはOne-Time Programmable(OTP)です。つまり、デバイスを一度プログラミングしたら、元に戻せません。これらのデバイスは、宇宙および高度なセキュリティアプリケーションに限定される傾向があります。これらのデバイスの販売量は少量であるため、価格は高く、高額な設計オプションです。

- フラッシュ:アンチヒューズベースの構成セルと同様に、フラッシュベースのセルも不揮発性です。アンチヒューズセルとは異なり、フラッシュセルは必要に応じて再プログラミングできます。フラッシュ構成セルは放射線耐性であるため、これらのデバイスは宇宙アプリケーションに適しています(上位のメタライゼーション層とパッケージの変更が必要)。

- SRAM:この場合、構成データは外部メモリに保存され、FPGAの電源が入るたびに(または動的構成シナリオの場合は推奨として)読み込まれます。

構成セルがアンチヒューズまたはフラッシュのFPGAには、「瞬時オン」であること、および消費電力が少ないという利点があります。このテクノロジの欠点は、チップの他の部分の作成に使用される基本のCMOSプロセスに加えて、追加の処理ステップが必要になることです。

構成セルがSRAMテクノロジに基づいているFPGAは、チップの他の部分と同じCMOSプロセスを使用して作成されており、通常はアンチヒューズとフラッシュテクノロジよりも1世代または2世代進んでいるため、他よりもパフォーマンスが優れているという利点があります。SRAM構成セルの主な欠点は、(同じテクノロジノードで)アンチヒューズやフラッシュよりも多くの電力を消費すること、および放射線によって生じるSingle Event Upset(SEU)の影響を受けやすいことです。

SEUの影響を受けやすいSRAMベースのFPGAは、長い間、航空および宇宙アプリケーションには適していないとみなされてきました。最近、特殊な移行戦略が採用され、その結果、SRAMベースのFPGAは、フラッシュベースのFPGAと並行して、Mars Curiosity Roverなどのシステムに使用されるようになりました。

FPGAの使用による柔軟性の実現

FPGAは、さまざまなアプリケーションに使用されます。特に、インテリジェントインターフェーシング機能、モータ制御、アルゴリズムのアクセラレーションと高性能コンピューティング(HPC)、画像とビデオの処理、マシンビジョン、人工知能(AI)、機械学習(ML)、ディープラーニング(DL)、レーダ、ビーム形成、基地局、通信の実装に活用できます。

たとえば、簡単な例として、異なるインターフェース標準または通信プロトコルを使用する他のデバイス間にインテリジェントインターフェースを提供できます。レガシーインターフェースを使用してカメラセンサとディスプレイデバイスに接続されているアプリケーションプロセッサを含む既存のシステムについて考えてみます(図3a)。

図3:FPGAを使用して、別のインターフェース標準または通信プロトコルを使用する他のデバイス間にインテリジェントインターフェースを提供し、レガシーデバイスに基づいて既存の設計の寿命を延ばすことができます。(画像提供:Clive "Max" Maxfield氏)

図3:FPGAを使用して、別のインターフェース標準または通信プロトコルを使用する他のデバイス間にインテリジェントインターフェースを提供し、レガシーデバイスに基づいて既存の設計の寿命を延ばすことができます。(画像提供:Clive "Max" Maxfield氏)

システムの作成者がカメラセンサとディスプレイデバイスを、軽量で、価格が安く、省電力の最新機器にアップグレードしたいと考えているとします。唯一の問題は、これらの新しいペリフェラルのどちらかまたは両方が、元のアプリケーションプロセッサ(AP)でサポートされていない最新のインターフェース標準を使用している可能性があることです。または、Mobile Industry Processor Interface(MIPI)のような完全に異なる通信プロトコルをサポートしている可能性があります。この例では、複数のI/O標準をサポートできるFPGAと、ソフトMIPI IPコアを組み合わせて使用して、高速、低コスト、リスクのないアップグレードパスを実現しています(図3b)。

もう1つの応用例として、レーダシステムや通信基地局などの実装に必要な信号処理の実行のように計算量の多いタスクを取り上げます。ノイマン型アーキテクチャまたはハーバードアーキテクチャを使用する従来のプロセッサは、特定のタスクには適していますが、同じ動作のシーケンスを繰り返し実行する必要のあるタスクには適していません。これは、シングルスレッドを実行する信号プロセッサコアが一度に1つの命令しか実行できないことが原因です(図4a)。

図4:一度に1つの命令のみ順番に実行するマイクロプロセッサとは異なり、FPGAの複数の機能ブロックは同時に実行できます。また、FPGAは超並列方式で適切なアルゴリズムを実行できます。(画像提供:Clive "Max" Maxfield氏)

図4:一度に1つの命令のみ順番に実行するマイクロプロセッサとは異なり、FPGAの複数の機能ブロックは同時に実行できます。また、FPGAは超並列方式で適切なアルゴリズムを実行できます。(画像提供:Clive "Max" Maxfield氏)

それに対し、FPGAは複数の機能を同時に実行できるため、一連の動作をパイプライン化することができ、それによりスループットが大幅に向上します。同様に、プロセッサでデータ値の1,000個のペアを1,000回追加するなど、同じ動作を実行するのではなく、プログラマブルファブリックで1,000の加算器をインスタンス化することで、FPGAの単一のクロックサイクルで同じ計算を超並列に実行することができます(図4b)。

FPGAの製造業者

製造業者の状況は変化し続けています。最大容量と最高性能を備えたハイエンドデバイスの主要製造業者は、Intel(Alteraを買収)とXilinxの2社です。

IntelとXilinxの製品は、ローエンドのFPGAからハイエンドのSoC FPGAまで多岐にわたっています。ほぼFPGAのみに特化しているもう1社のベンダがLattice Semiconductorで、小規模または中規模のアプリケーションを対象にしています。最後に紹介するMicrochip Technology(Actel、Atmel、およびMicrosemiを買収)は、中小規模の複数のFPGAファミリとSoC FPGAカテゴリのローエンドメンバーを扱っています。

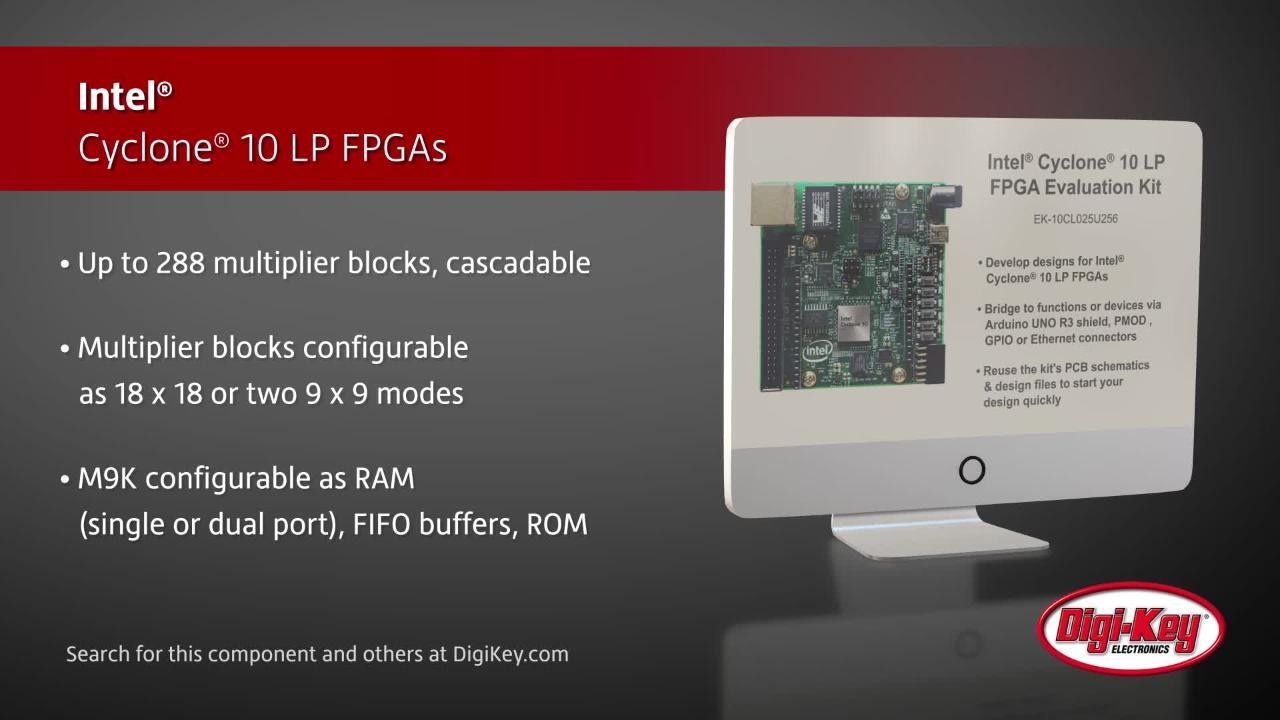

それぞれリソース、性能、容量、パッケージングスタイルが異なる、非常に多くのファミリがあるため、実行しているタスクに最適なデバイスを選択するのが難しい場合があります。以下の例を参考にしてください。Intelのデバイス、 Lattice Semiconductorのデバイス、およびXilinxのデバイス。

FPGAを使った設計方法

従来、FPGAでは、エンジニアはVerilogやVHDLなどのハードウェア記述言語を使用して設計の意図を表してきました。これらの記述は、必要に応じて動作するか検証するためにシミュレーションされた後、FPGAを構成(プログラミング)するのに使用される構成ファイルを生成する合成ツールに渡されます。

各FPGAベンダは独自にツールチェーンを開発しているか、専門のベンダが提供しているツールのカスタマイズバージョンを提供しています。どちらの場合も、FPGAベンダのウェブサイトからツールにアクセスできます。また、完全な機能を備えたツールスイートの無料または低コストバージョンも利用できる場合があります。

ソフトウェア開発者にとってFPGAが利用しやすくなるように、高位合成(HLS)ツールを提供しているベンダもあります。これらのツールは、C、C++、またはOpenCLの高い抽象度でキャプチャされた必要な動作のアルゴリズム的記述を解釈します。

初心者の設計者向けに、さまざまな機能を備えた開発および評価ボードが多数提供されています。たとえば、XilinxのZynq-7000 SoC FPGAが搭載された、DFRobotのDFR0600開発キット、IntelのCyclone V SoC FPGAが搭載されたTerasic IncのDE10 Nano、およびLattice Semiconductorの低電力iCE40 FPGA が搭載されたICE40HX1K-STICK-EVN評価ボードがあります。

FPGAベースのPCIeドーターカードを使用してX86マザーボードで実行されているアプリケーションを迅速化する計画がある設計者は、XilinxのAlveo PCIeドーターカードのような製品も視野に入れることができます。

まとめ

FPGA、プロセッサとFPGAの組み合わせ、またはファブリックの一部としてハードプロセッサコアを強化するFPGAによって最適な設計ソリューションが得られることがよくあります。

FPGAはここ数年で急速に進化しており、柔軟性、処理速度、および電力における多くの設計要件に対応し、幅広いアプリケーションに活用することができます。

免責条項:このウェブサイト上で、さまざまな著者および/またはフォーラム参加者によって表明された意見、信念や視点は、DigiKeyの意見、信念および視点またはDigiKeyの公式な方針を必ずしも反映するものではありません。