リソースに制約のあるアプリケーションでのFPGAの使用方法

DigiKeyの北米担当編集者の提供

2025-05-07

リソースに制約のある組み込みシステムでは、構成可能なロジックのニーズが、全体で高まっています。エッジAI、マシンビジョン、産業用オートメーションなどのアプリケーションでは、厳しい電力、サイズ、コストの制約の中で、進化する性能の要求に対応するための、柔軟でアプリケーションに特化したロジックが必要です。最新のフィールドプログラマブルゲートアレイ(FPGA)は、これらの相反する要求に対応できます。

この記事では、リソースに制約のあるアプリケーション向けにFPGAを選択する際の主要な考慮すべき設計基準について説明します。次に、 Alteraの電力とコスト最適化FPGAの製品ラインアップを例に、さまざまな製品ラインが特定のシナリオにどのように適合するかを説明します。最後に、設計コンセプトの試作と検証に使用できる開発キットと評価ボードを紹介します。

FPGAを選択する際の考慮事項

リソースに制約のあるシステムにFPGAを選択する際には、複数の設計要件を検討し、それらを適切なソリューションに適合させる必要があります。FPGAを選択する際には、以下の主要な特性を考慮する必要があります。

ロジックエレメント(LE)の容量:FPGAの基本的な構成要素であるLEの数は、実装可能なカスタムロジックの量を決定します。LEの数が多いほど、より複雑な設計が可能になりますが、その代償として電力、コスト、パッケージサイズが増加します。

I/Oとメモリ:FPGAは、システム内の異なるコンポーネントを接続するために使用されるため、I/Oピンの数は重要な考慮事項となります。I/O性能を向上させるため、多くのFPGAは、PCI Express(PCIe)、高速メモリ、マルチギガビットトランシーバなどのインターフェース用にハード化された専用ロジックブロックを組み込んでいます。

さらに、一部のFPGAには、A/Dコンバータ(ADC)やフラッシュメモリなどの機能が統合されています。これらの機能強化により、コンパニオンチップの必要性が減り、基板スペースの節約と電力効率の向上を実現できます。

プロセッサの統合:外部プロセッサの代わりに、FPGA内に「ソフト」マイクロプロセッサユニット(MPU)を実装できます。このアプローチは、システムのフットプリントを削減できますが、MPUの負荷が低いアプリケーションに最も適しています。

より高速で効率的なMPUを必要とするアプリケーションでは、FPGA内にMPUを専用ロジックブロックとして実装するハードプロセッサシステム(HPS)を備えたFPGAを検討することができます。

ハードウェアアクセラレータ: FPGAには通常、モーション制御などの演算負荷の高いタスクを効率的に処理する専用のデジタル信号処理(DSP)ブロックが搭載されています。よりハイエンドのデバイスには、AIワークロード向けの専用テンソルブロックが搭載されている場合があります。これらのアクセラレータブロックの機能はFPGAファミリによって大きく異なり、システム全体の性能に劇的な影響を与える可能性があります。

パッケージおよび消費電力の最適化:一部のFPGAは、物理的および電気的なフットプリントを最小限に抑えるよう特別に設計されています。たとえば、低消費電力のスリープモードが搭載されている場合があります。

ツール:カスタムロジックの作成は、特に経験の浅い設計者にとっては、困難な挑戦となる可能性があります。AlteraのQuartus PrimeDesign Softwareのようなツールが、このプロセスを合理化するために登場しました。

FPGA設計をより身近なものにするために設計されたQuartus Primeは、開発者向けの使いやすい操作性、豊富なビルド済みロジックブロックのカタログ、およびこれらのロジックブロックを自動的に相互接続する機能を提供します。このツールは、一般的なAIや機械学習(ML)のワークフローと統合されており、開発者はLinuxやZephyrのような一般的なオペレーティングシステム(OS)をFPGA上に展開することができます。

このような機能はFPGA設計を大幅に加速させるため、デバイスを選択する際にはツールの機能が重要な考慮事項となります。

高度な組み込みワークロード向けの高性能コンピューティング

設計要件がFPGAの選択にどのような影響を与えるかを説明するのに、まず、卓越した演算密度、帯域幅、統合性を必要とするハイエンドのアプリケーションから始めるのが適切です。たとえば、高度なエッジAIアプリケーションや高性能な産業用ゲートウェイなどが挙げられます。

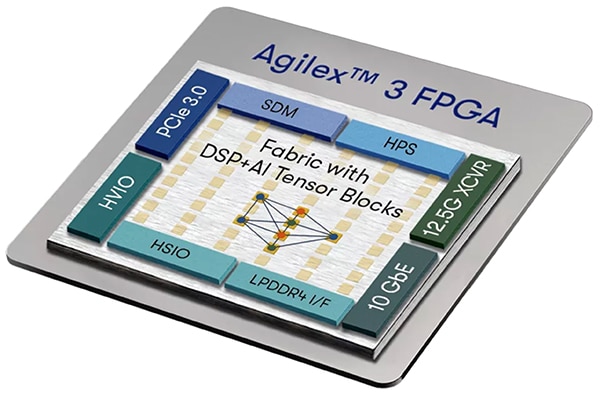

Agilex 3 FPGA(図1)は、このようなアプリケーションの要求を満たすように設計されており、最大135K LEを提供します。このチップは、FPGAのみとシステムオンチップ(SoC)の両方のバリエーションで提供されています。このSoCデバイスは、デュアルコアの800メガヘルツ(MHz)Arm®Cortex®-A55を搭載しており、FPGAがヒューマンマシンインターフェース(HMI)やネットワークスタックのような複雑なソフトウェアスタックを処理できるようにします。

このプログラマブルファブリックには、毎秒最大2.8INT8テラオペレーション/秒(TOPS)で実行できるAIテンソルブロックが搭載されています。これらのブロックは、FP16、FP19、FP32、BFLOAT16を含むさまざまな計算フォーマットをサポートし、AIワークロードの効率的な実行のために最適化されています。可変精度DSPブロックも搭載され、汎用信号処理用に最大180(GFLOPS)の浮動小数点演算性能を実現します。

図1:Agilex 3は高性能DSPとAIテンソルブロックを搭載していることが特徴です。(画像提供:Altera)

図1:Agilex 3は高性能DSPとAIテンソルブロックを搭載していることが特徴です。(画像提供:Altera)

高速コネクティビティもAgilex 3アーキテクチャの強みです。トランシーバは最大12.5ギガビット/秒(Gbits/s)のデータレートをサポートし、PCIe3.0、10ギガビットEthernet(GbE)、LPDDR4メモリインタフェース用のハードウェア化されたI/Oブロックが利用可能です。IEEE1588の高精度時刻同期のサポートにより、リアルタイム産業用ネットワークへの適性がさらに向上しています。

A3CZ135BB18AE7Sデバイスは、このファミリの機能を示しています。135KのLE、184のDSPブロックを搭載し、2.54TOPSを実現します。

複雑なシステムのための高度な統合

産業用オートメーションやミッドレンジビジョンシステムなどのアプリケーションでは、生の計算処理能力よりも、大量のカスタムロジックやI/Oを備えた複雑な構成をサポートする能力の方が重要になる場合があります。Cyclone VFPGAは、このようなシナリオに適しており、最大300K LEと広範な高速インタフェースを備えています。Agilex 3と同様に、これらのチップにはFPGAのみとSoCのバリエーションがあります。この場合、SoCデバイスはデュアルコアのArm Cortex-A9を実装しています。

これらのチップのプログラマブルファブリックには、9 × 9の3倍および18 × 18の2倍の固定小数点乗算、27 × 27の固定小数点または浮動小数点乗算をサポートする可変精度DSPブロックが実装されています。これらのブロックは、高度な信号処理やAIに使用することができます。

I/Oの幅広い組み合わせは、複数の電圧レベルとインターフェースタイプをサポートします。強化されたロジックブロックは、PCIe2.0、DDR3コントローラ、最大6.144Gbits/sで動作するトランシーバなど、高度な高速接続を可能にします。

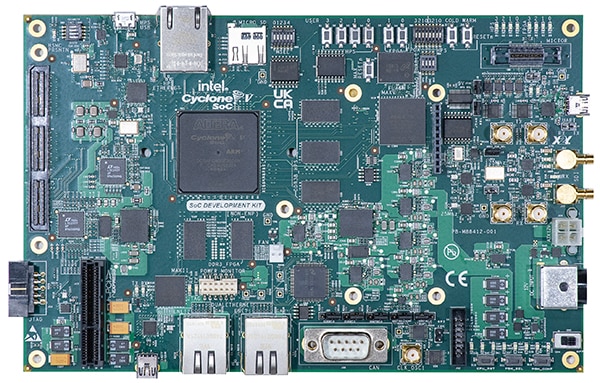

開発者は、DK-DEV-5CSXC6N-B開発キットを使用してCyclone V SoCファミリを評価できます(図2)。このキットは、複雑な高スループットシステムの迅速な試作用に設計されています。

図2:DK-DEV-5CSXC6N-B Cyclone V開発キットは、高性能な試作をサポートします。(画像提供:Altera)

図2:DK-DEV-5CSXC6N-B Cyclone V開発キットは、高性能な試作をサポートします。(画像提供:Altera)

このキットにはいくつかの特筆すべき機能があります。

- デュアルEthernetポート、PCIe x4コネクタ、高速メザニンカード(HSMC)(各方向16 LVDSチャネル)

- USB 2.0 OTG、CAN、UART、2行テキストLCDインターフェース

- FPGA側とHPS側にそれぞれ1ギガバイト(Gバイト)のDDR3 SDRAM、128メガバイト(Mバイト)のクアッドSPIフラッシュ、4GバイトのmicroSDカード

このボードには、600MHzで動作するデュアルコアArm Cortex-A9プロセッサ、85K LE、87個のDSPブロック、288本のI/Oピンを31mm × 31mmの896-FBGAパッケージに集積した5CSXFC5D6F31C8Nデバイスが搭載されています。

小型パッケージで電力効率に優れた構成可能なロジック

スペースと消費電力に関する厳しい制約が、多くのアプリケーションを制限しています。たとえば、センサインターフェース、電源シーケンス、周辺機器制御などがあります。MAX 10ファミリのようなFPGAは、このような場合に効果的なソリューションを提供します。MAX 10デバイスは、2Kから50K LEまでの構成と、3mm × 3mmという小型パッケージで提供されます。

主な機能には、最大2個の内蔵12ビットADC、DDR3メモリインターフェース、18 × 18およびデュアル9 × 9固定小数点モードをサポートする乗算器ブロックなどがあります。デュアルイメージストレージをサポートするオンチップフラッシュにより、外部メモリデバイスを使用せずに設定できます。

省電力機能は、MAX 10ファミリの最も特徴的な特性の1つです。内蔵スリープモードにより、動的消費電力を最大95%まで削減できます。オンチップフラッシュのおかげで、デバイスは完全に電源を切ってから10ミリ秒(ms)未満で動作を再開することもできます。

単一電源オプションにより、電源供給がさらに簡素化されます。これにより、MAX 10デバイスは、電源部がシステムの他の部分より先にオン状態になる必要がある監視の役割に特に適しています。

MAX 10 に関心のある開発者は、EK-10M08E144MAX 10 FPGA評価ボード(図 3)を使用してファミリを評価できます。このボードは、ArduinoUNO R3コネクタとテストポイントを介して外部信号にアクセスでき、ADC機能と全体的な電源動作の測定をサポートするように設計されたレイアウトを備えています。

図3:EK-10M08E144 MAX 10 FPGA評価ボードは、主要なI/Oに簡単にアクセスできます。(画像提供:Altera)

図3:EK-10M08E144 MAX 10 FPGA評価ボードは、主要なI/Oに簡単にアクセスできます。(画像提供:Altera)

このボードには、144ピンのLQFPパッケージに8K LEとシングルADCを内蔵した10M08SAE144C8Gデバイスを搭載しています。内蔵ハードウェアリソースに加え、このFPGAはRISC-VベースのNios Vソフトプロセッサをサポートしているため、設計者は外付けのマイクロコントローラユニット(MCU)無しで軽量の制御機能を実装できます。

ミッドレンジアプリケーション向けのバランスの取れた性能

アプリケーションによっては、エントリーレベルのFPGAが対応可能なロジックとI/O容量では不足する場合があります。たとえば、センサフュージョン、モーションコントロール、チップ間ブリッジングなどがあります。Cyclone 10 LPFPGAは、コスト重視のアプリケーションで電力と帯域幅のバランスをとるために最適化されたデバイスで、最大120KのLEと525のI/Oピンを提供することにより、これらの要件に対応します。

MAX 10と同様に、このファミリには、フィルタリング、制御ループ、基本的なAI推論などのワークロードに適したDSPブロックが含まれています。MAX 10とは異なり、Cyclone 10 LPデバイスは真のLVDSトランシーバとオンチップターミネーション(OCT)を内蔵し、高速デジタルインターフェースをサポートします。

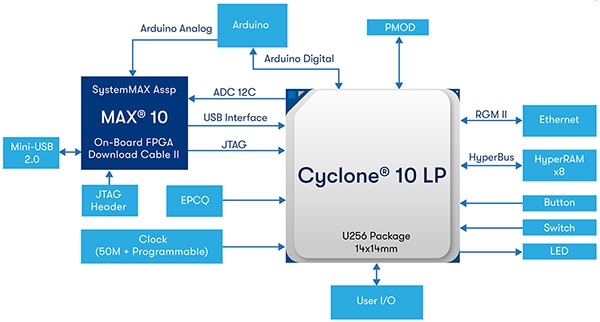

Cyclone 10 LPに関心のある開発者は、EK-10CL025U256Cyclone 10評価キットを使用して、このファミリを評価できます(図4)。このボードにはArduino UNO R3とDigilent Pmodコネクタがあり、簡単に拡張できます。その他の機能には、GbE、USB 2.0、128メガビット(Mbits)のSDRAM、64Mbitsのフラッシュメモリがあります。

図4:EK-10CL025U256 Cyclone 10評価キットは、周辺モジュールの拡張を容易にサポートします。(画像提供:Altera)

図4:EK-10CL025U256 Cyclone 10評価キットは、周辺モジュールの拡張を容易にサポートします。(画像提供:Altera)

このボードは10CL025YU256C8Gデバイスを搭載しており、25K LE、66個のDSPブロック、150本のI/Oピンが14mm × 14mmパッケージに収められています。MAX 10と同様に、Cyclone 10 LPファミリはNios Vソフトプロセッサをサポートしています。

まとめ

設計者は、組み込みシステムにカスタムロジックを実装する際に、これまで以上に柔軟に対応できるようになりました。高性能アプリケーションには、AIアクセラレータを統合したFPGAが有効です。低消費電力設計では、スリープモードを備えたデバイスを活用できます。I/O集約型システムは、ピン数が多い、高速インターフェースを備えたチップを活用できます。重要なのは、リソースに制約のある組み込みシステムの厳しい制約の中で、使いやすいキットを使ってこれらの機能をすべて実現できることです。

免責条項:このウェブサイト上で、さまざまな著者および/またはフォーラム参加者によって表明された意見、信念や視点は、DigiKeyの意見、信念および視点またはDigiKeyの公式な方針を必ずしも反映するものではありません。