FPGAの基礎 – パート4:Xilinx FPGA入門

DigiKeyの北米担当編集者の提供

2020-04-01

編集者メモ:RISC、CISC、グラフィックスプロセッサとFPGAの組み合わせ、FPGA単独、またはファブリックの一部としてハードプロセッサコアを強化するFPGAによって最適な処理ソリューションが得られることがよくあります。しかし、多くの設計者はFPGAの機能、その発展の過程や使い方をよく知りません。 このシリーズのパート1では、FPGAを詳しく紹介しています。パート2では、Lattice SemiconductorのFPGA製品を取り上げました。パート3では、Microchip Technologyが(その子会社であるMicrosemi Corporationを通じて)提供しているFPGAデバイスファミリと設計ツールについて詳しく解説しました。今回のパート4では、Xilinxのコンポーネントとツールを紹介します。そしてパート5では、Alteraの製品について検討します。

第1部で説明したように、フィールドプログラム可能ゲートアレイ(FPGA)は、スタンドアロンでも異機種混在アーキテクチャでも使われる非常に貴重なコンピューティング資産となり得る多くの特性を備えています。しかし、設計者はFPGAの機能や、このようなデバイスを設計に組み込む方法を十分に理解していません。

この状況を解決するための1つの方法は、大手ベンダーが提供しているFPGAアーキテクチャとその関連ツールについて理解を深めることです。この記事では、Xilinxの製品ラインナップについて見ていきます。

高度なFPGAオプションの概要

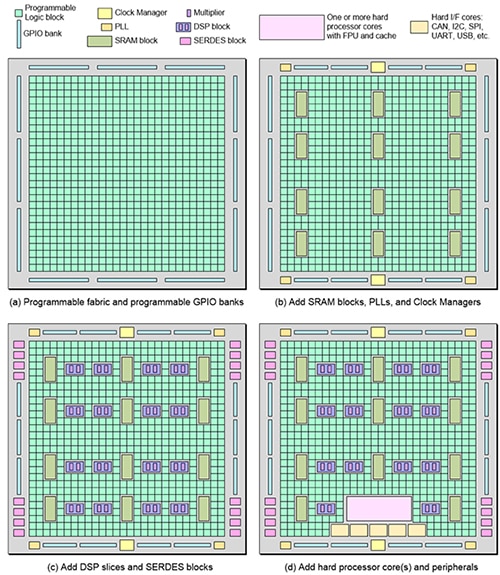

市場にはさまざまな種類のFPGAが出回り、それぞれに異なる機能が組み合わされています。FPGAの中心となるのがプログラム可能ファブリックです。これは、ロジックエレメント(LE)とも呼ばれるプログラム可能なロジックブロックの配列として表されます(図1a)。次のFPGAファブリックの拡張には、ブロックRAM(BRAM)と呼ばれるSRAMのブロック、位相ロックループ(PLL)、クロックマネージャなどが含まれています(図1b)。デジタル信号処理(DSP)ブロック(いわゆるDSPスライス)と高速シリアライザ/デシリアライザ(SERDES)ブロックを追加することもできます(図1c)。

図1:プログラム可能ファブリックと構成可能な汎用IO(GPIO)のみが含まれる最も簡易なFPGA(a)、基盤のファブリックをSRAMブロック、PLL、クロックマネージャで拡張する各種アーキテクチャ(b)、DSPブロックとSERDESインターフェース(c)、およびハードプロセッサコアと周辺機器(d)。(画像提供:クリーブ・"マックス"・マックスフィールド氏)

図1:プログラム可能ファブリックと構成可能な汎用IO(GPIO)のみが含まれる最も簡易なFPGA(a)、基盤のファブリックをSRAMブロック、PLL、クロックマネージャで拡張する各種アーキテクチャ(b)、DSPブロックとSERDESインターフェース(c)、およびハードプロセッサコアと周辺機器(d)。(画像提供:クリーブ・"マックス"・マックスフィールド氏)

CAN、I2C、SPI、UART、USBなどの周辺機器へのインターフェース機能はプログラム可能ファブリックにソフトコアとして実装できますが、多くのFPGAではハードコアとしてシリコンに組み込まれています。同様に、マイクロプロセッサをプログラム可能ファブリックにソフトコアとして、またはシリコンにハードコアとして実装できます(図1d)。ハードプロセッサコアを含むFPGAは、システムオンチップ(SoC)FPGAと呼ばれます。各FPGAが提供する機能、特長、性能、処理能力は、対象となる市場やアプリケーションに応じて異なります。

Altera(Intelが買収)、Atmel(Microchip Technologyが買収)、Efinix、Lattice Semiconductor、Microsemi(Microchip Technologyが買収)、Xilinxなど、多くのFPGAベンダーがあります。

これらのベンダーはすべて複数のFPGAファミリを提供しています。SoCのFPGAを提供するベンダーや、人工知能(AI)および機械学習(ML)アプリケーション向けにデバイスを提供するベンダー、宇宙などの高放射線環境を対象にした放射線耐性デバイスを提供するベンダーもあります。それぞれ異なるリソースを提供する多くのファミリが存在するため、作業に最適なデバイスをすぐに選択するのは難しい場合があります。

XilinxのFPGA、SoC、MPSoC、RFSoC、ACAPの導入

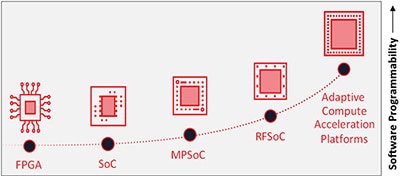

Xilinxが提供するプログラム可能なデバイスの性能および機能は、ベーシックなレベルから非常に高度なレベルにまで及びます。従来のFPGAから、SoC(シングルハードコアプロセッサを含むFPGAプログラム可能ファブリック)、MPSoC(複数ハードコアプロセッサを含むFPGAプログラム可能ファブリック)、RFSoC(RF機能を備えたMPSoC)、およびACAP(Adaptive Compute Acceleration Platform)まで幅広いタイプが含まれています(図2)。

図2:Xilinxのアーキテクチャポートフォリオは、プログラム可能ファブリックのみを含む単純なFPGAから、プログラム可能ファブリックがハードコアプロセッサで強化されたSoCデバイス、複数のハードコアプロセッサを含むMPSoC、RF機能を含むRFSoC、さらにAIなどのアプリケーション向けの最新世代ACAPへと徐々に発展してきています。(画像提供:クリーブ・"マックス"・マックスフィールド氏)

図2:Xilinxのアーキテクチャポートフォリオは、プログラム可能ファブリックのみを含む単純なFPGAから、プログラム可能ファブリックがハードコアプロセッサで強化されたSoCデバイス、複数のハードコアプロセッサを含むMPSoC、RF機能を含むRFSoC、さらにAIなどのアプリケーション向けの最新世代ACAPへと徐々に発展してきています。(画像提供:クリーブ・"マックス"・マックスフィールド氏)

Xilinxには幅広い製品ラインナップがあり、非常に多くの市場分野に対応しています。さらに幅広いデプロイメントメソッドも提供しており、FPGAの入門者には「全体像」が把握し難いほど多岐にわたります。

Xilinx製品が対象とする代表的な市場には、データセンター(計算処理、ネットワーク、ストレージ)、通信(有線、無線)、航空宇宙および防衛、産業・科学・医療(ISM)、試験・測定・エミュレーション(TME)、自動車・放送・一般消費者用などの分野があります。

デプロイメントメソッドには、XilinxがHardware Adaptable Device(ハードウェア適応デバイス)と名付けているメソッド(チップ、評価ボード、開発キットを含む)、Deployable End-System(展開可能エンドシステム)メソッド(システムオンモジュール(SoM)およびPCIeアクセラレータカードを含む)、FAAS(FPGAサービス)メソッド(Amazon Web Service(AWS)、Alibaba.com、Nimbix.netなどの主要クラウドプロバイダによるXilinx技術の評価/活用を含む)などがあります。

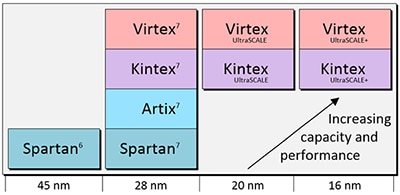

Xilinxが提供するFPGAについては、プロセス技術ノードにより分類できます(図3)。

図3:Xilinxが提供するFPGAには包括的なマルチノードポートフォリオがあり、幅広いアプリケーションの要件に対応します。(画像提供:クリーブ・"マックス"・マックスフィールド氏)

図3:Xilinxが提供するFPGAには包括的なマルチノードポートフォリオがあり、幅広いアプリケーションの要件に対応します。(画像提供:クリーブ・"マックス"・マックスフィールド氏)

目的のアプリケーションに応じて、低コストで小さなフットプリントのFPGAを初期のテクノロジノードで実装することを選ぶか、最先端のネットワーキングアプリケーションであれば、たとえば、高機能、高帯域幅、高性能のデバイスをより最新のテクノロジノードで実装することを選ぶこともできます。

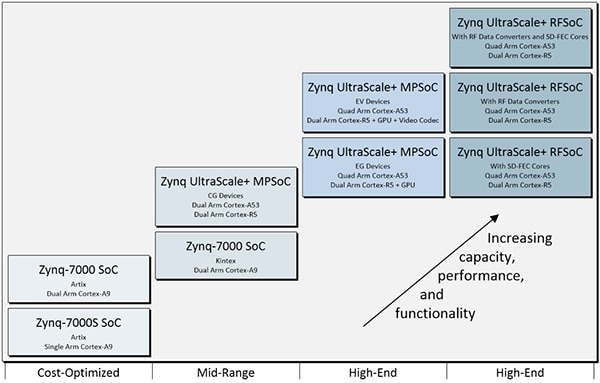

1つ以上のハードプロセッサコア(および他の高度な機能、たとえばGPU、コーデック、ソフト判定前方誤り訂正(SD-FEC)コアなど)を必要とする設計の場合、XilinxにはZynqファミリという製品ラインナップが対応します。Zynq SoC、MPSoC、およびRFSoC製品の概要を図4に示します。これらのソリューションによって得られる幅広い機能性により、設計者は、電力、性能、コスト、市場投入までの時間を最適化し易くなります。

図4:XilinxのSoC、MPSoC、およびRFSoC製品 は、プロセッサのソフトウェアプログラム可能性とFPGAのハードウェアプログラム可能性を統合し、設計者にシステムの性能、柔軟性、拡張性をもたらします。(画像提供:クリーブ・"マックス"・マックスフィールド氏)

図4:XilinxのSoC、MPSoC、およびRFSoC製品 は、プロセッサのソフトウェアプログラム可能性とFPGAのハードウェアプログラム可能性を統合し、設計者にシステムの性能、柔軟性、拡張性をもたらします。(画像提供:クリーブ・"マックス"・マックスフィールド氏)

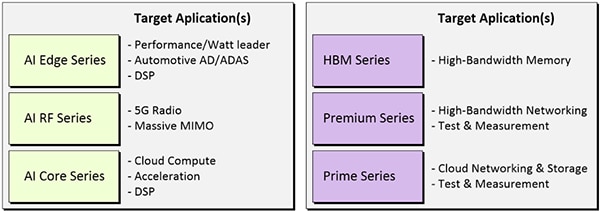

Xilinxの最新製品、Versal ACAP(Versal Adaptive Compute Acceleration Platform)デバイスは、すべて7ナノメートル(nm)プロセステクノロジノードで実装されています。ACAPは高度に統合されたマルチコアコンピュートプラットフォームで、発展的で多様なアルゴリズムに適応できます。またハードウェアおよびソフトウェアの両レベルで動的にカスタマイズ可能で、幅広いアプリケーションおよびワークロードに適合します。ACAPはプログラム可能なネットワークオンチップ(NoC)を中心に設計されており、ハードウェア設計者とソフトウェア開発者の双方が容易にプログラムできます。

Versalデバイスの新機能には、インテリジェントエンジン(MLおよびDSPワークロード用の大規模なベクトルプロセッサアレイ)、テラバイト単位でデータ移動が可能な高帯域幅/低遅延/低電力のプログラム可能NoC、そして組み込み済みコアインフラとシステム接続により性能/使用率/生産性を向上させる統合シェルが含まれます。

Versal ACAP製品ラインナップの概要を図5に示します。

図5:XilinxのVersal ACAPは高度に統合されたマルチコアコンピュートプラットフォームで、発展的で多様なアルゴリズムに適応可能です。ACAPはハードウェアおよびソフトウェアの両レベルで動的にカスタマイズ可能で、幅広いアプリケーションおよびワークロードに適合します。(画像提供:クリーブ・"マックス"・マックスフィールド氏)

図5:XilinxのVersal ACAPは高度に統合されたマルチコアコンピュートプラットフォームで、発展的で多様なアルゴリズムに適応可能です。ACAPはハードウェアおよびソフトウェアの両レベルで動的にカスタマイズ可能で、幅広いアプリケーションおよびワークロードに適合します。(画像提供:クリーブ・"マックス"・マックスフィールド氏)

設計ツールのセクションで詳しく取り上げますが、Versalデバイスが他と異なり優れているのは新しいソフトウェアスタックで、データサイエンティストおよびソフトウェアエンジニア、さらに従来のハードウェア設計エンジニアを対象にしている点です。

現在、非常に多くのXilinxデバイスが提供されています。代表的な製品には、Artix-7 FPGA、Kintex UltraScale FPGA、Kintex UltraScale+ FPGA、Trenz Electronic GmbHのZynq-7000 SoCモジュール、およびZynq UltraScale+ MPSoCなどがあります。

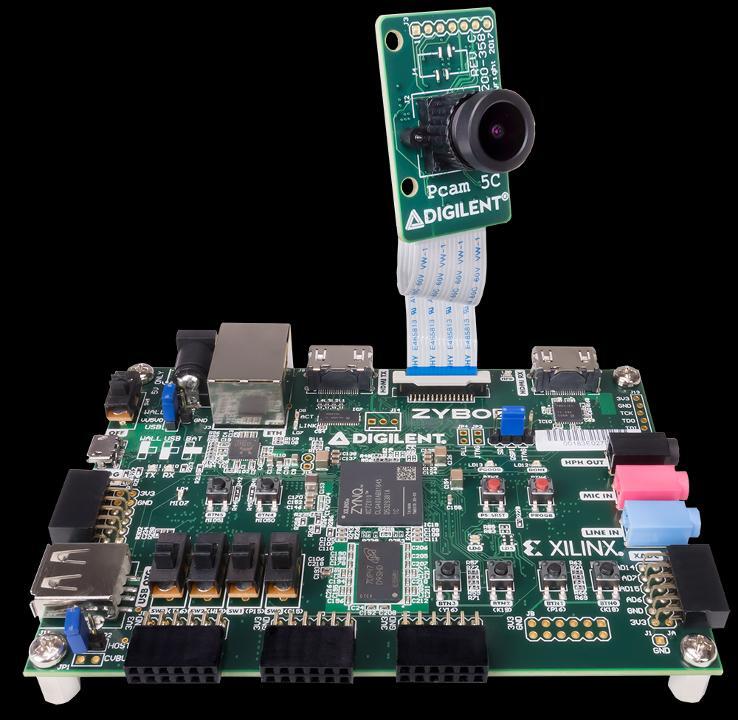

同様に、評価ボードおよび開発ボードにも幅広い種類があります。代表的な製品は、DigilentのArtix-7 FPGA評価ボード、Analog DevicesのKintex UltraScale FPGA評価ボード、XilinxのKintex UltraScale+ FPGA評価ボード、DigilentのZynq-7000 SoC FPGA評価ボード、およびXilinxのZynq UltraScale+ MPSoC FPGA評価ボードです。

XilinxのFPGA、SoC、ACAPを使用した設計および開発

Xilinx製品が他社製品に勝り、異なる点は、その幅広く厚みのある各種設計ツールおよび設計フローにあります。

FPGAに関する本シリーズのパート1では、このようなデバイスを設計する従来の方法は、エンジニアがVerilogやVHDLなどのハードウェア記述言語(HDL)を使用して、レジスタ転送レベル(RTL)と呼ばれる抽象化レベルで設計意図を取り込む方法であると述べました。このRTL記述は、最初に必要に応じて動作をシミュレーションで検証します。次に合成ツールがその記述を引き継ぎ、FPGAのプログラミングに使用する構成ファイルを生成します。

抽象化の次のステップでは、C/C++などのプログラミング言語を使用するか、またはSystemC(イベント駆動型シミュレーションインターフェースを可能にするC++のクラスおよびマクロのセット)などの特別な実装により、設計の意図を取り込みます。これらは、それぞれプレーンC++構文を使用して記述された並行プロセスのシミュレーションを容易にします。このような記述は、通常のプログラムのように実行することで分析してプロファイルし、次にハイレベル合成(HLS)エンジンに渡してRTLを出力し、それを通常の合成エンジンに供給することができます。

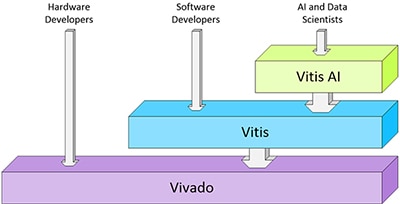

この一連の機能はすべてVivado Design Suite HLxエディションに含まれており、その出力が構成ビットストリームとなり、目標のFPGA、SoC、MPSoC、RFSoC、またはACAPデバイスにロードされます。Vivadoによりハードウェア開発者はCベースの設計を活用し、再利用のために最適化できるようになります。さらに、IPサブシステムの再利用、統合の自動化が可能になり、設計完了も加速されます(図6)。

図6:XilinxのVivadoおよびVitis設計ツールスタックの概要。抽象化の最も適切なレベルでツールを使用して作業できます。ハードウェア設計者はVivado、ソフトウェア開発者はVitis、AI/データサイエンティストはVitis AIで作業可能です。(画像提供:クリーブ・"マックス"・マックスフィールド氏)

図6:XilinxのVivadoおよびVitis設計ツールスタックの概要。抽象化の最も適切なレベルでツールを使用して作業できます。ハードウェア設計者はVivado、ソフトウェア開発者はVitis、AI/データサイエンティストはVitis AIで作業可能です。(画像提供:クリーブ・"マックス"・マックスフィールド氏)

抽象化の次のレベルはVitis統合ソフトウェアプラットフォームによりサポートされ、ソフトウェア開発者はより高速なアプリケーションをシームレスに構築できるようになます。概念的にVitisの「上に位置づけられる」Vitis AIにより、AI/データサイエンティストはTensorFlowの抽象化レベルで作業できるようになります。Vitis AIは、XilinxハードウェアプラットフォームにおけるAI推論の開発プラットフォームで、エッジデバイスおよびAlveo PCIeカードの両方を含んでいます。最適化されたIP、各種のツール、ライブラリ、モデル、サンプル設計が含まれており、XilinxのFPGAおよびACAPデバイスでAIを可能な限り加速できるように設計されています。

Vitis AIからVitisに、さらにVitisからVivadoに情報の受け渡しが行われます。図6で重要なのは、ユーザーに必要なものだけが「表示される」ということです。つまり、ハードウェア開発者にはVivadoのみ、ソフトウェア開発者はVitisのみ、AI/データサイエンティストにはVitis AIのみが表示されることになります。このように、ユーザーは抽象化の最も適切なレベルでツールを使用して作業できます。

ソフトウェア開発者にVitisのような「基盤ハードウェアを意識せず開発できる」ツールスイートを提供することで、より幅広い開発者層がFPGAを利用できるようになります。同様に、AI/データサイエンティストにVitis AIのような「基盤ソフトウェアを意識せずに対象の抽象化レベルに集中できる」ツールスイートを提供することで、やはり新たな開発者層がFPGAを利用できるようになります。

このようなツールスイートを提供するために、業界全体でFPGAツールをかつてない設計抽象化レベルに高めようとしています。Xilinxはその最前線にいます。これにより、開発者は各種デバイスの機能をより手軽に活用して新たな設計に統合できるようになります。

結論

プロセッサとFPGAの組み合わせ、FPGA単独、またはファブリックの一部としてハードプロセッサコアを強化するFPGAによって最適な処理ソリューションが得られることがよくあります。FPGAは1つのテクノロジとしてここ数年で急速に進化しており、柔軟性、処理速度、および電力における多くの設計要件に対応し、インテリジェントインターフェースからマシンビジョンや人工知能まで幅広いアプリケーションに活用することができます。

上述のように、Xilinxが提供するプログラム可能なデバイスは、性能および機能面でベーシックなレベルから非常に高度なレベルまで多岐にわたります。従来のFPGAから、SoC(シングルハードコアプロセッサを含むFPGAプログラム可能ファブリック)、MPSoC(複数ハードコアプロセッサを含むFPGAプログラム可能ファブリック)、RFSoC(RF機能を備えたMPSoC)、およびACAP(Adaptive Compute Acceleration Platform)まで幅広いタイプがあります。

Xilinxは、設計者がこれらのデバイスを使用して設計を作成できるように、ハードウェア開発者(Vivado)、ソフトウェア開発者(Vitis)、AI/データサイエンティスト(Vitis AI)それぞれのニーズに対応するツールスイートを提供しています。

免責条項:このウェブサイト上で、さまざまな著者および/またはフォーラム参加者によって表明された意見、信念や視点は、DigiKeyの意見、信念および視点またはDigiKeyの公式な方針を必ずしも反映するものではありません。