EfinixのQuantum対応FPGAの活用による、低電力かつ高性能のエッジコンピューティングの実装

DigiKeyの北米担当編集者の提供

2020-03-17

従来のクラウドコンピューティングは、遅延、データセキュリティ、エンドユーザーのプライバシー、利用可能な帯域幅、信頼できるコネクティビティなどの課題を抱えています。これらに対処するために、システムの設計者はエッジコンピューティングに移行しつつあります。しかしエッジコンピューティングにもさまざまな特有の課題があり、それらはコスト、サイズ、性能、消費電力から、スケーラビリティ、柔軟性、アップグレードしやすさなどに及びます。これらの課題は、設計者がより多くの画像を処理しようとする場合や、より多くの人工知能(AI)および機械学習(ML)アルゴリズムをデータソースの近くで実装しようとする場合に、特に浮き彫りになります。

結果として、設計者は従来のマイクロコントローラ(MCU)またはアプリケーションプロセッサ(AP)の先にある手法、すなわちフィールドプログラマブルゲートアレイ(FPGA)とそれらの並列処理機能を検討し始めます。FPGAは設計および実装の面で着実に向上しており、スタンドアロンデバイスとして、またはMCUおよびAPとの併用により、設計者のほぼすべての要件を満たすレベルに達していると言えます。しかしながら、FPGAの扱いに不慣れな設計者も多く、その習得に二の足を踏む場合もあります。

この記事では、クラウドからエッジコンピューティングへの移行について概説し、画像処理、AIおよびMLの処理では従来のアーキテクチャが万全でなくなる理由についても取り上げます。次にFPGAについて紹介し、データ集約型のエッジアプリケーションではアーキテクチャの面でFPGAに利点がある理由を解説します。そして、FPGAへの新しいアプローチとして、EfinixのQuantum技術、およびそれを適用する方法について紹介します。

エッジコンピューティング活用の理由は?

従来のクラウドコンピューティングでは、無数のリモートロケーションからデータを収集し、クラウドベースのシステムに供給することで、それらのストレージや分析を行います。ただし、このアプローチには多くの短所があります。たとえば、大量の未加工データを送信するコスト、データ転送時にその完全性とセキュリティを維持するコスト、応答の待ち時間、エンドユーザーのプライバシーの懸念、よくありがちなインターネットへの信頼性の低い接続、利用可能な帯域幅の非効率的な使用などです。

その名称が示すように、エッジコンピューティングとは、計算や分析などの処理をインターネットのエッジに近づけることを意味し、データはそのエッジで生成、分析、収集、適用されます。エッジコンピューティングという用語はアプリケーションまたはデバイス固有ではなく、設計者は必要に応じて、エッジのみでの処理またはクラウドとエッジをバランスさせる処理を選択できます。

エッジアプリケーションには、たとえばスマートファクトリ、スマートシティ、スマートホーム、スマート運輸などがあります。また、エッジデバイスには大規模なハイエンドのエッジサーバから比較的小さなセンサおよびアクチュエータ機器まで幅広くあり、後者の小さな機器類はデータが生成されるインターネットの最エッジ部分に位置しています。

FPGAの利点

演算能力の側面では、従来のプロセッサは意思決定とシーケンシャルタスクにかけては非常に効率的ですが、多くのデータ処理アルゴリズム、たとえば画像処理、AI、MLで使用されるアルゴリズムに関してはあまりにも非効率的です。これらのタスクは、大規模な並列(シーケンシャルと対照的な)処理パイプラインに分割される場合も多く見られます。いわゆる、エッジの際限を含むエッジコンピューティングに処理が託されているのが、まさにこれらのアプリケーションです。

FPGAはあらゆる機能的な組み合わせを実装するようにプログラム(構成)できるので、FPGAにより画像処理、AI、およびMLのアルゴリズムを大規模な並列方式で実行できます。これにより、遅延を最小化するとともに消費電力も削減できます。FPGAは、メインのプログラマブルファブリックに加えて、特殊な乗算器を含んでいるオンチップデジタル信号処理(DSP)ブロックを備えており、DSP集約型のアプリケーション処理を劇的に高速化します。FPGAは、オンチップ処理を容易にするオンチップメモリブロックも備えており、チップ外の処理よりもはるかに高速です。

多数あるFPGAベンダはいずれも、それぞれ独自の製品を提供しています。そのようなベンダの1社であるEfinixは、Quantumと呼ばれる特別なFPGAアーキテクチャを開発しました。これはエッジコンピューティング全般に適しますが、特に画像処理に最適な技術です。その技術を中心に、同社はTrion FPGAシリーズ(およびQuantum ASICシリーズ)を開発し、従来のFPGA技術に比べて消費電力、性能、面積で4倍の優位性を実現しています(図1)。FPGAドメインおよびASICドメインのブリッジとなるEfinity統合開発環境(IDE)もあります。

図1:消費電力、性能、面積で優位性を発揮するTrion FPGAは、カスタムロジック、コンピュートアクセラレーション、ML、ディープラーニング、画像処理などのアプリケーションに対応します。Efinity IDEにより、ユーザーはTrion FPGAからQuantum ASICにシームレスに移行して大量生産に対応できます。(画像提供:Efinix)

図1:消費電力、性能、面積で優位性を発揮するTrion FPGAは、カスタムロジック、コンピュートアクセラレーション、ML、ディープラーニング、画像処理などのアプリケーションに対応します。Efinity IDEにより、ユーザーはTrion FPGAからQuantum ASICにシームレスに移行して大量生産に対応できます。(画像提供:Efinix)

Quantum技術とは?

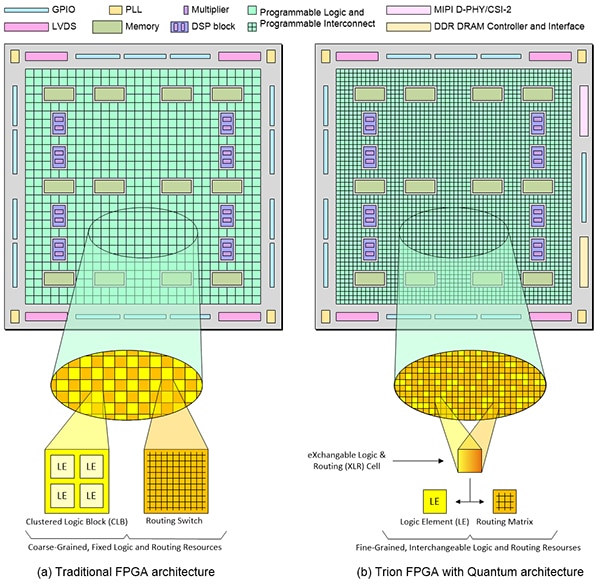

従来のFPGAと同様に、Trion FPGAにはメモリブロックおよびDSPブロックが含まれています。従来との違いはプログラマブルファブリックにあります(図2)。プログラマブルロジックの中核となるのは、論理素子(LE)です。各LEには、ルックアップテーブル(LUT)、マルチプレクサ、およびレジスタが含まれており、それらはいずれも必要に応じた構成が可能です。従来のFPGAの場合、プログラマブルファブリックは「目が粗い」と言えるかもしれません。

図2:従来のFPGAアーキテクチャ(a)は目が粗く、ロジックと相互接続はプログラム可能ですが固定リソースのままです。対照的に、QuantumアーキテクチャベースのTrion FPGA(b)はきめ細かく、ロジックとルーティングのリソースは交換可能です。(画像提供:マックス・マックスフィールド氏)

図2:従来のFPGAアーキテクチャ(a)は目が粗く、ロジックと相互接続はプログラム可能ですが固定リソースのままです。対照的に、QuantumアーキテクチャベースのTrion FPGA(b)はきめ細かく、ロジックとルーティングのリソースは交換可能です。(画像提供:マックス・マックスフィールド氏)

目の粗いファブリックでは、複数のLEが1つの大きなクラスタ化ロジックブロック(CLB)に集積されます。あるベンダは構成可能ロジックブロック(CLB)と呼び、また別のベンダはロジックアレイブロック(LAB)と呼んでいますが、いずれも同じ意味です。

なお重要な点として、この図はあくまでも抽象化した図であることをご理解ください。従来のFPGAにおけるCLBおよびルーティングスイッチ(プログラマブルインターコネクト)は、実際にはこの図のようなチェッカー盤のパターンではありません。しかし、プログラマブルロジックは常にプログラマブルロジックであり、プログラマブルインターコネクトは常にプログラマブルインターコネクトであることに変わりはありません。

従来のアーキテクチャと比べると、Trion FPGAでは個々の論理素子の分解能に及ぶまで格段にきめ細かいことがわかります。さらに、それぞれの「交換可能なロジックおよびルーティング」(XLR)セルは、LEとして機能するか、またはルーティングマトリックスの一部として機能するように構成できます。

Quantumアーキテクチャで使用される構成セルはSRAMベースです。つまり、この技術は「シリコンに依存しない」ということです。これらのセルは標準のCMOSプロセスを使用して製造でき、場合によりミッドレンジFPGAで使用されるフラッシュやアンチヒューズなどの代替構成技術で要求される特殊な処理ステップを必要としません。

このソフトウェア構成可能なロジックおよびルーティング、および高性能な適応型インターコネクトこそが、Quantumベースのアプローチにおいて、消費電力・性能・面積(PPA)の面で、同じプロセス技術ノードで作成された従来のSRAMベースFPGAと比べて4倍の向上をもたらす要素と言えます。

また、Quantumアーキテクチャを活用して作成されたFPGAの場合、従来のFPGAではメタライゼーション層が12以上必要になるのと比べて、7層で済みます。金属の層が増えるごとに複数のマスクおよびプロセスのステップが必要になるので、7層のみであれば設計と製造コストを削減して歩留まりも向上できます。

これらの特性および特長はいずれも、エッジコンピューティングや画像処理においてコスト、サイズ、性能、柔軟性などの利点を求める設計者にとってはきわめて有用です。このように、Trion FPGAは従来のFPGAアプリケーション、そして新たなエッジコンピューティングおよび画像処理アプリケーションのいずれにも最適な技術と言えます。後者のアプリケーションには、たとえばモバイル、モノのインターネット(IoT)、オートメーション、ロボティクス、センサフュージョン、コンピュータビジョン、AI、MLなどがあります。

Trion FPGAの構造

Trion FPGAは、40ナノメートルの低電力シリコンプロセスで製造されており、4,000(4K)~200Kの論理素子(LE)をともないますが、プロセスの拡張により大型デバイスにも対応可能です。すべてのTrion FPGAには、メモリおよびDSPブロックが含まれていますが、それらの容量と個数はデバイスのサイズによって異なります。T4F81C2などの小型デバイスは、機能的には最小限(3,888のLE、78,848のメモリビット、59 GPIO)を備え、ハンドヘルドの制御プレーン機能を対象としています。

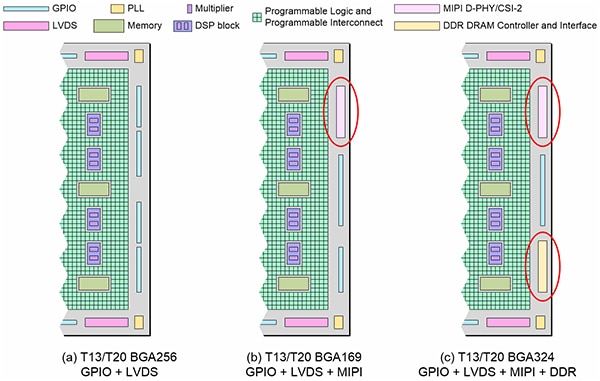

T20F256C3などのハイエンドデバイスになると、それに応じてより多くのリソースを備えます(19,728のLE、1,069,548のメモリビット、195 GPIO)。T13F256C3はT20F256C3と類似していますが、LEは12,828です。また、T13/T20などのデバイスには各種のバージョンがあります(図3)。

図3:汎用FPGAのEfinix T13/T20 BGA256(a)は、I/O集約型のニーズに応える設計に適します。T13/T20 BGA169(b)は2つのMIPI D-PHY/CSI-2ハードコアブロックを備え、MIPIカメラインターフェースのサポートを必要とする設計に対応します。またT13/T20 BGA324(c)は、ハードコアx16ビットダブルデータレート(DDR)DRAMインターフェースおよびコントローラでMIPIインターフェースを拡張しており、メモリ帯域幅集約型のニーズを含む設計に対応します。(画像提供:マックス・マックスフィールド氏)

図3:汎用FPGAのEfinix T13/T20 BGA256(a)は、I/O集約型のニーズに応える設計に適します。T13/T20 BGA169(b)は2つのMIPI D-PHY/CSI-2ハードコアブロックを備え、MIPIカメラインターフェースのサポートを必要とする設計に対応します。またT13/T20 BGA324(c)は、ハードコアx16ビットダブルデータレート(DDR)DRAMインターフェースおよびコントローラでMIPIインターフェースを拡張しており、メモリ帯域幅集約型のニーズを含む設計に対応します。(画像提供:マックス・マックスフィールド氏)

MIPI CSI-2カメラインターフェースは、その低電力、低遅延、低コストのチップ間コネクティビティの特性から、モバイルなどの分野で最も広く採用されています。また、1080p、4K、8K(およびそれ以上の解像度)のビデオ、高解像度の画像処理など、幅広い高性能フォーマットもサポートします。ここで特に着目されるのは、MIPI CSI-2がエッジアプリケーションのビジョンセンサに使用される最も有力なインターフェースであることです。これらのアプリケーションの設計をサポートするために、T13/T20 BGA169 FPGAは2つのMIPI D-PHY/CSI-2ハードコアブロックを備えています(図3)。

DDRメモリは、高帯域幅のデータ転送をサポートしますが、厳密なタイミングプロトコルに従う必要もあります。TrionのT13/T20 BGA324(図3)では、強化されたMIPI D-PHY/CSI-2インターフェースに加えて、拡充されたx16ビットDDR DRAMインターフェースとコントローラも備えており、メモリ帯域幅集約型のニーズを含む設計に対応します。

Quantum ASIC

上述のように、Trion FPGAで使用されている構成セルはSRAMベースです。これにより、システムの電源を最初に投入するとき、Trion FPGAはその構成データを外部メモリデバイスからロードするか、またはホストプロセッサによる「ビットバンギング」によってロードする必要があります。これを大量生産で実現できるように、EfinixはさらにQuantum Accelerated組み込みFPGA(eFPGA)ソリューションをQuantum ASICとして提供しています。この場合、EfinixはT4、T8、T13またはT20の設計を採用してマスクプログラム済みQuantum ASICバージョンを作成できます。これは内部的に起動し、外部の構成デバイスを必要としません。

Trion FPGAによる設計および開発

Efinixは各種の評価ボードおよび開発キットを提供しており、Trion FPGAの習熟に役立ちます。たとえば、Trion T8F81C-DK T8 Trion FPGA開発キット、Trion T20F256C-DK T20 Trion FPGA評価ボード、Trion T20MIPI-DK T20 MIPI D-PHY/CSI-2開発キットなどがあります。

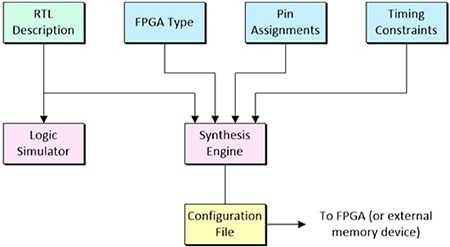

FPGAによる開発で使用される最も一般的な手法の1つは、言語駆動設計(LDD)と呼ばれます。この手法では、VerilogやVHDLなどのハードウェア記述言語(HDL)を使用してレジスタ転送レベル(RTL)と呼ばれる抽象レベルで設計の意図を表します。論理シミュレーションによる検証の後に、この表現は、ターゲットのFPGAタイプ、ピン割り当て、入力から出力への最大遅延などのタイミング制約といった追加の情報とともに、合成エンジンに送られます。合成エンジンからの出力は構成ファイルです。このファイルはFPGAに直接ロードされるか、または外部メモリデバイスにロードされます(図4)。

図4:論理シミュレーションによる検証の後、RTL設計の説明が、FPGAタイプ、ピン割り当て、タイミング制約などの追加の設計詳細とともに合成エンジンに送られます。合成エンジンから出力される構成ファイルは、FPGAにロードされます。(画像提供:マックス・マックスフィールド氏)

図4:論理シミュレーションによる検証の後、RTL設計の説明が、FPGAタイプ、ピン割り当て、タイミング制約などの追加の設計詳細とともに合成エンジンに送られます。合成エンジンから出力される構成ファイルは、FPGAにロードされます。(画像提供:マックス・マックスフィールド氏)

EfinixのEfinity IDEは、このクラスのツールに該当します。このソフトウェアでは、シンプルで使いやすいグラフィカルユーザーインターフェース(GUI)およびコマンドラインスクリプトのサポートによって、RTLからビットストリームへの完全なフローを実現できます。直感的なダッシュボードは、開発者に対してフロー(合成、配置、ルーティング、ビットストリーム生成など)をガイドする役割を果たし、段階ごとに自動または手動で制御できます。開発者はEfinityの合成エンジンを利用して、Trion FPGAが備えるQuantumアーキテクチャを最大限に活用することで、消費電力・性能・面積において4倍の優位性を実現できます。

ModelSim、NCSim、または無料のIVerilogシミュレータによるシミュレーションフローのサポートに加え、Efinity IDEには、Interface Designer(デバイス周辺でロジックを制約しブロックにピンを割り当てる)、Floorplan Editor(設計ロジックおよびルーティング配置を参照する)、Timing Browserおよび静的タイミング分析(設計のパフォーマンスを評価する)、およびLogic AnalyzerおよびVirtual I/Oデバッグコアを備えた統合ハードウェアデバッガも含まれています。

結論

クラウドベースのアプローチの代わりに、またはそのアプローチの補完として、より多くの画像処理、AIおよびMLの処理をエッジで実行するのにつれて、設計者はこれらの処理アーキテクチャにFPGAを含めることを検討し、コスト、性能、消費電力、サイズ、スケーラビリティ、柔軟性、アップグレードしやすさなどの問題に、より的確に対処する必要があります。

設計者の中にはFPGAの習熟面で二の足を踏む向きもありますが、これまで述べたように、EfinixのQuantum技術に代表されるFPGAの進歩により、低コスト化、フォームファクタの小型化、高性能化、さらに優れた柔軟性を通じて、投資効果をより迅速に得ることができます。

これにより、FPGAは従来のFPGAアプリケーションとともに新たなエッジコンピューティングにも最適な技術となり、モバイル、IoT、オートメーション、ロボティクス、センサフュージョン、コンピュータビジョン、AI、MLなどのアプリケーション分野でその真価を発揮します。

関連リソース

免責条項:このウェブサイト上で、さまざまな著者および/またはフォーラム参加者によって表明された意見、信念や視点は、DigiKeyの意見、信念および視点またはDigiKeyの公式な方針を必ずしも反映するものではありません。