ロジックレベルシフトの基礎

通信とGPIOにおけるハイ/ローのロジックレベル電圧の混合

概要

最新のデジタルデバイス設計では、さらなる小型化、高速化、効率化が進んでいます。中心的な5Vロジックに、3.3V、2.5V、1.8V、それ以下など、かつてない低さの電圧規格が加わったことにより、不整合のシステム間で確実で効率的な通信を成立させる方法が求められています。設計者は、このようなプラットフォーム間で、論理「1」または論理「0」を予測可能な方法で実現させる必要があります。

バイナリまたは2段のロジック電圧間での変換/絶縁は、予測可能な回路動作を後押しします。設計者は、5Vピンを介した3.3V信号であれば「動作するはず」と考えるかもしれませんが、あらゆる状況でそれが当てはまるとは限りません。逆に、3.3V、5V許容のピンを介した5V信号は確かにほとんどの場合で動作しますが、この方法では部品の追加や場合によっては過電圧を「消散させる」ことにより、高コストになります。

代替方法はあるか?

アクティブなトランスレータ/レベルシフトデバイスは、一般的な変換の問題を解決し、さらに反転、プッシュプル出力、トライステート、差動機能などの利便性を得られる場合もあります。しかし、それほど複雑でなく、より広いロジック電圧レベルと双方向通信を可能にするデバイスは何かあるでしょうか?小型のディスクリートMOSFETであれば、高周波で高効率な変換を実現できます。I²CやダイレクトGPIOピン接続のような通信用のレベルシフトは、このような安価な半導体といくつかの追加の受動デバイスによって実現できます。MOSFETを適切に選択することで、例えば車載用回路のモニタリングにも利用される、12Vや18Vなどのより高いロジック電圧にも対応できます。

注:Hs(ハイスピード)モードのI²Cでは、NXPのPCA9306双方向トランスレータのような、より高精度な部品が必要な場合もあります。

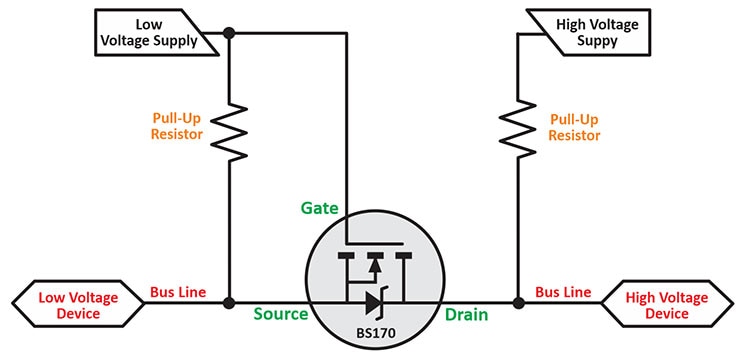

例:BS170 (Nチャンネルエンハンスメントモード電界効果トランジスタ)

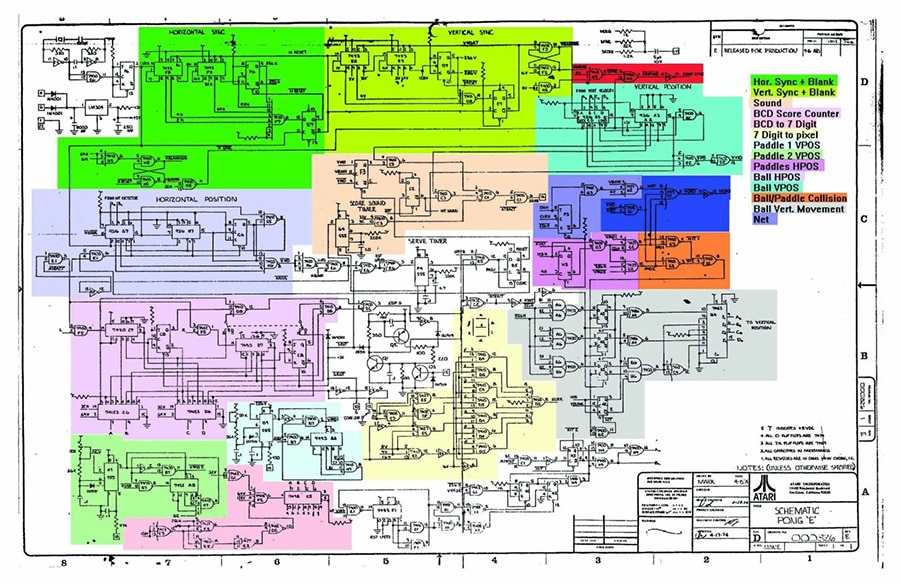

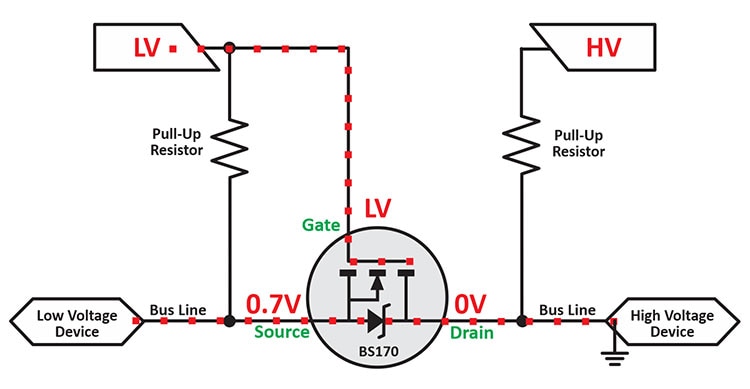

BS170は、オン状態抵抗を最小限に抑えながら、低電圧で低電流のスイッチングアプリケーションに適した確実で高速なスイッチング性能をもたらすように設計されています。図1に、基本的な通信やGPIOロジックレベルのシフトを行うために必要な接続を示します。

図1:基本的なシングルバスのレベル変換MOSFET回路。

図1:基本的なシングルバスのレベル変換MOSFET回路。

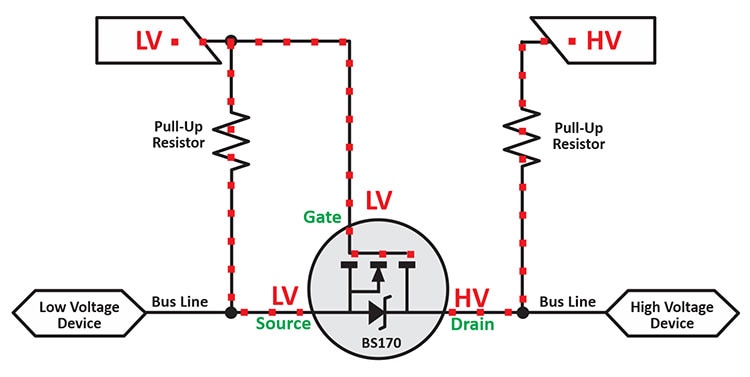

MOSFET各側のロジックハイレベルは、それぞれの電源へのプルアップ抵抗によって実現され、高速モード(400kHz)I²C信号や他の同様な高速デジタルインターフェースの変換を可能にします。MOSFETのゲートは、低電源電圧レベルに保持されます。バスラインをプルダウンするデバイスがない場合、MOSFETのソース側バスラインは低電圧プルアップ抵抗によってプルアップされます。MOSFETのゲート/ソース間電圧(VGS)は閾値を下回り、MOSFETは導通していません。そのため、MOSFETのドレイン側バスラインは、高電圧プルアップ抵抗によってプルアップされます。MOSFET各側のバスラインはHIGHに保持されますが、電圧レベルは異なります(図2を参照)。

図2:ロジックハイの電圧変換。

図2:ロジックハイの電圧変換。

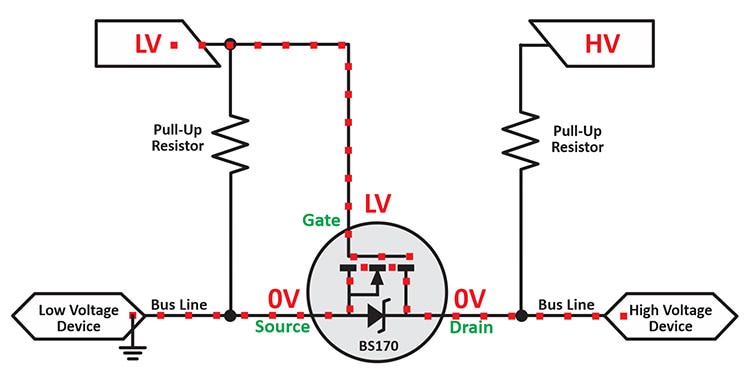

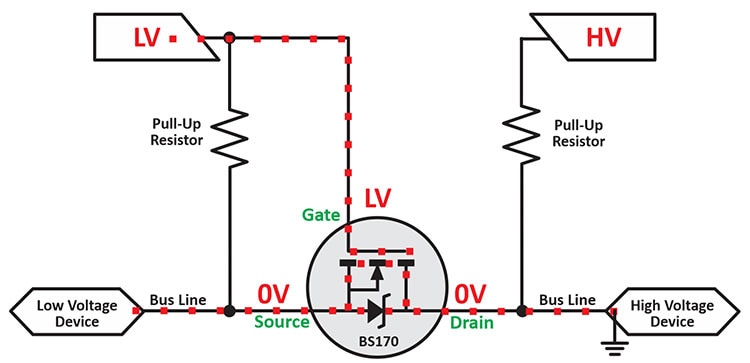

低電圧デバイスがMOSFETのソース側バスラインをプルダウンし、ゲートが低電源電圧に留まると、VGSは閾値を超えて上昇し、MOSFETが導通し始めます。そして、MOSFETのドレイン側バスラインもプルダウンされます(図3を参照)。

図3:ロジックローの電圧変換が低電圧デバイスによって開始されます。

図3:ロジックローの電圧変換が低電圧デバイスによって開始されます。

高電圧デバイスがMOSFETのドレイン側バスラインをプルダウンすると、MOSFET基板のダイオードにおけるわずかな電圧降下によって、ソースも部分的にプルダウンされます(図4を参照)。

図4:ほぼロジックローの電圧変換が、高電圧デバイスによって開始されます。

図4:ほぼロジックローの電圧変換が、高電圧デバイスによって開始されます。

MOSFETのソース側が部分的にプルダウンされると、VGSは閾値を超えて上昇し、MOSFETは実質的に基板ダイオードをバイパスして導通し始めます(図5を参照)。

図5:完全なロジックローの電圧変換が、高電圧デバイスによって開始されます。

図5:完全なロジックローの電圧変換が、高電圧デバイスによって開始されます。

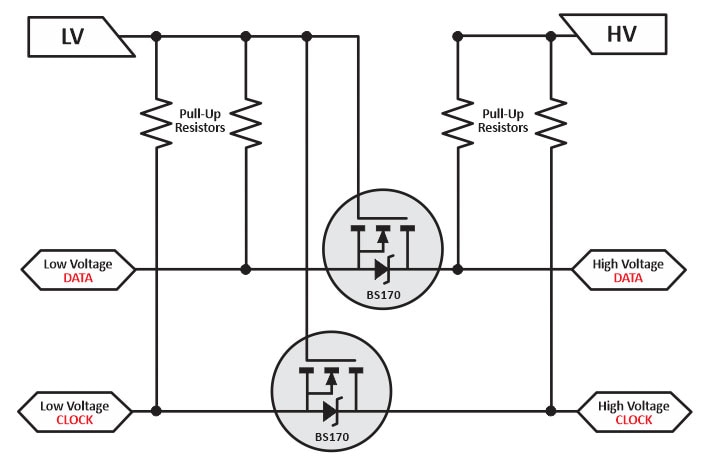

この3つの状態は、駆動部分によらず、バスシステムの両方向に転送されるロジックレベルを示しています。MOSFETの機能性に応じて、高/低電源電圧の多くの組み合わせが可能です。ロジックレベルの競合が、ポイントツーポイントGPIO、センサ出力、または双方向マルチライン通信のいずれに関係する場合でも、MOSFETレベルシフタは便利なツールです。図6に、2つのMOSFETを使用した、2ライン双方向変換型通信回路の実装を示します。

図6:2ライン双方向変換型データ通信回路。

図6:2ライン双方向変換型データ通信回路。

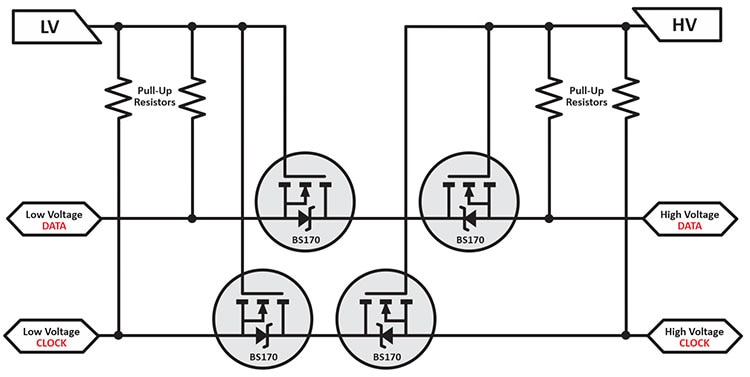

絶縁

高電圧デバイスがパワーダウンされたり高電源電圧に電力損失が発生したりした場合にランダムなロジックレベルを防ぐには、追加のMOSFETを「ドレインツードレイン」で実装して高電圧ロジックバスラインを絶縁できます。

図7:変換型データ通信回路におけるバスラインの絶縁。

図7:変換型データ通信回路におけるバスラインの絶縁。

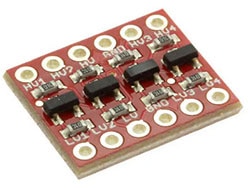

開発ボード

ロジックレベル変換をより深く習得できるように、複数のメーカーが、すばやく接続して実験できるMOSFETまたはロジック変換デバイス搭載の開発ボードを必要な受動ペリフェラルデバイスとともに提供しています。

まとめ

シンプルながら効果的なこのようなロジック変換の方法を上手く利用するには、MOSFETとプルアップ抵抗の適切な選択がカギになります。一般的なデバイスのデータシートには、実験に必要な情報が記載されています。BS170には、4.7kΩ~10kΩ範囲のプルアップ抵抗がほとんどの場合に通用します。また、専用のロジックレベルコンバータICは、I/Oや電源電圧入力における15kVのESD保護といった付加的な機能も備えています。

Have questions or comments? Continue the conversation on TechForum, Digi-Key's online community and technical resource.

Visit TechForum