マイクロコントローラ間の正確な通信を確保するI/O電圧規格とその役割

母国語を使って外国人とコミュニケーションを取ろうとしたところ(図1)、相手があなたの言葉を理解できないだけでなく、あなたの「はい」が相手の言語では「いいえ」を意味していることに気付いた状況を想像してみてください。これはまさに、互換性のないI/O規格を持つ2つの集積回路(IC)が通信しようとしたときに起こることです。その結果、最良の場合でも混乱が生じ、最悪の場合、ハードウェアの損傷につながります。

図1:異なるIO規格の使用による混乱を象徴するAI生成画像。(提供:AI生成)

図1:異なるIO規格の使用による混乱を象徴するAI生成画像。(提供:AI生成)

マイクロコントローラは0と1の2進ロジックで動作します。これらのロジックレベルに対応する電圧範囲があります。たとえば、あるマイクロコントローラは、0.3V未満の電圧にロジック「0」を割り当て、2.7Vより高く3.3V以下の電圧にロジック「1」を割り当てます。しかし、もう1つのマイクロコントローラは、1.2Vから1.8Vの電圧にロジック「1」を割り当てます。1番目のマイクロコントローラが2番目のマイクロコントローラに3.3Vの信号を送信すると(図2)、受信デバイスの耐電圧を超える可能性があり、永久的な損傷を引き起こす可能性があります。

図2:互換性のないIO規格の2つのICが通信している様子。(提供:AI作成)

図2:互換性のないIO規格の2つのICが通信している様子。(提供:AI作成)

このため、I/O電圧の互換性を理解し管理することは、組み込みシステム設計において非常に重要です。適切なレベルシフトや電圧変換を行わないと、2つのチップ間のシンプルな接続でも、予測不可能な動作やハードウェアの故障につながる可能性があります。

I/O電圧規格の役割

I/O電圧規格は、デジタルロジック信号の許容電圧レベルを定義しています。これらの規格は、ロジックハイ(1)またはロー(0)を規定します。これらは、デバイスが信号を正しく解釈し、適切に応答できることを確保します。これらのレベルについて一般的に合意された規格がなければ、デバイスが信号を読み違えたり、相互に通信できなかったりする可能性があります。

規格で定義された用語:

- VIH(入力高電圧):ロジックハイとして認識される最小電圧。

- VIL(入力低電圧):ロジックローとして認識される最大電圧。

- VOH(出力高電圧):ロジックハイとして出力される最小電圧。

- VOL(出力低電圧):ロジックローとして出力される最大電圧。

通信を成功させるためには、一方のデバイスの出力レベルが、受信デバイスの許容入力範囲内に収まっていなければなりません。

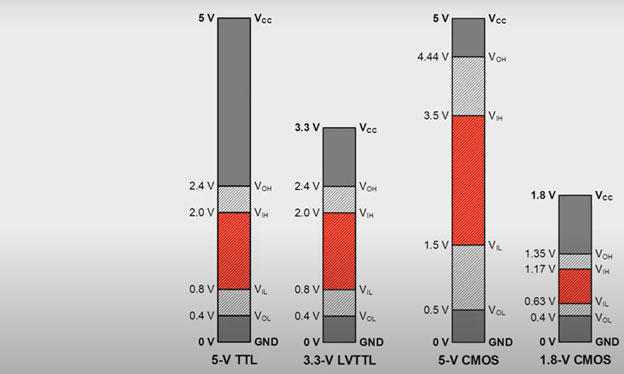

シングルエンドI/O規格

シングルエンド入出力(SIO)規格(図3)は、最も一般的な入出力(I/O)規格の1つです。信号の伝達には、コモングランドを基準とした1本のワイヤを使用します。低速で低複雑度の設計に関しては、SIOは、2つの相補的な信号を使用する差動信号規格に比べ、コスト効率が高く、シンプルな代替手段です。

低電圧相補型金属酸化膜半導体(LVCMOS)は一般的なシングルエンド規格で、多くの場合LVMOSと呼ばれます。LVCMOSは通常、1.8V、2.4Vまたは3.3Vで動作し、ロジックハイとローの特定の閾値を定義します。SIO規格のシンプルさは、一定の代償を伴います。LVCMOSのようなSIOは、長距離や高周波ではノイズや信号劣化の影響を受けやすくなります。異なる電圧領域で動作するデバイスとLVCMOSをインターフェースする場合、レベルシフタを使用して適切な電圧互換性を確保することが重要です。

図3:異なるI/O規格の電圧レベル。(提供:Texas Instruments)

図3:異なるI/O規格の電圧レベル。(提供:Texas Instruments)

I/Oインターフェースの課題

1. 電圧の不一致

異なる電圧レベルで動作するデバイスのインターフェースに関する最も一般的な問題は、電圧の不一致です。たとえば、3.3Vの出力をレベルシフトせずに1.8Vの入力に接続すると、低電圧のデバイスを損傷する可能性があります(図2)。

これを緩和するためには、一方のICの入力高電圧(VIH)と入力低電圧(VIL)のレベルが、もう一方のICの出力高電圧(VOH)と出力低電圧(VOL)のレベルに一致するようにしなければなりません。

2. シグナルインテグリティ

高速では、反射、リンギング、クロストークが信号を破損する可能性があります。適切な終端処理、インピーダンスマッチング、トレースルーティングは、クリーンな信号遷移を維持するために不可欠です。

3. 電源領域

複数の電圧レールを持つシステムでは、領域間の信号の分離や変換に注意しなければなりません。レベルシフタ、分圧器、またはプルアップ抵抗によるオープンドレイン構成が一般的なソリューションです。

高度なロジックファミリ:LVPECL、CML、VML、LVDS

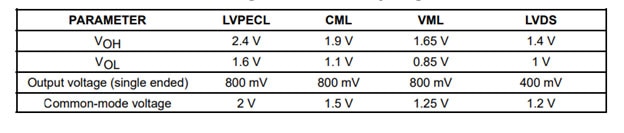

高速通信システムでは、LVPECL(Low Voltage Positive Emitter Coupled Logic)、CML(Current Mode Logic)、VML(Voltage Mode Logic)といったロジックファミリが使用されます(表1)。これらは、より高速な遷移と優れたノイズ耐性を提供しますが、慎重な設計が求められます。

- LVPECL:3V前後で動作し、差動信号伝送と高速性能が特徴

- CML:高速スイッチングと低ジッタを実現するために定電流源を使用

- VML:一般的ではないものの、負荷に依存しない振幅で電圧モード信号伝送を提供

- LVDS:中速、低消費電力の差動信号伝送に広く採用

表1:ロジックレベル(LVPECL、CML、VML、LVDS)別の電圧パラメータ。(提供:Texas Instruments)

表1:ロジックレベル(LVPECL、CML、VML、LVDS)別の電圧パラメータ。(提供:Texas Instruments)

I/Oインターフェースのベストプラクティス

- VIH、VIL、VOH、VOLの値については、必ずデータシートを確認してください。

- 電圧領域間でインターフェースする場合は、レベルシフタを使用します。

- オシロスコープやロジックアナライザを使用して、早くから頻繁にテストを行います。

I/Oインターフェースは、単にピンを接続するだけではありません。すべての信号が意図したとおりに正確に理解されるよう確保することが重要です。組み込みシステムが複雑化し、複数の電圧領域やロジックファミリで動作するようになる中で、I/O互換性を習得することが重要になってきています。

電圧規格を理解し、不一致を予測し、ベストプラクティスを適用することで、変換エラーのない明確な通信を実現する、堅牢で信頼性の高いシステムを設計することができます。ただし、異なるI/O規格のICをインターフェースする必要がある場合、信号レベルの不一致を緩和する1つの方法は、レベルシフタを使用することです。

レベルシフタ

レベルシフタ(LS)は、電圧トランスレータとも呼ばれており、異なる電圧レベルで動作するコンポーネント間を安全にインターフェースするために、組み込みシステムで使用される回路です。たとえば、3.3Vで動作するマイクロコントローラが、1.8Vロジックで動作するセンサと通信する必要がある場合、レベルシフタは、損傷やロジックエラーのリスクなしに、マイクロコントローラとセンサの間で信号が正しく変換されることを確保します。使用されるプロトコルによって、レベルシフタは単方向と双方向に分類されます。LSは一般的に、MOSFET、バッファIC、または専用のトランスレータチップを使用して実装されます。シグナルインテグリティの維持や、混合電圧環境におけるコンポーネントの保護に不可欠な役割を果たしています。

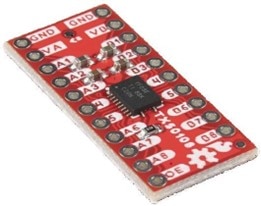

図4:8チャンネルのレベルシフタモジュール。(提供:SparkFun)

図4:8チャンネルのレベルシフタモジュール。(提供:SparkFun)

関連リソース

Have questions or comments? Continue the conversation on TechForum, Digi-Key's online community and technical resource.

Visit TechForum