JKフリップフロップの仕組み

初代Digi-Keyer(デジタル電子キーヤーキット)を使用した実践例あり

はじめに

フリップフロップは、1ビットのバイナリデータを2つの安定した状態に保存するための集積回路です。カウンタ、レジスタ、分周器などに幅広く使用され、本記事の例では、非安定マルチバイブレータと呼ばれる順序論理回路に使用されています。

フリップフロップには多様なタイプがありますが、共通機能として、セットおよびリセット入力、クリア、プリセット、クロック入力、コンプリメンタリ論理出力などが備わっています。フリップフロップは、クロック入力の立ち上がりまたは立ち下がりエッジによってトリガされます。一般的には、SRフリップフロップ、Dフリップフロップ、Tフリップフロップといったタイプがあり、JKフリップフロップは、他のタイプの多くをエミュレートするように構成できるため、「ユニバーサル」と呼ばれることもあります。

JKフリップフロップの機能

フリップフロップを使用する際には、デバイスのデータシートにある真理値表を手元に置いておく必要があります。その表を参考に、複数の入力オプションとクロック遷移に応じた出力特性を決定します。たとえば、Texas InstrumentのCD74HCT73Eは、共通の特性と読みやすい真理値表を特長とする、標準的なデュアルJKフリップフロップです。

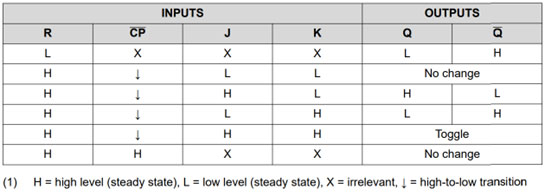

覚えておくべき基本的な真理が2つあります。Q(バー)出力またはnotQ出力は常にQ出力の補数であることと、クロック入力がHighからLowに遷移するときの出力を決定するJK入力構成は4つしかないことです。可能なJK構成については、図1を参照してください。トグルとは、JとKがともにHighで、クロックがHighからLowに遷移したときに、Q出力とnotQ出力の現在の状態が反転することを意味します(真理値表の条件4)。

図1、標準的なJKフリップフロップデータシートの真理値表

図1、標準的なJKフリップフロップデータシートの真理値表

前述した基本的な真理では、リセット(R)入力を考慮に入れていません。リセットがLowで保持されている場合、リセット入力はフリップフロップを初期状態にします。データシートでは、リセットがLowの場合のクロックとJK入力に関して「無関係」という用語が使用されています。これらの入力の変化は、リセットがHighに保持され、クロック遷移を受け取るまで、出力に影響しません。

重要ポイント:フリップフロップは最初の電源入力時に、出力が自動的に既知の状態に設定されることはありません。どの出力状態が優先されるかは予測できませんが、リセット入力によって電源入力後の出力を既知の状態に初期化できます。

順序論理回路の例:モールス符号発生器

DAHを作成するには3つのDITが必要

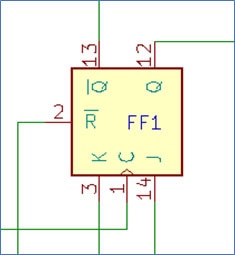

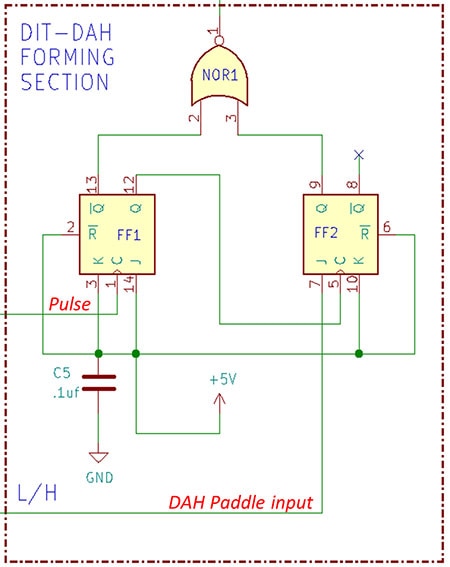

Digi-Keyer(デジタル電子キーヤーキット)のモールス符号発生器には、特定のタスクを持つさまざまなコンポーネントが備わっています。フリップフロップの役割を示すために、FF1およびFF2と呼ばれるフリップフロップに関連する要素を搭載しています。Digi-KeyerのDIT-DAH符号生成セクションの回路図は図2を参照してください。

図2、Digi-Keyerフリップフロップ符号生成回路

図2、Digi-Keyerフリップフロップ符号生成回路

符号(DITとDAH、別名「ト」と「ツー」)の生成に入る前に、NOR1論理ゲートの機能を説明する必要があります。NOR1は符号出力回路の初段であるだけでなく、NOR1出力がLowの間、タイミング回路がFF1に規則的なパルスを送信できるようにします。NOR1出力がHighの場合、現在のタイミングサイクルが終了するとパルスは停止します。

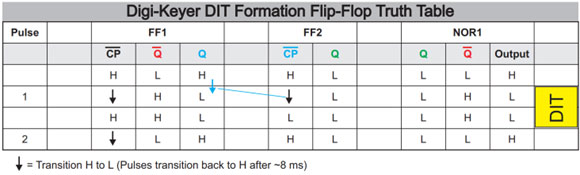

DITパドルスイッチを押すと、タイミング回路からFF1のC入力に、最初のHighからLowへの遷移パルスがトリガされます。JK入力がともにHighに保持されるため、出力端子QとnotQが反転します。notQは、NOR1をトリガしてタイミング回路にLow信号を出力し、DITが生成中であることを示します。タイミング関数が完了すると、FF1に別のパルスを送信して反転させ、FF1を正常な状態に戻します。DIT生成時、FF1のQ出力はFF2のC入力をトリガしますが、DAHパドルが押されていないため(FF2のJ入力がLow)、FF2の出力は図1の真理値表の条件3に従います。図3は、1つのDITを生成する順序論理の真理値表を大まかにまとめたものです。

図3:DIT生成順序論理の真理値表

図3:DIT生成順序論理の真理値表

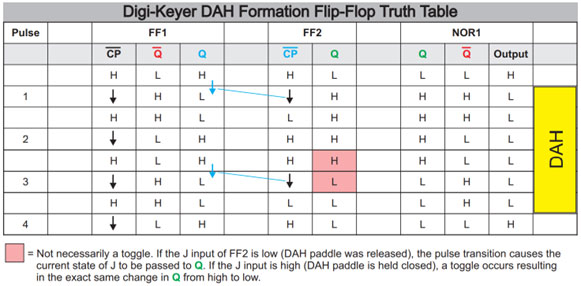

同様に、DAHパドルを押すと、タイミング回路のイニシャルパルスがトリガされてFF1が反転し、FF2のJ入力がHighになり、FF2の出力も反転します。FF2のQ出力もまた、NOR1出力をLowにするトリガとなるため、タイミングパルスが継続します。NOR1の出力は、FF1とFF2がともに正常な状態に戻るまでHighに戻りませんが、これには3回のDITサイクルが必要です。図4は、1つのDAHを生成する順序論理の真理値表を大まかにまとめたものです。

図4、DAH生成順序論理の真理値表

図4、DAH生成順序論理の真理値表

フリップフロップが正常な状態に戻るまでの時間は、HighからLowへの遷移の間に経過する時間によって決まります。この例では、タイミング回路での1パルス周期のLow時間は8msに固定されていますが、High時間は15ms~150msの範囲で調節可能です。最も遅い設定では、DIT符号の長さは約158ms、DAHの長さは約474msです。FF1とFF2を正常な状態に戻す最後のHighからLowへの遷移は、8msでHighに戻るため、パドルの一方または両方が閉じている場合(High)、符号と符号の間に一定の間隔が生じます。

もう1つの重要ポイント:回路の電源入力時、FF1とFF2は前述のように論理がランダムな状態になることがあります。NOR1の出力がLowになっている場合、タイミング回路は、FF1とFF2が正常な状態になるまでパルスを送信し続けます。その結果、電源入力後にリセット入力を使用することなく、フリップフロップは自動的に正常な状態に初期化されます。

まとめ

フリップフロップの論理は、順を追って説明することが難しいため、図3や図4のような真理値表を作成することで、バックグラウンドで行われている作業を可視化できます。この例では、マイクロコントローラや常時動作する固定クロックを使用せずに、多段階の順序論理を実行しました。意図的に入力を変化させなければ、出力が変化しないという意味では、フリップフロップの出力は保存されたデータであると言えます。しかし、揮発性データでもあるため、電源が切れるとデータは失われます。モールス符号発生器の目的は、データの作成ではありません。フリップフロップは、クロックパルスのHighからLowへの遷移の間に前の状態を記憶し、次の状態を決定するために使用されます。

リソース:

Digi-Keyerを組み立てて、その仕組みを知ることに興味があるでしょうか。DigiKeyでは、図面、部品表、プログラミングコード、PCBファイルなどのフルセットをこのリポジトリで提供しています。

https://media.digikey.com/pdf/Project%20Repository/Digikeyer.zip

Have questions or comments? Continue the conversation on TechForum, Digi-Key's online community and technical resource.

Visit TechForum