アナログの基礎 - パート3:パイプラインADCとその使用法

DigiKeyの北米担当編集者の提供

2020-07-14

編集前記:A/Dコンバータ(ADC)はアナログをデジタルの世界に接続するデバイスであり、現実の世界に接続する電子システムの基本的なコンポーネントです。またこれは、システムのパフォーマンスを決定する重要な要素にもなります。このシリーズでは、ADCの基礎から各種タイプ、さらにはADCのアプリケーションについて解説します。パート1ではSAR ADCについて、パート2では、デルタシグマ(ΔƩ)コンバータについて解説します。このパート3では、パイプラインADCの機能、特性、使用法について解説します。パート4では、デルタシグマADCがどのようにして超低ノイズの結果を得ることができるかを紹介します。パート5では、SAR ADCにとって難しい入力駆動の問題を探ります。

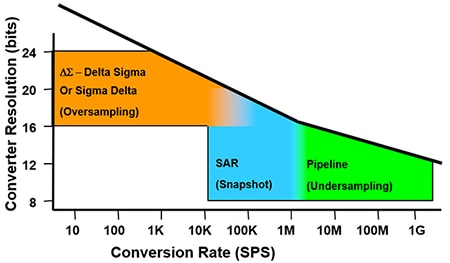

ADCがその機能を発揮する用途には、超高速マルチキャリアセルラーインフラ基地局、テレコミュニケーション、デジタルプリディストーション観測、バックホールレシーバなどがありますが、これらはいずれもギガサンプル/秒のサンプリング性能を備えたADCを必要とする領域です。このアナログの基礎シリーズのパート1と2では、それぞれ逐次比較レジスタ(SAR)ADCとデルタシグマ(ΔƩ)ADCについて解説し、これらのADCを適所に利用する方法についても説明しています。しかし、これらはどちらも、ギガサンプル/秒(GSPS)の速度で動作するという課題には、必ずしも適した技術とは言えません。

たとえば、SAR ADCでは「スナップショット」アルゴリズムを使用しますが、シリアルアプローチを用いるため、その動作速度は10Mサンプル/秒(MSPS)に制限されます。高分解能のΔƩ ADCのオーバーサンプリングアルゴリズムでは、最大5MHzの24ビット出力データレートを生み出す複数サンプルの取得と平均化のために、さらに時間がかかります。GSPSの動作速度は、SAR ADCおよびΔƩ ADCのサンプリング周波数の範囲とはかけ離れたレートです。

この超高速ADCの課題に対する解決策は、パイプラインADCです。パイプラインADCは、複数のサンプルを処理しながら、同時にGSPSの動作速度でその出力にデータを供給します。

この記事では、ΔƩ、SAR、およびパイプラインの各ADCを簡単に比較し、高速なコンバータ出力の実現にともなう問題点と、このような高速アプリケーションでパイプラインADCが有力な代替手法になり得る理由について解説します。さらに、Texas Instrumentsから提供される2つのパイプラインADCを紹介します。1つは精度を、もう1つは高速性を重視するデバイスです。また、これらのADCを使用する方法についても解説します。

パイプラインADCとは?

パイプラインADCは、連続的な複数の段によって構成されています。差動構成による初段は、最上位ビット(MSB)値を評価し、次に信号を調整して、MSB-1変換のためにその信号を次段に渡します。それぞれの段は、他の段と同時に処理を実行します(図1)。

図1:パイプライントポロジには複数の段があり、マルチビットコンバータの1ビットの変換を実現し、信号を調整してから次の段に渡します。(画像提供:Texas Instruments)

図1:パイプライントポロジには複数の段があり、マルチビットコンバータの1ビットの変換を実現し、信号を調整してから次の段に渡します。(画像提供:Texas Instruments)

図1に示されるそれぞれの段は機能的に類似しており、1ビットまたは2ビットのみを分解します。各段には、サンプルアンドホールド、低分解能のフラッシュADC、および信号調整機能があります。段1はサンプルを受け取り、MSBを瞬時に決定します。このMSBのデジタル値が、最初のラッチ(Latch 1)に供給されます。MSBが1と決定された場合、この段でサンプルから電荷のMSB値が差し引かれます。次にパイプラインコンバータは、残りの電荷に2倍のゲインを適用します。1つの段で動作が完了すると、アナログ差分が次の段に供給されます。2倍のゲインによる設計の優れた点は、段1から段nまで基本的に同じ回路になることです。

段の数は、ADCのビット数と一致する場合がよくあります。最終的な変換出力により、段ごとのデジタル結果が出力ラッチで結合されます。この変換プロセスでは、数クロックサイクルのデータレイテンシが発生します。

ΔƩ、SAR、パイプラインADCのサンプリングの比較

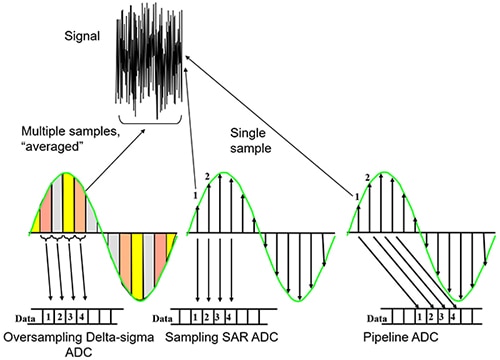

ΔƩコンバータは、オーバーサンプリングアルゴリズムを使用して、有限インパルス応答(FIR)または無限インパルス応答(IIR)のデジタルフィルタを実装します。これらのフィルタでは、複数のサンプルの取得時に信号出力のレイテンシ(待ち時間)または遅延が生じますが、メリットとして分解能がきわめて高くなります。結果として、ΔƩコンバータのアクイジション時間は、変換ごとに信号を1回だけサンプリングするSARまたはパイプラインコンバータよりも長くなります(図2)。

図2:最も低速で最高分解能のΔƩ ADCは、低周波数の信号処理に使われます。速度、分解能ともに中位のSAR ADCは、汎用アプリケーションの処理に適します。高速で低分解能のパイプラインADCは、最先端の高速ソリューションに適します。(画像提供:DigiKey)

図2:最も低速で最高分解能のΔƩ ADCは、低周波数の信号処理に使われます。速度、分解能ともに中位のSAR ADCは、汎用アプリケーションの処理に適します。高速で低分解能のパイプラインADCは、最先端の高速ソリューションに適します。(画像提供:DigiKey)

SAR ADCでは、時間上の特定の取得点で入力信号のスナップショットを得られます。電荷再配分の技法を使用するSARは、ゼロ待ち時間の変換をすばやく完了します。パイプラインコンバータはアンダーサンプリング技術を使用して、電荷の再分配技術を駆使するだけでなく出力で結果が出現するのを遅らせることで、高速変換を実現します。この変換アルゴリズムでは、データレイテンシが生じます。

レイテンシと変換速度の関係は、SAR、パイプライン、およびΔƩコンバータごとに異なります(図3)。

図3:ΔƩオーバーサンプリングおよび平均化アルゴリズムでは、最終的な出力データワードの出現に遅延が生じます。SAR ADCの出力は次のサンプル取得の前に出現するため、SAR ADCのレイテンシはゼロです。パイプラインコンバータではデータ結果に遅延がともない、レイテンシがゼロではなくなります。(画像提供:DigiKey)

図3:ΔƩオーバーサンプリングおよび平均化アルゴリズムでは、最終的な出力データワードの出現に遅延が生じます。SAR ADCの出力は次のサンプル取得の前に出現するため、SAR ADCのレイテンシはゼロです。パイプラインコンバータではデータ結果に遅延がともない、レイテンシがゼロではなくなります。(画像提供:DigiKey)

図3において、ΔƩコンバータは変換結果ごとに複数のサンプルを平均化します。ΔƩの平均化フィルタは、通常、FIRまたはIIRデジタルフィルタです。このマルチサンプリング平均化により、全体的な変換時間が長くなります。その代わり高分解能が可能になり、スループット時間/精度の相互依存が生じます。

SARコンバータの変換時間には、入力信号のアクイジション時間と変換時間が含まれます。アクイジション時間では、信号アクイジションが実際に発生する時点より前に入力信号整定が可能になります。スループット時間は、内部電荷再分配と連続的なシリアルデータ出力信号を組み合わせたもので、MSB値から始まります。

パイプラインADCでは、サンプルの取得が外部入力クロックの立ち上がり(または立ち下がり)エッジで開始されます。このサンプルで取得された電荷が段2に供給され、コンバータでは別の入力信号と同等の電荷がキャプチャされます。段2のMSB値が確定します。以降の外部クロックでは、2番目に取得された信号が段2に供給され、最初の信号が段3に供給されます。このクロックサイクル中に、最初に取得された信号のMSB-1と2番目に取得された信号のMSBが決定されます。このプロセスが、取得されたすべての信号で続行されます。入力信号に完全なデジタル出力の表現がある場合、コンバータの出力段には入力信号に並行する表現が示されます。

このアーキテクチャによって、パイプラインADCは、Mサンプル/秒から1GSPSを超えるサンプリングレートに広く使われています。分解能には、サンプルレートが高速な8ビットから低速な16ビットまでの幅があります。このような分解能とサンプリングレートの対象となる用途は幅広く、電荷結合素子(CCD)画像、超音波医療用画像、デジタルレシーバ、基地局、デジタルプリディストーション、デジタルビデオなどがあります。これらの用途の中には、速度だけでなく精度にも力点が置かれる場合があります。

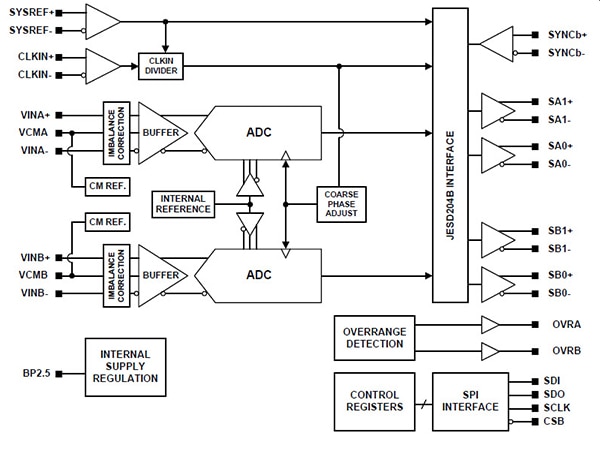

高精度パイプラインADC

高精度パイプラインADCの代表例には、Texas Instrumentsから提供される16ビット、370MSPSデュアルチャンネルのパイプラインADCであるADC16DX370があり、データインターフェースには7.4Gbit/sのバックエンドJESD204Bが使われます。入力信号150MHzのADC16DX370は、信号対ノイズ比(SNR)、スプリアスフリーダイナミックレンジ(SFDR)、およびノイズスペクトル密度(NSD)が、それぞれ69.6dBFS(フルスケールのdB)、88dBFS、および-152.3dBFS/Hzです。

それぞれのADCには、入力バッファと不均衡補正回路、および内部ドライバに必要な基準電圧があります。統合された入力バッファは、内部のスイッチ型サンプリングコンデンサの電荷と電荷のキックバックノイズを排除します。このバッファにより、駆動アンプ、アンチエイリアシングフィルタ、インピーダンスマッチングの要件が緩和されます(図4)。

図4:高性能な370MSPSのデュアルパイプラインADCであるADC16DX370は、内部リファレンスを備えます。アナログ信号を16ビットのデジタルワードに変換します。(画像提供:Texas Instruments)

図4:高性能な370MSPSのデュアルパイプラインADCであるADC16DX370は、内部リファレンスを備えます。アナログ信号を16ビットのデジタルワードに変換します。(画像提供:Texas Instruments)

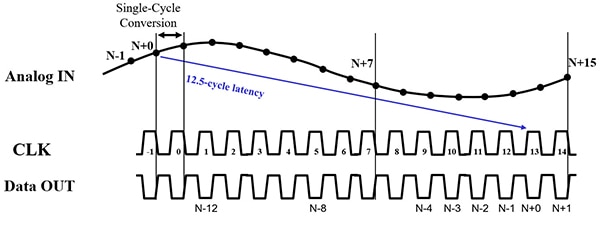

ADC16DX370では、低ノイズレシーバとクロック分周器によってCLKIN入力からサンプリングクロックが取得されます。入力クロック分周器により、高周波クロック信号がシステム全体に分配され、ADCデバイスでローカルに分周されるため、信号が共通の中間周波数(IF)でシステムの他の部分に結合するのを避けることができます。ADCのコアレイテンシは、12.5クロックサイクルです(図5)。

図5:このタイミング図は、ADCのコアレイテンシが12.5クロックサイクルであることを示しています。(画像提供:DigiKey)

図5:このタイミング図は、ADCのコアレイテンシが12.5クロックサイクルであることを示しています。(画像提供:DigiKey)

サンプリングは、(CLKIN+) - (CLKIN-)差動信号の立ち上がりエッジで行われます。最小コア値として、デジタル出力コードは12.5クロックサイクルのデータ遅延の後に利用可能になります。CLKIN入力分周器の係数は、1、2、4、または8です。

ADC16DX370には、差動クロック入力ピンがあります。各ピンのDCへの内部終端は50Ω抵抗で、合計100Ωの内部差動終端を可能にします。クロック入力ピンには、外部ACカップリングが必要です。

デュアルパイプラインADCのプリント基板設計は、性能を十分に発揮させるために重要な要素です。デバイスを出入りするすべての信号を適切にルーティングするには、少なくとも6つのレイヤが必要です。信号ルーティングレイヤには、信号リターンパスを制御してループ領域を最小化するために、隣接する強固なグランドプレーンが必要です。また、インピーダンス制御のためにマイクロストリップおよびストリップラインのルーティングを慎重に行う必要があります。電源プレーンおよび隣接する強固なグランドプレーンを使用することで、電源のリターンパスを制御します。また、電源プレーンとグランドプレーン間のスペースを最小にすると、分散デカップリングを向上させて性能を改善できます。

ADC16DX370のターゲットアプリケーションには、高IFサンプリングレシーバ、マルチキャリア基地局レシーバ、および高分解能化と370MSPSの変換速度を補完するマルチモード/マルチバンドレシーバがあります。この16ビットパイプラインADCは、たとえばRFヘテロダインレシーバサブシステムのバックグラウンドノイズから小信号を識別するために必要なSNR(69.6dBFS)性能を備えています。

設計者がADC16DX370を評価できるように、このADCは、ADC16DX370EVM評価ボードおよび連動するHigh-Speed Data Converter(HSDC)Proソフトウェアによりサポートされています。このEVMには、PCとの接続用にmini-USBケーブルが付属しています。TIはTSW16DX370EVMリファレンス設計ボードも提供しており、100MHz超の使用可能帯域幅でレシーバIFサブシステムソリューションを評価するためにこのボードを使用できます。

高速パイプラインADC

高速動作と幅広いダイナミックレンジが優先される場合、設計者はTexas Instrumentsのデュアルチャンネル、1GSPSの12ビットADCであるADS54J20を活用できます。このADCは、67.8dBFSの高SNR、-157dBFS/Hzのノイズフロアで動作するように設計されています。広い瞬時帯域幅で最高のダイナミックレンジを目標にする用途に最適なADCです(図6)。

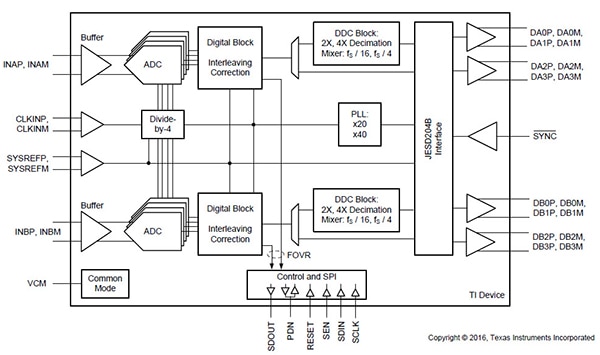

図6:ADS54J20デュアルパイプラインADCは、-157dBFS/Hzのノイズフロアを実現するインターリーブ補正を備えており、デシメーションデジタルフィルタのオプションもあります。(画像提供:Texas Instruments)

図6:ADS54J20デュアルパイプラインADCは、-157dBFS/Hzのノイズフロアを実現するインターリーブ補正を備えており、デシメーションデジタルフィルタのオプションもあります。(画像提供:Texas Instruments)

図6に示されるADS54J20では、インターリーブアルゴリズムとディザーアルゴリズムを使用して、高SFDRでクリーンなスペクトルが実現されます。このデバイスにはプログラム可能なデシメーションフィルタの各種オプションもあり、幅広い周波数で高いSNRとSFDRを必要とするシステムに有用です。

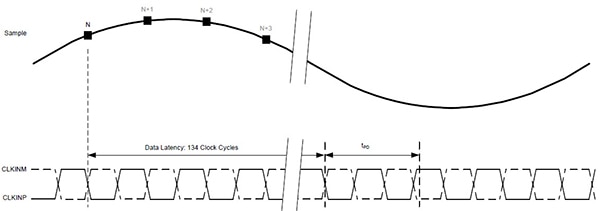

バンドパスデシメーションフィルタには、デジタルミキサと3つの連結されたFIRフィルタが含まれており、約134出力クロックサイクルのレイテンシに加えて、ロジックゲートおよび出力バッファの伝播遅延(4ナノ秒)が生じます(図7)。

図7:このADCレイテンシのタイミング図には、134クロックサイクルに加えて、ロジックゲートと出力バッファの伝播遅延(tPD)が示されています。(画像提供:Texas Instruments)

図7:このADCレイテンシのタイミング図には、134クロックサイクルに加えて、ロジックゲートと出力バッファの伝播遅延(tPD)が示されています。(画像提供:Texas Instruments)

デジタルブロック、インターリーブエンジン、およびデシメーションフィルタ(図6)と、高速サンプリング1GHzクロック周波数の組み合わせが、コンバータの遅延の一因になります。

ADS54J20のターゲットアプリケーションの中には、レーダおよびアンテナのアレイ、ブロードバンドワイヤレス、ケーブルモデムターミネーションシステム(CMTS)、およびDOCSIS 3.1レシーバがあります。

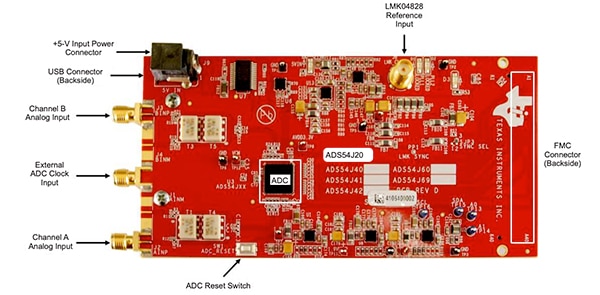

また、ADS54J20は評価ボードによってサポートされ、ここではADS54J20EVMが該当します(図8)。

図8:ADS54J20高速ADCをサポートするADS54J20EVM評価ボードには、Mini USBケーブルと電源ケーブルが付属します。(画像提供:Texas Instruments)

図8:ADS54J20高速ADCをサポートするADS54J20EVM評価ボードには、Mini USBケーブルと電源ケーブルが付属します。(画像提供:Texas Instruments)

ADS54J20EVMは、HSDC Proソフトウェアと組み合わせて使用でき、PC接続用のMini USBケーブル、および電源ケーブルが付属しています。

まとめ

SAR ADCとΔƩ ADCにはこれらが有用なデバイスとなる適所があり、一方で超高速ADCの課題に相応しいソリューションになるのがパイプラインADCです。パイプラインADCは、複数のサンプルを処理しながら、数百キロサンプル/秒からギガサンプル/秒の速度でデータを出力に供給します。しかし、すべてのパイプラインADCが動作速度のみに力点を置くわけではありません。この記事で述べたように、パイプラインADCによって高精度も達成できます。

どこに力点を置くかにかかわらず、パイプラインADCは、高速セルラー基地局、超高速マルチキャリアセルラーインフラ基地局、テレコミュニケーション、デジタルプリディストーション観測、バックホールレシーバなど、高速変換を必要とする多くのアプリケーションに最適なオプションです。

免責条項:このウェブサイト上で、さまざまな著者および/またはフォーラム参加者によって表明された意見、信念や視点は、DigiKeyの意見、信念および視点またはDigiKeyの公式な方針を必ずしも反映するものではありません。