アナログの基礎 - パート4:デルタシグマADCの最適化による低ノイズの実現

DigiKeyの北米担当編集者の提供

2020-08-05

編集前記:A/Dコンバータ(ADC)はアナログをデジタルの世界に接続するデバイスであり、現実の世界に接続する電子システムの基本的なコンポーネントです。またこれは、システムのパフォーマンスを決定する重要な要素にもなります。このシリーズでは、ADCの基礎から各種タイプ、さらにはADCのアプリケーションについて解説します。アナログの基礎シリーズのパート1では、SAR ADCについて説明します。パート2では、デルタシグマコンバータについて説明します。パート3では、パイプラインADCについて検討します。このパート4では、デルタシグマADCがどのようにして超低ノイズの結果を得ることができるかを紹介します。パート5では、SAR ADCにとって難しい入力駆動の問題を探ります。

デルタシグマ(ΔƩ)集積回路トポロジは、A/Dコンバータ(ADC)に引き続き実装され、プロセス制御、高精度温度測定、および重量計のアプリケーション向けに高分解能、高集積、および低電力のソリューションを提供します。

このコンバータタイプに関する不可解な事実は、それが7.78dBの理論的信号対ノイズ比(SNR)(5Vシステムの2V(VRMS)ノイズと同等)を使用した1ビット変換で始まるという点です。そこから、ADCは正真正銘の24ビットデルタシグマコンバータに発展し、146dBの理論的SNR(5Vシステムの244nV RMSノイズと同等)を提供します。

この1ビットから24ビットへの分解能の増加は、量子化ノイズを低減してSNRを向上させるオーバーサンプリングアルゴリズム、ノイズシェーピング変調器、およびデジタルフィルタに依存しています。12または16ビットの逐次比較レジスタ(SAR)ADCへ供給するアンプの入力段を代わりに使用することにより、ΔƩコンバータの複雑さとその関連ノイズを回避できます。この設計パスは機能しますが、プリント基板上の集積回路の増加やBOMの増大が必要になります。

ノイズの問題に対処するためのより優れた方法は、超低ノイズΔƩ ADCに真正面から取り組むことです。

この記事では、低ノイズの対象アプリケーションと、この要件を満たすためにΔƩ ADCがどのように内部設計されているかを手短に説明します。次に、Texas Instrumentsの2つのΔƩ ADC(一方は24ビットの精度、他方は32ビットの精度を特長とする)を紹介し、両者において堅牢なデジタルフィルタリングを活用する方法を説明します。

ΔƩ ADCの適合用途

アナログの観点から、温度、圧力、ロードセル、および光センサの出力を測定する場合、さまざまなレベルの精度が必要です。アンプは根本的に、これらの小さな(ほとんどの場合DC付近の)アナログの発生を定量化する能力を向上させます。漸進的なデジタル化により、視点や機能の変化がもたらされると同時に、センサ信号を保存および変更する機能が向上しました。

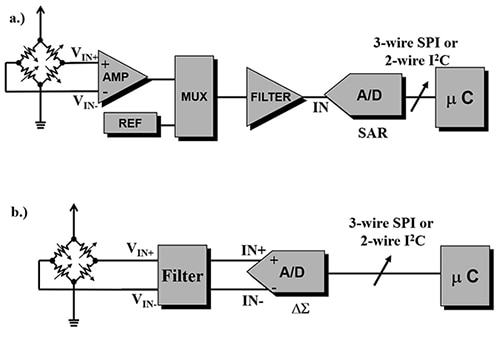

デジタルキャプチャへの一般的なセンサ信号パスは、センサから始まり、ゲイン、マルチプレクシング、およびフィルタ段を通過して、ADCに至ります(図1a)。

図1:センサ信号をデジタル化する2つの技術では、SAR ADC(a)やΔƩ ADC(b)を使用します。高分解能回路において、SAR ADCは増幅および5次アクティブフィルタを必要とする一方で、ΔƩ ADCはフロントエンドのアナログ1次パッシブフィルタを必要とします。(画像提供:A Baker’s Dozen: Real Analog Solutions for Digital Designers, B. Baker, ISBN 0-7506-7819-4)

図1:センサ信号をデジタル化する2つの技術では、SAR ADC(a)やΔƩ ADC(b)を使用します。高分解能回路において、SAR ADCは増幅および5次アクティブフィルタを必要とする一方で、ΔƩ ADCはフロントエンドのアナログ1次パッシブフィルタを必要とします。(画像提供:A Baker’s Dozen: Real Analog Solutions for Digital Designers, B. Baker, ISBN 0-7506-7819-4)

図1aのコンバータは、12ビットから18ビットへの変換を実行可能なSAR ADCであり、最大10Mサンプル/秒(MSPS)の変換レートで動作できます。16ビットコンバータは、216または65,536セグメントを提供します。5Vシステムにおいて、最下位ビット(LSB)は5V/216298または76.3μVであり、理論的SNRは98dBです。SARコンバータの前にアナログゲインを実行することにより、さらに高い精度を実現できます。

ΔƩ信号チェーン(図1b)は、BOMを低減させる単一のコンバータにより信号チェーンの分解能を向上させます。ΔƩ ADCでは、16ビットから32ビットへの変換を実行できます。この信号チェーンにおいて、24ビットΔƩ ADCは224または16,777,216セグメントを提供します。したがって、5Vシステムにおいて、LSBは5V/224または298nVであり、理論的SNRは146dBです。この分解能レベルにより、コンバータの精度はセンサの機能に近づきます。

フィルタリング計算を実装するための時間を必要とする内部デジタルフィルタにより、24ビットΔƩ ADCは遅くなります。このコンバータの一般的な出力データレートは、数Hz~1MSPSです。アナログフィルタは、複雑な3つのオペアンプ、5次アナログフィルタに代わり、低コストの1次抵抗器-コンデンサ(RC)フィルタになったことに注意してください。

これら2つのアプローチのノイズ間の違いは明確です。ΔƩ ADCの低ノイズは、SAR ADCの低ノイズを上回ります(表1)。

*注:SNR = 6.02N + 1.76(Nはビット数)

|

表1:16ビットSAR ADCおよび24ビットΔƩ ADC向けに5Vのフルスケール入力電圧を備えたADCセグメント、LSB、および理論的SNR。(データ提供:DigiKey)

ΔƩ ADCは、速度の仕様ではなく精度が最優先される温度、圧力、およびロードセルなどのセンサソリューション向けの優れたソリューションを提供します。このADCは、アナログではなくデジタルのノイズ低減技術を使用することにより、これらの小さな電圧値に変換できます。

ΔƩ ADCの内部

ΔƩ ADCの内部は80%デジタルです。一般的に、コンバータは入力信号を受信すると、即座にそのアナログ信号をデジタル信号に変換します。次に、コンバータは、そのデジタル信号をデジタルフィルタ段への後続の変調器変換と組み合わせます。そこでは、蓄積された1ビット信号が複数ビットに変換されます。さらに、コンバータは、デジタル出力段を通して、最後のマルチビット変換を待機中のマイクロコントローラへ順次送信します。

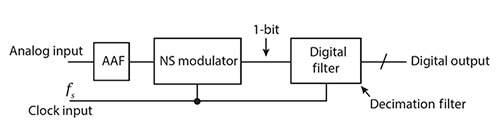

アナログ信号は、最初に外部1次アンチエイリアシングフィルタ(AAF)を通過します。次に、ノイズシェーピング(NS)変調器がアナログ信号を取得して、コンバータのクロックレートでデジタルフィルタに1ビットストリームを生成します(図2)。

図2:一般的なΔƩは、アナログ信号を1次AAFに通し、NS変調器を使用して1ビットストリームを生成します。それから、マイクロコントローラへのデジタル出力でマルチビット結果を生成します。(画像提供:CMOS: Mixed-Signal Circuit Design, 2nd Edition, J. Baker, ISBN 978-0-470-29026-2)

図2:一般的なΔƩは、アナログ信号を1次AAFに通し、NS変調器を使用して1ビットストリームを生成します。それから、マイクロコントローラへのデジタル出力でマルチビット結果を生成します。(画像提供:CMOS: Mixed-Signal Circuit Design, 2nd Edition, J. Baker, ISBN 978-0-470-29026-2)

デジタルフィルタは、1ビットストリームから複数のコードでクロックし、デジタルフィルタで完全なマルチビット結果を作成します。これらのマルチビット結果は、デジタル出力を通して順次送信されます。

ΔƩ変調器

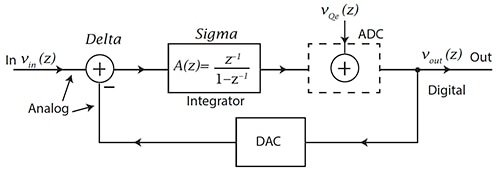

積分器/フィードバックループの数により、ΔƩ変調器の順序が決定されます。1次ΔƩ ADC変調器には、1つの積分器とフィードバックループがあります(図3)。

図3:アナログ積分器と1ビットADCおよびフィードバックループのDACを備えた1次変調器。VQe(z)は、量子化ADCのノイズです。(画像提供:CMOS: Mixed-Signal Circuit Design, 2nd Edition, J. Baker, ISBN 978-0-470-29026-2)

図3:アナログ積分器と1ビットADCおよびフィードバックループのDACを備えた1次変調器。VQe(z)は、量子化ADCのノイズです。(画像提供:CMOS: Mixed-Signal Circuit Design, 2nd Edition, J. Baker, ISBN 978-0-470-29026-2)

図3では、アナログ信号(VIN(z))が変調器のデルタ(Δ)部分に入ります。次に、アナログ信号は積分器段またはシグマ(Ʃ)段を通過して、1ビットADC(図2ではfSのサンプルレートを使用)に進みます。これは、コンパレータである場合があります。このデジタル化されたクロック信号は、1ビットのD/Aコンバータ(DAC)にフィードバックし、さらにΔ段のVOUT(z)に進みます。1ビットDACは、アナログ入力信号VIN(z)から差し引かれるアナログ電圧を提供します。この1次変調器の伝達関数は、以下のようになります。

![]() 式1

式1

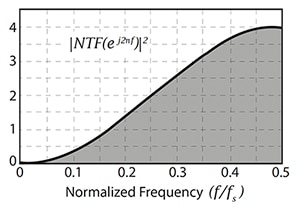

積分器とフィードバックループにより、変調器は変調器のデジタル出力データストリームにノイズシェーピングアルゴリズムを実装します(図4)。

図4:ノイズ伝達関数(NTF)が 1-z-1と等しく、0.5正規化周波数がFS/2と等しい場合の、ΔƩ変調器の出力におけるノイズシェーピング機能。(画像提供:Understanding Delta-Sigma Data Converters, Schreier, Temes, ISBN 0-471-46585-2)

図4:ノイズ伝達関数(NTF)が 1-z-1と等しく、0.5正規化周波数がFS/2と等しい場合の、ΔƩ変調器の出力におけるノイズシェーピング機能。(画像提供:Understanding Delta-Sigma Data Converters, Schreier, Temes, ISBN 0-471-46585-2)

図4において、ノイズシェーピング特性は、変換1ビット量子化ノイズを低減するための最初の段階です。ノイズを正常に高周波数へ押し込むことにより、ローパスデジタルフィルタはノイズ低減プロセスを完了します。

より高次の変調器には、追加の積分器とフィードバックループが含まれます。たとえば、3次変調器には3つの積分器と3つのフィードバックループがあります。ノイズシェーピング機能は、DC付近のノイズを低減してシェーピングされたノイズを増やすことにより、変調器の順序と共に変化します。

より高次の変調器は、シリコンハードウェアの増加、安定性の低下、信号範囲を犠牲にすることにより、向上した性能を提供します。

ΔƩデジタルフィルタ

ΔƩ ADCは、オーバーサンプリング(OS)を使用することにより動作します。オーバーサンプリングは、ADC出力データレート(FD)に対する変調器(FS)のサンプルレートの比率です(式2)。

![]() 式2

式2

オーバーサンプリングは、ローパスデジタルフィルタを使用して、ノイズシェーピングされたデータの帯域幅をデジタル的に制限することにより、ΔƩ ADCノイズを向上させます。

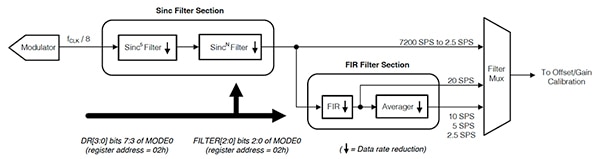

ΔƩ ADCで一般的に使用される2つのデジタルフィルタは、sin(pf)/pf (sinc)および直線位相有限インパルス応答(FIR)フィルタです。Texas InstrumentsのADS1235(24ビットΔƩ ADC)と ADS1262およびADS1263(32ビットΔƩ ADC)のデジタルフィルタ実装は、独占的にsincフィルタを使用するか、FIRフィルタが後に続くsincの組み合わせかの選択肢を提供します(ADS1263は、バックグラウンド測定を意図した補助24ビットΔΣ ADCを統合しています)(図5)。

図5:ADS1235 24ビットΔƩ ADCでは、sincフィルタを排他的に使用するか、FIRフィルタが後に続くsincの組み合わせを使用できます。(画像提供:Texas Instruments)

図5:ADS1235 24ビットΔƩ ADCでは、sincフィルタを排他的に使用するか、FIRフィルタが後に続くsincの組み合わせを使用できます。(画像提供:Texas Instruments)

図5において、sinc(「Sinc」で示される)フィルタは、ローパスデジタルフィルタです。sincフィルタの出力(w(n))は、式3を使用して計算されます。

![]() 式3

式3

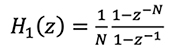

zドメイン伝達関数は、次のようになります。

式4

式4

周波数応答は、以下のようになります。

![]() 式5

式5

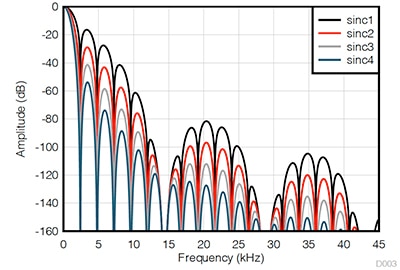

図5において、SincNは、直列に配置されたN個の同一sincフィルタと等しくなります。グラフ上のsincフィルタの振幅対周波数応答は、くし型の外観を示しています(図6)。

図6:ADS1262/63では、多くのsincデジタルフィルタ(sinc2は直列に配置された2つの同一SINCフィルタと等しく、sinc3は直列に配置された3つの同一sincフィルタと等しい場合など)が、2400サンプル/秒(SPS)でくし型の周波数応答を形成します。(画像提供:Texas Instruments)

図6:ADS1262/63では、多くのsincデジタルフィルタ(sinc2は直列に配置された2つの同一SINCフィルタと等しく、sinc3は直列に配置された3つの同一sincフィルタと等しい場合など)が、2400サンプル/秒(SPS)でくし型の周波数応答を形成します。(画像提供:Texas Instruments)

図6において、ピークおよびヌルは、sincフィルタ応答の特性です。周波数応答のヌルは、f (Hz) = N ·FD(N = 1, 2, 3, ....の場合)で発生します。ヌル周波数において、フィルタのゲインはゼロです。

sincフィルタ(直列)は、減衰を増大させ、待ち時間を増加させます。たとえば、7.3728MHzの外部クロックレートを使用した特定のsincフィルタ計算で14400SPSの出力データレートを生成する場合、2番目のsincフィルタの出力のデータレートは7200SPSです。

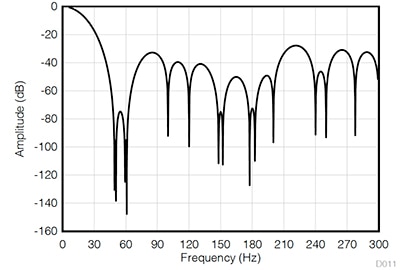

ローパスFIRフィルタは、係数に基づくフィルタです。このフィルタには、50Hzおよび60Hzの同時減衰と、2.5SPS~20SPSのデータレートでの高調波があります。FIRフィルタのデータレートの変換待ち時間は、シングルサイクルと同じです。FIRフィルタは、sincフィルタからフィルタリング前のデータを受信し、10SPSの出力データレートを生成するためのデータをデシメートします(図7)。

図7:ADS1262/63では、FIRフィルタが50Hzおよび60Hz信号を減衰させてライン周波数干渉を低減し、これらの周波数の近くに配置された一連の応答ヌルを提供します。ヌルは、50Hzおよび60Hz高調波で繰り返します。(画像提供:Texas Instruments)

図7:ADS1262/63では、FIRフィルタが50Hzおよび60Hz信号を減衰させてライン周波数干渉を低減し、これらの周波数の近くに配置された一連の応答ヌルを提供します。ヌルは、50Hzおよび60Hz高調波で繰り返します。(画像提供:Texas Instruments)

FIRフィルタは50Hzおよび60Hz信号を減衰させてライン周波数干渉を低減し、これらの周波数の近くに配置された一連の応答ヌルを提供します。応答ヌルは、50Hzおよび60Hz高調波で繰り返します。

高精度低ノイズΔƩ ADC

低ノイズΔƩ ADCの優れた例は、前述したTexas InstrumentsのADS1235差動入力24ビットコンバータです。

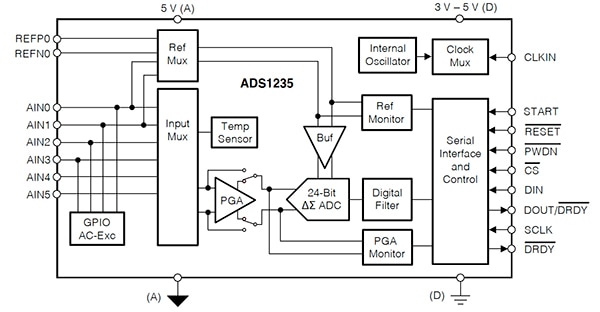

ADS1235は、3つの差動入力または5つのシングルエンド入力を備えた高精度7200SPSのΔƩ ADCであり、1、64、および128のゲインを備えた統合型のプログラム可能なゲインアンプ(PGA)です。このデバイスには、PGAオーバーレンジモニタや基準モニタなどの診断機能も含まれています。このADCは、重量計、歪ゲージ、および抵抗圧力センサなどの高精度機器に、高精度のゼロドリフト変換データを提供します(図8)。

図8:6チャンネルアナログ入力およびGPIO入力マルチプレクサを備えたADS1235 24ビットΔƩ ADC のブロック図。(画像提供:Texas Instruments)

図8:6チャンネルアナログ入力およびGPIO入力マルチプレクサを備えたADS1235 24ビットΔƩ ADC のブロック図。(画像提供:Texas Instruments)

ADS1235において、ノイズ性能に影響を与える重要な要素は、データレート、PGAゲイン、およびチョップモードです。低速のデータレートは、デジタルフィルタのコーナ周波数をもたらし、ノイズを低減します。さらに、チョップモードで実行される2ポイントデータ平均化により、ノイズは通常の動作と比較して√2減少します。

低周波数、2.5SPSのデータレート、および1V/VのPGAゲインにより、5Vシステムのsinc3デジタル出力へのコンバータノイズは0.15mVRMS(0.3mVピーク-ピーク(PP))であり、24ビットの有効分解能、24ビットのノイズフリー分解能を備えています。このデバイスの理論的(および実際の)SNRは、146dBです。実際、これらの条件において、安定した4次変調器およびsinc1からsinc4のフィルタは、24ビットの有効分解能と24ビットのノイズフリー分解能を生成します。

ADS1235は、2.5SPSデータレート向けの完璧に近い24ビット変換を実現しました。このファミリの次世代ΔƩ ADCは、Texas InstrumentsのADS1262/63です。これらのデバイスの主な違いは、ADS1262/63は低ノイズ回路を向上させ、拡張32ビット出力データレジスタを提供することです。

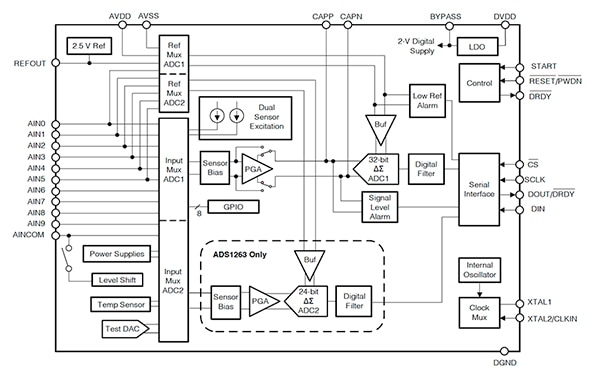

ADS1262/63には、1、2、4、8、16、および32のゲインを備えた、向上した低ノイズCMOS PGAがあります。フレキシブルなアナログフロントエンド(AFE)は、RTDの直接測定に最適な2つのセンサ励弧電流源を組み込んでいます(図9)。

図9:10チャンネルアナログ入力マルチプレクサを備えたADS1262およびADS1263 32ビットΔƩ ADC のブロック図。ADS1263には、2番目のオンチップ24ビットΔƩ ADCがあります。(画像提供:Texas Instruments)

図9:10チャンネルアナログ入力マルチプレクサを備えたADS1262およびADS1263 32ビットΔƩ ADC のブロック図。ADS1263には、2番目のオンチップ24ビットΔƩ ADCがあります。(画像提供:Texas Instruments)

ADS1235と同様に、PGAゲイン、データレート、デジタルフィルタモード、およびチョップモードは、ADS1262/63のノイズ性能に影響を与える重要な要素です。32ビット分解能により、ADS1262/63は真に低ノイズの深度機能を提供します。

初めに、安定した4次変調器およびsinc1からsinc4のフィルタは、32ビットの有効分解能と24ビットのノイズフリー分解能を生成します。低周波数、2.5SPSのデータレート、および1V/VのPGAゲイン(バイパス)を構成することにより、5Vシステムにおけるsinc3デジタル出力のコンバータノイズは0.08mVRMS(0.307mVPP)になります。このデバイスは、26.9ビットの有効分解能と25ビットのノイズフリー分解能を上回ります。この32ビットシステムにおいて、理論的SNRは387dBであり、実際のSNRは164dBです。

24ビットおよび32ビットコンバータのノイズ間の違いは明確で、32ビットΔƩ ADCの低ノイズ機能は24ビットΔƩ ADCの機能を上回ります(表2)。

*注:SNR = 6.02N + 1.76(Nはビット数)

|

表2:フルスケール入力電圧5VにおけるADC RMSノイズ、ピーク-ピークノイズ、およびSNRの比較。(データ提供:DigiKey)

結論

ΔƩ ADCは、継続的な機能追加により、低ノイズの限界を引き続き押し広げています。この記事では、デジタルに近いこの低ノイズADCがどのように温度、圧力、およびロードセルのアプリケーションに直接マッピングするかを示しました。高精度24ビットΔƩ ADCおよび32ビットΔƩ ADCの基本的説明では、超高精度特性の実現に向けた道筋を概説しました。

免責条項:このウェブサイト上で、さまざまな著者および/またはフォーラム参加者によって表明された意見、信念や視点は、DigiKeyの意見、信念および視点またはDigiKeyの公式な方針を必ずしも反映するものではありません。