アナログの基礎 - パート5:SAR ADCの難しい入力駆動問題への取り組み

DigiKeyの北米担当編集者の提供

2020-10-28

編集部注:A/Dコンバータ(ADC)はアナログをデジタルの世界に接続するデバイスであり、現実世界に接続するあらゆる電子システムの基本的なコンポーネントでもあります。またこれは、システムのパフォーマンスを決定する重要な要素にもなります。このシリーズでは、ADCの基礎から各種タイプ、さらにはADCのアプリケーションについて解説します。アナログの基礎シリーズのパート1では、SAR ADCについて説明します。パート2では、デルタシグマコンバータについて説明します。パート3では、パイプラインADCについて検討します。パート4では、デルタシグマADCがどのようにして超低ノイズの結果を得ることができるかを紹介します。このパート5では、SAR ADCにとって難しい入力駆動の問題を探ります。

多くのデータ収集、産業制御、計装アプリケーションでは、逐次比較レジスタ(SAR)コンバータが最適な場合、超高速アナログ/デジタルコンバータ(ADC)が必要になります。ただし、変換を成功させるには、SARコンバータ周辺の外部回路も課題に対応することを確認しておくことが重要です。SARコンバータで特に注意が必要な端子は、アナログ信号の入力端子です。この入力端子を放置しておくと、安定性の問題や容量性電荷の「キックバック」を引き起こし、不正確な変換や信号収集時間の延長につながる可能性があります。

SARコンバータアプリケーションの正確な入力信号制御ソリューションは、オペアンプの駆動にあります。これらのデバイスは、適切な出力抵抗とコンデンサの値によってサポートされており、高分解能、16ビットおよび20ビットのSARコンバータシステム向けの高精度で堅牢なソリューションの基盤となります。

この記事では、安定した正確なSAR ADC変換を実現するための問題点について簡単に説明します。また、SAR ADCを駆動するための適切なオペアンプを紹介し、必要な入力ドライバ回路を実装する方法を示します。そして、Analog Devicesのソリューションを例に挙げて説明します。

SAR ADC入力回路

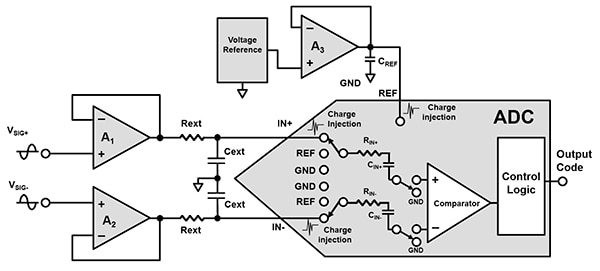

SAR ADCドライバ回路には、ADCを信号源から分離するオペアンプ(A1およびA2)があります(図1)。この回路では、Rextはアンプの出力段をADCの容量性負荷(CIN+およびCIN-)とCextから「絶縁」することで、アンプを安定に保ちます。CextとCREFは、IN+、IN-、REF入力端子からのスイッチング電荷注入を吸収するADCへのほぼ完全な入力ソースを提供します。入力端子(IN+、IN-)はコンバータの取り込み時間中に入力信号(VSIG+、VSIG-)の電圧を追跡し、ADCの入力サンプリングコンデンサCIN+とCIN-に電荷を供給します。

図1:この回路では、Rextはオペアンプ出力段からCextを「絶縁」しています。CextとCREFは、サンプリング期間中に差動SAR ADC用の電荷リザーバを提供します。(画像提供:DigiKey)

図1:この回路では、Rextはオペアンプ出力段からCextを「絶縁」しています。CextとCREFは、サンプリング期間中に差動SAR ADC用の電荷リザーバを提供します。(画像提供:DigiKey)

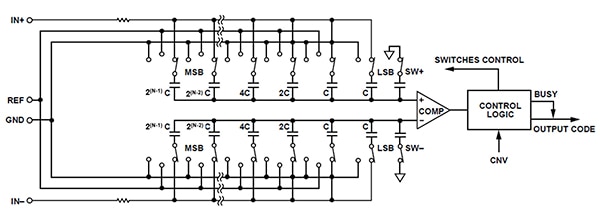

Analog DeviceのAD7915(16ビット)とAD4021(20ビット)SAR ADCを例にADCの内部を見てみると、電荷再分配型のデジタルアナログコンバータ(DAC)を使用していることがわかります。静電容量式DACは、2つの同一アレイのバイナリ加重コンデンサを搭載しています。これらのアレイは、非反転および反転コンパレータ入力に接続されています(図2)。

図2:SAR ADCの簡略化されたAD7915およびAD4021ベースの回路図。ここでNは、コンバータのビット数に等しくなります。(画像提供:DigiKey。Analog Devices提供の原資料に手を加えたもの)

図2:SAR ADCの簡略化されたAD7915およびAD4021ベースの回路図。ここでNは、コンバータのビット数に等しくなります。(画像提供:DigiKey。Analog Devices提供の原資料に手を加えたもの)

収集フェーズの間、入力(IN+およびIN-)は容量性アレイに切り替わります。さらに、SW+とSW-が閉じ、最下位ビット(LSB)のコンデンサをグランド(GND)に接続します。この状態では、コンデンサアレイがサンプリングコンデンサとなり、IN+およびIN-のアナログ信号を取得します。収集フェーズが完了すると、制御ロジック(右側)へのCNV入力がハイレベルになり、変換フェーズが開始されます。

変換フェーズは、SW+とSW-を開き、2つのコンデンサアレイをGNDに切り替えることから始まります。この構成では、キャプチャされたIN+とIN-の差動電圧により、コンパレータが不平衡になります。電荷再配分DACは、コンデンサアレイの各エレメントを最上位ビット(MSB)から最下位ビット(LSB)に、GNDとREFの間で系統的に切り替えます。コンパレータ入力は、バイナリ加重電圧ステップ(VREF/2N-1、VREF/2N-2、...、VREF/4、VREF/2)によって異なります。制御ロジックはスイッチをMSBからLSBに切り替え、コンパレータを平衡状態に戻します。このプロセスが完了すると、ADCは収集フェーズに戻り、制御ロジックはADC出力コードを生成します。

入力電荷注入、回路の安定性、AD7915 ADCの駆動

変換プロセスの重要な部分は、正確な入力信号電圧を取得することです。ADCデータ変換プロセスは、ADC収集時間の終わりまで安定性を維持しながら、駆動アンプが入力コンデンサCIN+およびCIN-を正確に充電することでスムーズに実行されます。設計者にとっての問題は、ADCの入力端子には、駆動アンプが管理する「キックバック」電荷注入またはスイッチングノイズに加えて静電容量(CIN+、CIN-)が入ってくることです。

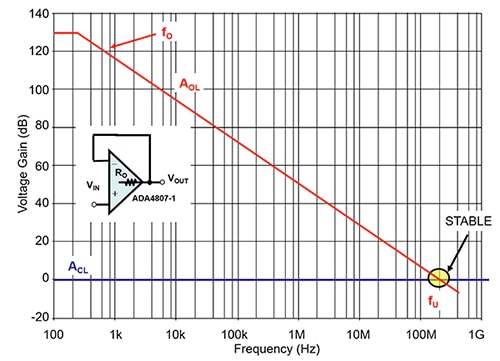

アンプ回路のボード線図は、回路の安定性を素早く推定します。ボード線図ツールは、アンプの開ループとシステムの閉ループのゲイン伝達関数の大きさを近似します(図3)。

図3:図1のアンプの開ループと閉ループの伝達相関関係は、アンプ負荷としてRextおよびCextを用いず、続くSAR ADCを用いた場合のものです。(画像提供:DigiKey)

図3:図1のアンプの開ループと閉ループの伝達相関関係は、アンプ負荷としてRextおよびCextを用いず、続くSAR ADCを用いた場合のものです。(画像提供:DigiKey)

y軸では、増幅回路のアンプの開ループゲイン(AOL)と閉ループゲイン(ACL)を定量化してます。ここで、増幅器のAOL曲線は130dBで始まり、閉ループゲインACLは0dBに等しくなっています。x軸に沿った単位は、100ヘルツ(Hz)から1ギガヘルツ(GHz)までの開ループと閉ループのゲイン周波数を対数的に定量化します。

図3では、約220Hz(fO)におけるアンプのDC開ループゲインは、-20dB/decadeの速度で130dBから下降していきます。周波数が高くなるにつれて、この減衰率は約180メガヘルツ(MHz)で0dBを超えて継続します。この曲線は単極システムを表しているので、クロスオーバー周波数fUは、ユニティゲイン安定増幅器のゲイン帯域幅積(GBWP)に等しくなります。このプロットは、AOLとACLの閉塞率が20dB/decadeであるため、安定したシステムを表しています。

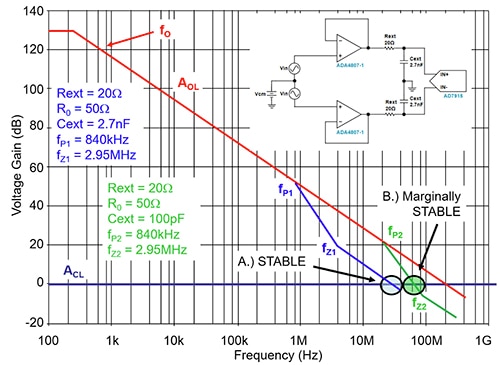

RextとCextおよびSAR ADCを加えることで、システムのゼロ点と極が作成され、増幅器回路が変更されます(図4)。このシステムは、16ビット、1メガサンプル/秒(MSPS)のAD7915差動PulSAR ADCと、180MHzレールツーレール入出力ADA4807-1アンプで構成されており、どちらもAnalog Devices製です。アンプとADCの組み合わせでは、ADC入力容量負荷が30ピコファラッド(pF)(標準)のため、Rextが必要になります。この回路では、Cextが充電バケットとして機能し、ADC入力に十分な電荷を供給して入力電圧に正確に一致させる必要もあります。

図4:2つの別々のRext/CextペアでAD7915 SAR ADCを駆動する2つのADA4807オペアンプのボード線図応答を示しています。fP1とfZ1のコーナー周波数は、アンプの開ループゲインを変更し、安定したシステム応答を実現します。fP2とfZ2のコーナー周波数は、アンプの開ループゲインを変更し、わずかに安定した応答を実現します。(画像提供:DigiKey)

図4:2つの別々のRext/CextペアでAD7915 SAR ADCを駆動する2つのADA4807オペアンプのボード線図応答を示しています。fP1とfZ1のコーナー周波数は、アンプの開ループゲインを変更し、安定したシステム応答を実現します。fP2とfZ2のコーナー周波数は、アンプの開ループゲインを変更し、わずかに安定した応答を実現します。(画像提供:DigiKey)

図4の回路は、初期収集時にADCの容量性負荷とADCのスイッチング電荷注入により、発振する可能性があります。Rext/Cextアンプの出力コンポーネントによって生成される追加の極とゼロ点がシステムの安定性を確保しているため、開ループと閉ループのゲイン曲線の交点は20dB/decade以上となり、位相マージンは45°以下になります。fP2とfZ2を使用したこの構成では、不安定な回路になります。

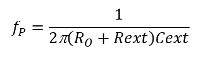

不安定性を防ぐために、回路内にRextとCextを使用してアンプの開ループゲイン曲線を評価する場合、設計者はアンプの開ループ出力抵抗ROの影響を考慮する必要があります。50Ω(W)に等しいRO、Rext、およびCextの組み合わせは、1つの極(fP、式1)と1つのゼロ(fZ、式2)を導入することにより、開ループ応答曲線を変更します。値RO、Rext、およびCextは、fPのコーナー周波数を決定します.RextとCextの値は、ゼロコーナー周波数fZを決定します。

式1

式1

式2

式2

fPとfZの計算は次のとおりです。

fP1 = 842kHz

fZ1 = 2.95MHz

この場合: RO = 50W

Rext = 20W

Cext = 2.7nF

fP2 = 22.7MHz

fZ2 = 79.5MHz

この場合: RO = 50W

Rext = 20W

Cext = 0.1nF

上記のfP1とfZ1の値は、AD7915およびADA4807-1に安定したシステムを提供します。

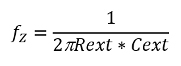

Easy Drive AD4021 SAR ADCの駆動

AD7915の代替品として、AD4021 20ビット1MSPS Easy Drive SARコンバータがあります。AD4021デバイスファミリは、入力キックバックと入力電流を0.5マイクロアンペア(μA)/MSPSまで大幅に低減します。Easy Driveの特長は、消費電力とシグナルチェーンの複雑さを低減したことです。

AD4021のアナログ入力には、標準的なスイッチドキャパシタSAR入力の非線形電荷キックバックを低減する回路が搭載されています。キックバックを低減し、収集フェーズを長くすることで、より低帯域幅でより低電力のドライバアンプを使用することができます(図5)。

図5:AD4021の入力回路と収集タイミングにより、キックバックスイッチング電流が減少し、ドライバアンプの厳しい要件が緩和されます。(画像提供:Analog Devices)

図5:AD4021の入力回路と収集タイミングにより、キックバックスイッチング電流が減少し、ドライバアンプの厳しい要件が緩和されます。(画像提供:Analog Devices)

キックバックの低減と長い収集時間の組み合わせにより、入力抵抗-コンデンサ(RC)フィルタのRext抵抗値を大きくし、それに対応するCextコンデンサを小さくすることもできます。このように、小型のCextアンプ負荷を組み合わせることで、安定性が向上し、消費電力を抑えることができます。

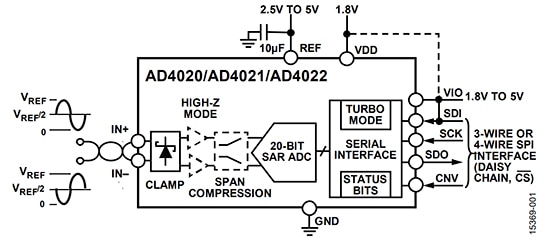

単一の5V電源を使用するAD4021の推奨接続図は、同様の回路図を持っているように見えます。ただし、アンプの要件は緩和されており、Rext/Cext(RとC)の値は小さくなっています(図6)。

図6:前述のAD7915の駆動と比較して、より緩和されたアンプ要件とより大きなRext値を備えた、単一5V電源で駆動されるAD4021およびADA4807-1の典型的な応用図。(画像提供:Analog Devices)

図6:前述のAD7915の駆動と比較して、より緩和されたアンプ要件とより大きなRext値を備えた、単一5V電源で駆動されるAD4021およびADA4807-1の典型的な応用図。(画像提供:Analog Devices)

図6では、SARベースのAD4021も電荷再分配サンプリングDACを使用しています。ADCには、オンボードの変換クロックとシリアルクロックがあります。そのため、変換処理には同期クロック(SCK)入力は必要ありません。このようなクロック構成にすることで、収集時間の延長が可能になり、入力信号が最終値に落ち着くまでの時間を長くすることができるため精度が向上します。

AD7915とAD4021の両方のドライブアンプの主な考慮点はノイズです。アンプ/Rext/Cextの組み合わせは、AD7915ではフルスケールステップから16ビットレベル(0.0015%、15ppm)に、AD4021では20ビットレベル(0.00001%、1ppm)に落ち着く必要があるためです。

AD7915およびAD4021の信号対雑音(SNR)性能を維持するには、ドライバアンプのノイズがADCのノイズの3分の11 以下でなければなりません。AD4021のノイズは60マイクロボルトrms(mVrms)であり、アンプ/Rext/Cextの組み合わせは20mVrms未満である必要があります。AD4021のノイズは31.5mVrmsなので、アンプ/Rext/Cextの組み合わせは10.5mVrms未満にする必要があります。

Analog Devicesの精密ADCドライバツールは、設計者が正しいRextとCextの値を素早く計算するのに役立ちます。選択されたドライバとADCを使用して、このツールは回路の整定時間、ノイズ、歪みの動作をモデル化します。

まとめ

SAR ADCは、超高速データ収集、産業用制御、計装アプリケーションの分野で圧倒的なシェアを占め続けています。しかし、これらのデバイスの外部入力回路(駆動アンプと入力フィルタ)は、潜在的なスイッチング電荷注入とアンプの安定性の問題に対応するために特別な配慮が必要です。

AD7916やAD4021などの大半のSARコンバータの正確な入力信号制御のソリューションは、オペアンプドライバ(この場合はADA4807-1)にあります。これまでに述べたように、これらのデバイスは、適切な出力抵抗とコンデンサの値によってサポートされており、高精度、堅牢、高分解能、16ビットまたは20ビットのSARコンバータシステムを構築するための強固な基盤を形成します。

免責条項:このウェブサイト上で、さまざまな著者および/またはフォーラム参加者によって表明された意見、信念や視点は、DigiKeyの意見、信念および視点またはDigiKeyの公式な方針を必ずしも反映するものではありません。