アナログの基礎 - パート1:SAR A/Dコンバータ

DigiKeyの北米担当編集者の提供

2020-04-15

編集前記:A/Dコンバータ(ADC)はアナログをデジタルの世界に接続するデバイスであり、現実の世界に接続する電子システムの基本的なコンポーネントです。またこれは、システムのパフォーマンスを決定する重要な要素にもなります。このシリーズでは、ADCの基礎から各種タイプ、さらにはADCのアプリケーションについて解説します。アナログの基礎シリーズのパート1では、逐次比較レジスタ(SAR)ADCについて説明します。パート2では、デルタシグマ(ΔƩ)コンバータを取り上げます。パート3では、パイプラインADCについて検討します。パート4では、デルタシグマADCがどのようにして超低ノイズの結果を得ることができるかを紹介します。パート5では、SAR ADCの難しい入力駆動の問題を探ります。

センスした情報データは、そのままではアナログ領域のものなので、それをデジタル領域に取り込むにはある種の置き換えを行う必要があります。その大仕事の主役となるのが、A/Dコンバータ(ADC)です。長年にわたってADCトポロジとしての定評を獲得してきたのが、逐次比較レジスタ(SAR)、デルタシグマ、そしてパイプラインという3種類のADCです。これらのADCトポロジは、3種類それぞれに大きな差異があることで各種の周波数範囲で動作し、低周波数のセンサアプリケーションからより高周波数のLiDARや衛星通信まで、あらゆる用途に対応します。

SAR ADCは、最初に主流となったコンバータでした。このコンバータトポロジはこれまでに、プロセス制御、医療、初期のデジタルオーディオシステムなど、さまざまなアプリケーションに採用されてきました。これらのアプリケーションは、8ビットから20ビットのSAR ADCの出力変換範囲から恩恵を受けます。ただし、SAR ADCが優れているのは、アナログ入力信号のスナップショットをキャプチャし、多数の信号スナップショットを使用して時系列で全体像を示す点にあります。

この記事では、SAR ADCを取り巻く信号チェーンについて概説します。そこから、ADCのスナップショット動作で重要な役割を果たす基礎的な入力段を分析することで、このADCトポロジについて掘り下げます。次にSAR ADCソリューションの例として、Analog DevicesのAD7625BCPZとAD4020BCPZ-RL7を紹介し、ADC4020BCPZ-RL7の内部にあるA/D変換の仕組みに焦点をあてます。また、最適なデータ収集システムの主な仕様についても紹介します。

SAR ADCのアナログ信号チェーン

SAR ADCは、自動テスト機器、マシンオートメーション、医療機器、精密なデータ収集などのシステムに採用されています。どのSAR ADC用途にも、中庸の8~20ビット分解能のデジタル式表現を必要とするアナログ信号が存在し、サンプリングはほぼDC~15Mサンプル/秒(MSPS)で行われます(本記事の執筆時において)。

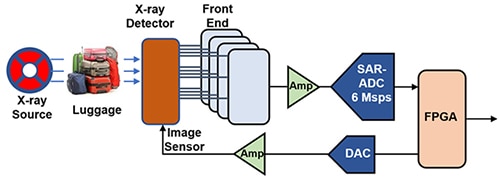

SAR ADCは、アナログフロントエンド(AFE)信号チェーンがなくとも十分に機能します。しかし、SAR ADCのフロントエンドに適切な信号をもたらすことも設計者の役割であれば、ある程度の信号調整が必要になると考えられます(図1)。

図1:このSAR ADC信号チェーンの例には、X線検出器、AFE、アンプドライバ、Analog DevicesのAD7625BCPZコンバータ(6MSPS)、変換結果用のデジタルレセプタクル(FPGA)が含まれています。(画像提供:DigiKey)

図1:このSAR ADC信号チェーンの例には、X線検出器、AFE、アンプドライバ、Analog DevicesのAD7625BCPZコンバータ(6MSPS)、変換結果用のデジタルレセプタクル(FPGA)が含まれています。(画像提供:DigiKey)

上図では、X線源が手荷物を通してX線検出器に信号を送ります。X線検出機器の役割は、手荷物の完全な画像を短時間で構成し、旅行者を待たせないようにすることです。

フロントエンドはX線検出器の信号を受け取り、信号調整機能としてアナログゲインやレベルシフトなどを実行します。さらに、その信号がSAR ADC(この例ではAnalog DevicesのAD7625BCPZ)に送られます。

SAR ADCの前にあるアンプによって適切な安定化を図り、通常はアンプとSAR ADCの間に1次ローパスフィルタを使用します。このSAR ADCは最大6MSPS(167nsごとに1サンプル)でサンプリングを行い、短期間で多数のスナップショットに適合します。

SAR ADC入力段のコアの簡素化

SAR ADCはさまざまな機能拡張や強化を経てきましたが、いずれの場合も、変換期間中の主な動作は電荷再分配であり、これは逐次比較ADCの最も一般的な方式の1つでもあります。またSAR ADCには、S-Dやパイプラインのコンバータとは異なり、待ち時間ゼロ(ゼロレイテンシ)というさらなる利点があります。

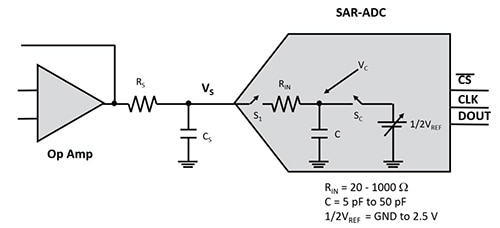

端的に言うと、信号スナップショットが生じる場所は容易にわかります。SAR ADCの入力コアには、入力信号収集スイッチ(S1)、容量性アレイ、変換スイッチ(SC)、そして内部基準電圧(½VREF)が含まれます(図2)。

図2:出力安定化フィルタを備えSAR ADCを駆動するオペアンプ。(画像提供:DigiKey)

図2:出力安定化フィルタを備えSAR ADCを駆動するオペアンプ。(画像提供:DigiKey)

SAR ADCコアの動作は次のとおりです。

- S1が開き、SCが閉じます。これにより、入力段がアナログ信号ソースから遮断されます。

- Cの電荷が½VREFによって再較正されます。この再較正で、SAR ADCがゼロに戻ります。

- 次にS1が閉じ、SCが開きます。これでデバイスが入力アナログ信号に接続されます。

- SAR ADCが入力信号VSをあらかじめ規定された収集期間で収集します。この収集期間では、S1およびSCのスイッチングノイズ、およびアンプがコンデンサ負荷やスイッチングノイズに突然さらされることを許容します。

- 次にS1が開きます。このとき、信号スナップショットが生じます。

- SAR ADCは、VCで信号をデジタル式の表現に変換します。これを実行する所要時間が「変換時間」です。

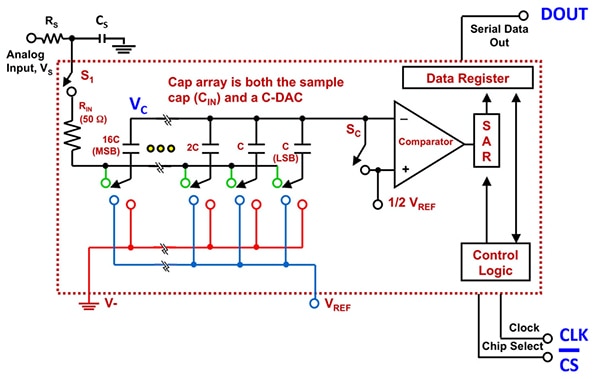

SAR ADC入力段のコアの詳細

変換コアでは、VCでキャプチャした信号の電荷再分配が行われます。コンバータの電荷再分配のオーケストレーションはこのコア内で行われ、クロックによりゲート制御されます。このプロセスから、一定周期による個々のデジタル出力コードがSAR ADCのDOUT出力に到達します(図3)。

図3:4ビットSAR ADCの内部には、デジタル重み付けコンデンサの完全なアレイ、すなわち16C、8C、4C、2C、および2つのCが含まれます。(画像提供:DigiKey)

図3:4ビットSAR ADCの内部には、デジタル重み付けコンデンサの完全なアレイ、すなわち16C、8C、4C、2C、および2つのCが含まれます。(画像提供:DigiKey)

変換時の最初のステップとして、SAR ADCアルゴリズムが最上位ビット(MSB)を判定します。SAR ADCは、16Cコンデンサ下部でのV-およびVREFコンパレータ入力のスイッチングにより、½VREFと比較した信号の大きさのテストを開始します。一連のSAR ADC変換動作での以降の比較は、½VREFに対して8Cをテスト(図では非表示)、次に4Cをテストのように続きます。

SAR ADC出力変換の詳細

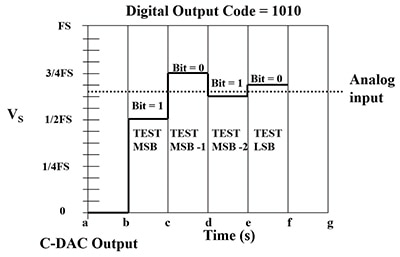

MSBの判定がDOUTピンを介してすぐに送信され、MSB 1の判定の間にMSBスイッチは停止したままになります。SAR ADCは、最下位ビット(LSB)が最後に決まるまで、このアルゴリズムを実行します(図4)。

図4:4ビットSAR ADCは、一定周期で変換アルゴリズムを実行してビット判定を行い、DOUTピン(図3を参照)を通じてそれらの判定を送信します。(画像提供:DigiKey)

図4:4ビットSAR ADCは、一定周期で変換アルゴリズムを実行してビット判定を行い、DOUTピン(図3を参照)を通じてそれらの判定を送信します。(画像提供:DigiKey)

図4に、SAR ADCでMSBからLSBまでのビット判定が一定周期で行われる動作を示します。すべての変換データは、図3の右上にあるDOUTを介して連続的に即座に送出されます。フルスループット時間に標準で必要なのは、信号収集の十分な時間とビットごとのクロックサイクルです。

SAR ADC変換の課題

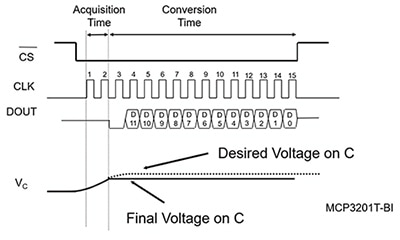

設計者は、変換から正しいアナログ値を確実にキャプチャするために必要な、信号セトリング時間の長さに留意する必要があります(図5)。

図5:12ビットSAR DACの変換タイミング図。完全な変換ごとに16のクロックが必要になります。(画像提供:DigiKey)

図5:12ビットSAR DACの変換タイミング図。完全な変換ごとに16のクロックが必要になります。(画像提供:DigiKey)

図5では、コンバータの入力スイッチが開くまでに、入力信号VCが最終的な目的の電圧に達していません。この例では、回路設計者がアンプ入力信号のセトリング時間の計算を間違えています。

20ビット、1.8MSPSのAD4020BCPZ-RL7 SAR ADCは、信号収集フェーズを拡張しながらスループットレートを維持することで、信号収集の複雑さを緩和します。このデバイスでは、低信号対ノイズ比(SNR)が100.5dBと低く抑えられています。

SAR ADC伝達関数

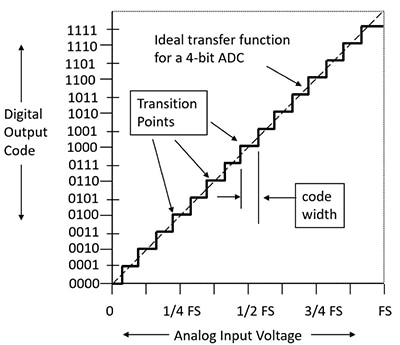

ADCの考えられるコード数は、2N(Nはビット数)に等しくなります。たとえば4ビットコンバータでは、コード数は24、つまり16になります(図6)。

図6:デジタル出力コード(縦軸)とアナログ入力電圧(横軸)のグラフで表される、理想的な4ビットSAR ADCの伝達関数は、直線になります。(画像提供:DigiKey)

図6:デジタル出力コード(縦軸)とアナログ入力電圧(横軸)のグラフで表される、理想的な4ビットSAR ADCの伝達関数は、直線になります。(画像提供:DigiKey)

画像の生成

SAR ADCのスループットレートには、Analog DevicesのAD4020BCPZ-RL7で可能な20ビット分解能で最大1.8MSPSのスループットレートを達成するような、収集時間と変換時間も含まれています。AD4020BCPZ-RL7のスループット速度があれば、多数のスナップショットを収集し、マシンオートメーションや医療機器向けのデジタル画像レンダリングソリューションを作成することもできます。

結論

プロセス制御から医療および民生向けまで幅広いアプリケーションで使用されるSAR ADCは、その信号スナップショット機能と向上し続ける分解能および速度によって真価が実証され続けています。現時点でSAR ADCの分解能は8~20ビットに及び、スループットレートは最大15MSPSを発揮します。その一例として、Analog DevicesのAD4020BCPZ-RLは、低ノイズ、高速処理、および20ビット、1.8MSPSの精度を提供します。しかし、SAR ADCコンバータのアーキテクチャはこれで終わりというわけではありません。

免責条項:このウェブサイト上で、さまざまな著者および/またはフォーラム参加者によって表明された意見、信念や視点は、DigiKeyの意見、信念および視点またはDigiKeyの公式な方針を必ずしも反映するものではありません。