アナログの基礎 - パート2:デルタシグマ(ΔƩ)ADCとそのデジタル機能の活用法

DigiKeyの北米担当編集者の提供

2020-05-14

編集前記:A/Dコンバータ(ADC)はアナログをデジタルの世界に接続するデバイスであり、現実の世界に接続する電子システムの基本的なコンポーネントです。またこれは、システムのパフォーマンスを決定する重要な要素にもなります。このシリーズでは、ADCの基礎から各種タイプ、さらにはADCのアプリケーションについて解説します。アナログの基礎シリーズのパート1では、SAR ADCについて説明しました。このパート2では、デルタシグマ(ΔƩ)コンバータを取り上げます。パート3では、パイプラインADCについて検討します。パート4では、デルタシグマADCがどのようにして超低ノイズの結果を得ることができるかを紹介します。パート5では、SAR ADCにとって難しい入力駆動の問題を探ります。.

パート1で説明した逐次比較レジスタ(SAR)A/Dコンバータ(ADC)と同様に、高精度なアナログセンサ信号チェーン(すべてSAR-ADCに供給する複数のゲイン、信号コンディショニング、および複雑なアナログフィルタ段)への挑戦は、アナログの失敗につながる可能性があります。設計者は、結果的に高価な高密度プリント基板ソリューションに落ち着く可能性もあります。

さらに、超低センサ信号を初めとして、信号チェーンの各アナログ段の出力は、コンバータのデジタル出力で低い信号対ノイズ比(SNR)および高い歪みエラーとして現れるエラーをもたらします。このようなシステムの設計者は、一歩下がって、高精度センサADCのパラダイムを再考する必要があります。

高精度センサシステムに関連した問題の解決策は、小さなセンサ信号を迅速にデジタル化し、ゲインおよびフィルタリングのノイズがあるアナログ機能をデジタルで実装するADCトポロジを選択することです。これが、デルタシグマ(ΔƩ)ADCの役割です。

この記事では、例としてAnalog DevicesのAD4110-1ユニバーサル入力A/Dフロントエンドを使用して、ΔƩ ADCおよび内部A/D変換メカニズムの基本的機能を手短に説明します。そこから、周囲の信号チェーンを詳細に調べ、適切なデータ収集システムの重要な仕様を提供します。

ΔƩ ADCの構造

今世紀が始まる少し前に、ΔƩ ADCはアナログの主役に躍り出ました。デルタシグマの先進技術の採用拡大により、主要なアナログ信号および計算プロセスは、デジタルドメイン内で行われるようになりました。ΔƩ ADC集積回路(IC)についての調査によると、シリコン面積の80%以上がデジタル機能を実行しています。圧倒的にデジタル化された回路の副産物は、堅牢性と小さなフットプリントです。

なぜそれが可能になったのでしょうか?それは、低電圧アナログ信号の直接的なデジタル化に始まります。デジタルドメインでは、デジタル回路によって必要なゲイン機能も実行しつつ、アナログフィルタリングをほぼ完全に置き換えることができます(図1)。また、デジタル回路は、各半導体のプロセスノードとともに収縮します。

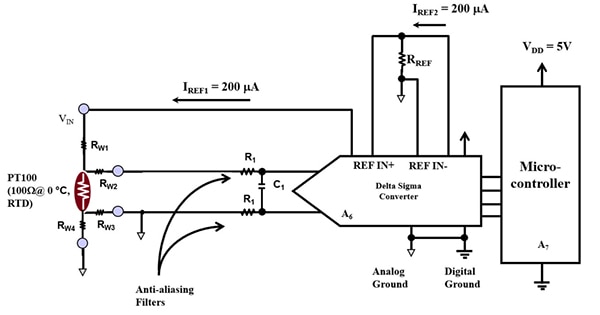

図1:デルタシグマには、フィルタリングとゲインに必要な回路のほぼすべてが含まれます。この例では、ΔƩ ADCが小さな抵抗温度検出器(RTD)の電圧を感知およびデジタル化します。それから、内部デジタル信号ゲインおよびフィルタリングを使用して、低ノイズ24ビットのデジタル結果を提供します。(画像提供:A Baker’s Dozen)

図1:デルタシグマには、フィルタリングとゲインに必要な回路のほぼすべてが含まれます。この例では、ΔƩ ADCが小さな抵抗温度検出器(RTD)の電圧を感知およびデジタル化します。それから、内部デジタル信号ゲインおよびフィルタリングを使用して、低ノイズ24ビットのデジタル結果を提供します。(画像提供:A Baker’s Dozen)

図1で、24ビットΔƩ ADCシステムは、アナログ入力、中央デジタルエンジン、およびデジタルI/O端子で構成されています。コンバータは低電圧RTD信号を取得し、デジタルフィルタリングを通して、アナログ入力の完全な24ビットデジタル表現を生成します。アナログゲインブロック(通常はSAR-ADC回路で優勢)はここに存在せず、唯一のアナログフィルタはR1とC1の組み合わせです。そうです、これがシンプルで低コストの一次フィルタです。

ΔƩ ADCの仕組み

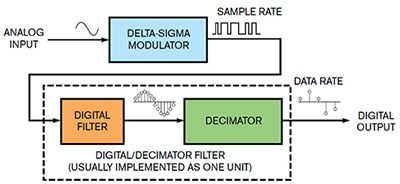

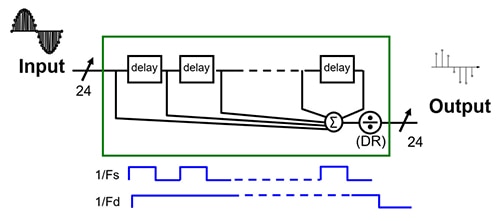

ΔƩ ADCの基本的なトポロジには、デジタルフィルタと直列に接続されたΔƩ変調器があります。この基本的なトポロジ以外にも、ほとんどのΔƩ ADCには他のさまざまな機能があります。一方、すべてのデルタシグマコンバータにこの不可欠なコアがあります(図2)。

図2:基本構成として、すべてのΔƩ ADCには、ΔƩ変調器、デジタルフィルタ、およびデシメータがあります。(画像提供:EDN)

図2:基本構成として、すべてのΔƩ ADCには、ΔƩ変調器、デジタルフィルタ、およびデシメータがあります。(画像提供:EDN)

図2で、入力は正弦波またはDCになります。この説明では正弦波入力に焦点を当てます。ΔƩ変調器は、シングルサイクルの正弦波を1ビットストリームにデジタル化します。ΔƩ変調器の出力サンプル周波数はFsです。1ビット変調器による変換には高い量子化ノイズがあるように見えますが、実際には信号ノイズが高周波へと「成形」されます。これにより、デジタルフィルタの出力で低ノイズ、高分解能の変換が可能になります。

変調器の出力において、デジタルフィルタはΔƩ変調器の1ビット結果を蓄積し、フィルタ計算を実行します。デジタルフィルタ出力信号は、出力周波数Fsを継続しながらアナログ入力信号をデジタルに反映します。この信号は、デジタルドメインのみに存在するようになります。デジタルローパスフィルタ(またはデシメーションフィルタ)は、高周波数ノイズを減衰し、出力データレート(1/Fd)を減速させます。デジタル/デシメータフィルタは、変調器の1ビットコードストリームをサンプリングし、低速のマルチビットコードへフィルタリングします。

ほとんどのコンバータには1つのサンプルレートしかありませんが、デルタシグマコンバータには入力サンプリング周波数(Fs)と出力データ周波数(Fd)という2つのサンプルレートがあります。これら2つの周波数変数の比は、式1により、システムのデシメーション比(DR)を定義します。

![]() 式1

式1

ΔƩ変調器

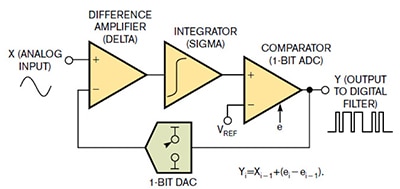

ΔƩ変調器は、1ビットコードのストリームを生成することにより、実際のA/D変換を実行します。このプロセスは差動アンプで開始します(図3)。

図3:ΔƩ ADC変調器の入力段は、アナログ入力とフィードバックDAC間のデルタを感知します。第2段では、アナログ信号上に積分器機能またはシグマを実装します。(画像提供:EDN)

図3:ΔƩ ADC変調器の入力段は、アナログ入力とフィードバックDAC間のデルタを感知します。第2段では、アナログ信号上に積分器機能またはシグマを実装します。(画像提供:EDN)

図3で、差動アンプ(デルタ)は積分器(シグマ)にアナログ信号を送信します。積分器の出力において、コンパレータは非常に高いサンプルレート(1/Fs)で積分器の出力と基準電源(VREF)を区別します。さらに、コンパレータは1ビットD/Aコンバータ(DAC)に1ビットストリームを提供します。次に、変調器はアナログ入力信号とフィードバックDACのアナログ出力の差を測定します。

ΔƩ変調器は、積分器とDACフィードバックループの働きにより、ノイズを高周波数へ成形します。図3の数式(右下)は、伝達方程式をYi = Xi-1 +(ei – ei-1)として示しています。変調器は、量子化ノイズ(ei)により、入力信号(Xi)を1ビット出力コード(Yi)にデジタル化します。厳密に言えば、変調器の出力(Yi)は、入力(Xi-1)に量子化ノイズ(ei – ei-1)を加えたものと等しくなります。この数式は、量子化ノイズを、現在の誤差(ei)から変調器の以前の誤差(ei-1)を差し引いたものとして示しています。

デジタルおよびデシメーションフィルタ

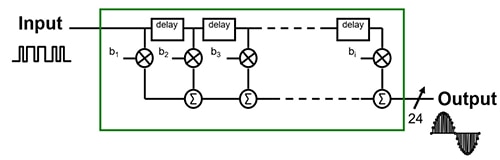

平均化は、デジタルフィルタリングの一形態であり、低速の産業用ΔƩ ADCで一般的です。ほぼすべての産業用ΔƩ ADCは、直線位相の有限インパルス応答(FIR)を使用するsincフィルタと呼ばれる平均化フィルタのクラスを組み込んでいます。このフィルタは、デジタルローパスフィルタです(図4)。

図4:この平均化FIRデジタルフィルタの係数(bx)は、すべて1に等しくなります。(画像提供:DigiKey)

図4:この平均化FIRデジタルフィルタの係数(bx)は、すべて1に等しくなります。(画像提供:DigiKey)

図4で、変調器の出力ビットストリームはこのデジタルフィルタへの入力になり、変調器のサンプリングクロックが遅延タイミングを決定します。図4に示すFIRフィルタの係数(bx)は、すべて1に等しくなります。この平均化アルゴリズムにより、FIRデジタルフィルタは、図3のアナログ入力の低ノイズ24ビットデジタル表現を生成します。サンプルは変調器のサンプルレート(1/Fs)で発生します。それから、デシメーションフィルタはDRを使用して出力データレートを低減します。

「デシメーション」という語は、不必要な兵士を系統的に排除する軍事行為に関連しています。デジタルエレクトロニクスにおけるデシメーションも、DRによりデジタル信号の出力データレート(1/Fd)を低減するという同じ概念に基づいています。これを実行するための迅速かつデジタルな方法は、デジタルフィルタの出力サンプルの一部を系統的に廃棄することです(図5)。

図5:デシメーションプロセスは、サンプルレート(1/Fs)で割った出力データレート(1/Fd、画像の下)の因数により、デジタル24ビット出力の数を系統的に削減します。(画像提供:DigiKey)

図5:デシメーションプロセスは、サンプルレート(1/Fs)で割った出力データレート(1/Fd、画像の下)の因数により、デジタル24ビット出力の数を系統的に削減します。(画像提供:DigiKey)

図5のデシメーションプロセスは、式1により、DRで出力データレート(1/Fd)をデシメートします。

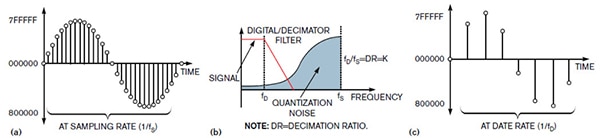

デジタルおよびデシメーションフィルタを介したイベントが、ΔƩ ADCノイズを効果的に低減します(図6)。

図6:ここには、時間領域内のデジタルフィルタ出力(a)、デシメーションフィルタのローパス機能でスーパーインポーズされた変調器ノイズが成形した出力(b)、および時間領域内のデシメータの出力信号(c)が示されています。(画像提供:EDN)

図6:ここには、時間領域内のデジタルフィルタ出力(a)、デシメーションフィルタのローパス機能でスーパーインポーズされた変調器ノイズが成形した出力(b)、および時間領域内のデシメータの出力信号(c)が示されています。(画像提供:EDN)

図6は、デジタル/デシメーションフィルタを通過するデジタル信号を示しています。デジタルフィルタの24ビット出力(図6(a))は、変調器のサンプリングレート(1/Fs)と同じレートで動作します。変調器はすでに量子化ノイズを高周波数に成形しているため(図6(b))、デジタル/デシメーションフィルタは出力信号の低周波数部分をキャプチャします。デシメーションフィルタ(図6(c))の出力は、元のアナログ信号の低周波数デジタル表現を生成します。

デジタル拡張

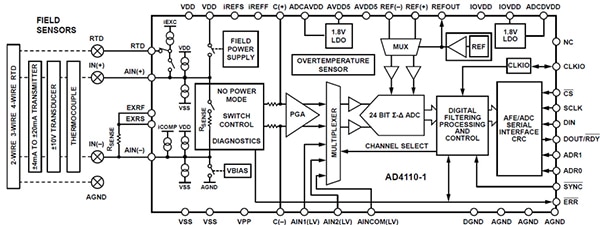

ΔƩ ADCは主に、デジタルドメインに存在します。それで、デジタルプログラム可能なゲイン段、電流源、短絡または開回路の入力信号インジケータ、およびさまざまなシリアル出力インターフェースを簡単に追加できます(図7)。

図7:Analog DevicesのAD4110-1は、産業用プロセス制御システムに複数のアナログフロントエンド機能を提供します。(画像提供:Analog Devices)

図7:Analog DevicesのAD4110-1は、産業用プロセス制御システムに複数のアナログフロントエンド機能を提供します。(画像提供:Analog Devices)

図7は、Analog Devices のAD4110-1ΔƩ ADCには、プログラム可能な入力端子、診断機能、および柔軟なデータレートを含む多くのデジタル機能強化があることを示しています。入力対応センサインターフェースには、RTDおよび熱電対温度センサが含まれます。

AD4110-1にはΔƩ ADCの基本コアがありますが、このデバイスはデジタルを重視し、数々のデジタル対応機能を実現しています。これにより、AD4110-1はユニバーサルなアナログフロントエンド(AFE)になっています。

AD4110-1は標準のΔƩ ADCと同様に、熱電対、RTD、およびブリッジからの非常に低い電圧をデジタル化できます。これらの機能にはしばしば追加の励起回路が必要ですが、AD4110-1ではそれらがボードに組み込まれています。

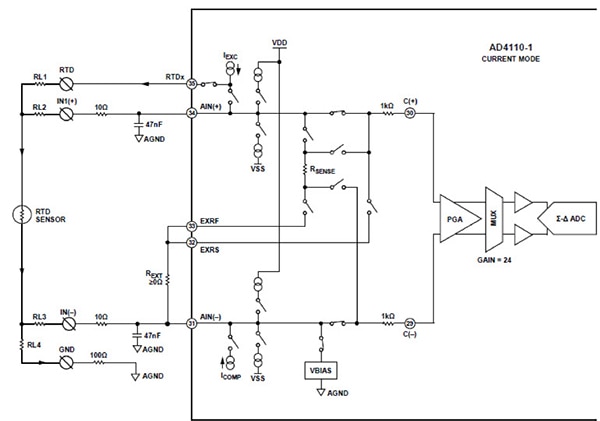

たとえば、RTDは、コンバータの基準電源にレシオメトリックな高精度電流源を必要とします(図8)。

図8:4線式RTDおよびAD4110-1デルタシグマ(ΔƩ)ADC用の適切なワイヤ接続。RTDの励弧電流は、0.1mA~1mAまでの6つのレベルでプログラム可能です。(画像提供:Analog Devices)

図8:4線式RTDおよびAD4110-1デルタシグマ(ΔƩ)ADC用の適切なワイヤ接続。RTDの励弧電流は、0.1mA~1mAまでの6つのレベルでプログラム可能です。(画像提供:Analog Devices)

図8において、AD4110-1には、コンバータのPGA_RTD_CTRLレジスタを使用して0.1mA~1mAまでの6つのレベルにプログラム可能な励弧電流が含まれます。RTD抵抗器への励弧電流は、ピン35からです。コンバータは、ピン34および31の高インピーダンス入力を介して、RTD全体の電圧降下を感知します。AD4110-1のプログラマブルゲインアンプ(PGA)は、0.2~24V/Vの16個のプログラマブルゲインを提供します。この機能により、設計者は入力センサをAD4110-1の入力範囲にさらに補完できます。他の補助機能には、オープンワイヤ(熱電対で有用)、ゲイン較正、および補正係数の存在を感知するプルアップ/プルダウン電流が含まれます。

結論

ΔƩ ADCは、複雑なアナログフロントエンド回路を排除し、フロントエンド変調器、FIRデジタルフィルタ、およびデシメーションフィルタを使用することにより、高分解能かつデジタルで平均化された低ノイズデジタル出力信号を提供します。回路の大部分はデジタル形式であるため、高度なデジタル処理ノードによって簡単に拡張でき、小さなフットプリントとボードの複雑さの低減を維持しつつ、さらに機能を追加できます。

Analog DevicesのAD4110-1 ΔƩ ADCは、このADCアーキテクチャの特性を活用します。AD4110-1にはΔƩ ADCの基本コアがありますが、このデバイスはデジタルを重視し、数々のデジタル対応機能を実現しています。これにより、AD4110-1はユニバーサルなAFEとして、RTDや熱電対に確実に対応できるようになっています。

免責条項:このウェブサイト上で、さまざまな著者および/またはフォーラム参加者によって表明された意見、信念や視点は、DigiKeyの意見、信念および視点またはDigiKeyの公式な方針を必ずしも反映するものではありません。