パワーコンバータのデッドタイムとその制御方法

自動車、小型電気自動車(EV)、コードレスツール、充電ステーションでの電力要件の高度化により、48V電源システムへの移行が進んでいます。これらのシステムは、高効率と低損失に加え、小型化と軽量化というメリットももたらします。しかし、48V電源システムでは、48Vバスから供給される電力を使用可能な電圧にスイッチ(変換)するためにパワーコンバータの使用が必要となります。

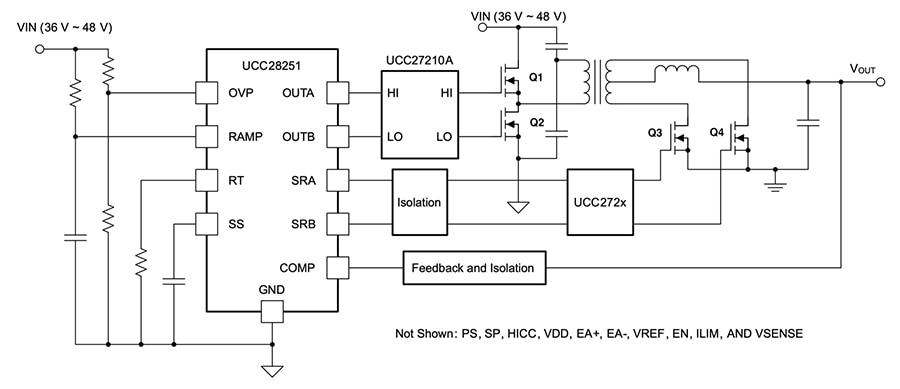

パワーコンバータは、パワースイッチ技術を使用して、48VDCを選択した電圧に変換します。一般的な48Vコンバータ(ここではTexas InstrumentsのUCC28251PWR)は、図1のQ1とQ2で示される電界効果トランジスタ(FET)のようなハーフブリッジ構成のパワースイッチデバイスをベースにしています。パワースイッチデバイスは、パルス幅変調(PWM)コントローラによって制御され、目的の出力電圧を生成、安定化します。

図1:一般的なDC/DCコンバータは、PWMコントローラを使用してハーフブリッジ構成のパワーFETを駆動します。PWMコントローラは、FET入力のパルス幅を調整して、必要な出力(VOUT)電圧を生成、安定化します(画像提供:Texas Instruments)。

図1:一般的なDC/DCコンバータは、PWMコントローラを使用してハーフブリッジ構成のパワーFETを駆動します。PWMコントローラは、FET入力のパルス幅を調整して、必要な出力(VOUT)電圧を生成、安定化します(画像提供:Texas Instruments)。

この回路では、FETであるQ1とQ2がハーフブリッジトポロジを形成しています。これらを交互にオンにして、トランスを駆動します。FETであるQ3とQ4は、トランスの二次側からのスイッチング波形を変換して元のDCに戻す同期整流器です。同期整流器は半導体整流器で発生する直列電圧降下をなくすので、効率が向上します。これらの整流器FETは、一次電源のスイッチデバイスと同期して駆動する必要があります。

代替となるインバータのトポロジには、4つのFETを使用したフルブリッジやHブリッジ、あるいは3相コンバータに使用される、6つのFETをカスケード接続したフルブリッジがあります。これらの技術はすべて、1ペア以上のパワーデバイスを使用しています。それらのペアは、図1のFETのように直列に接続されています。

これらのトポロジには2つの重要な問題があります。1つ目は、ハイサイド(Q1)とローサイド(Q2)のスイッチデバイスを同時にオンにすることができないということです。同時にオンにすると、48Vのバスとグランドの間で短絡が発生してしまいます。この状態は「シュートスルー」と呼ばれ、通常、電源スイッチが破損します。シュートスルーは、各パワーデバイスのスイッチング時間を個別に制御することで防止します。この制御の目的は、非アクティブなデバイスの電源を入れる前に、アクティブなデバイスの電源を切ることにあります。

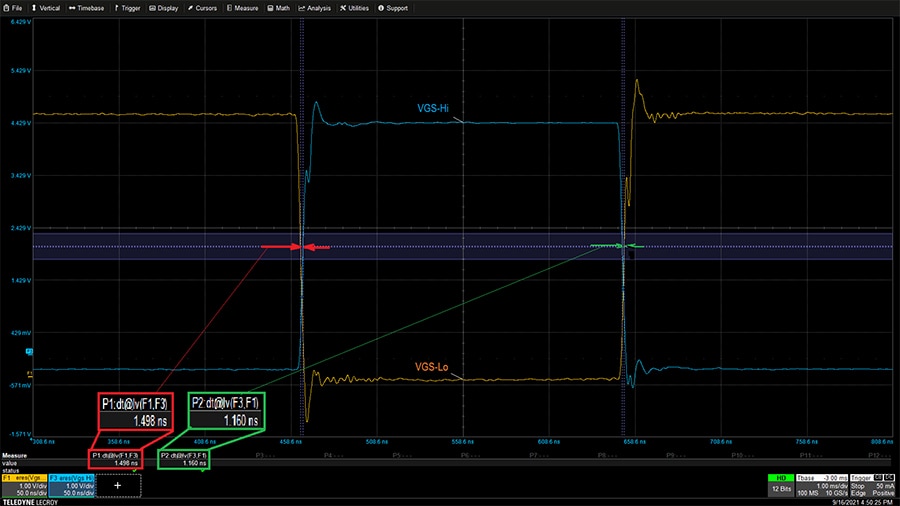

これら2つのイベント(電源オンと電源オフ)の間の遅延を一次デッドタイムと呼びます。一次デッドタイムは、コントローラのパルス幅が最大のときに、ハイサイドFETとローサイドFETのゲート~ソース間電圧(VGS)の遷移時間を比較することで測定されます(図2)。これら両遷移間の遅延がデッドタイムです。

図2:一次デッドタイムは、コントローラのパルス幅が最大のときに、ハイサイドFETとローサイドFETのVGSの遷移時間を比較することで測定されます。これら両遷移間の遅延がデッドタイムです。この例では、1.498nsと1.166nsです(画像提供:Art Pini)。

図2:一次デッドタイムは、コントローラのパルス幅が最大のときに、ハイサイドFETとローサイドFETのVGSの遷移時間を比較することで測定されます。これら両遷移間の遅延がデッドタイムです。この例では、1.498nsと1.166nsです(画像提供:Art Pini)。

図2では、ローサイドFET(VGS LO)がオフになってからハイサイドFET(VGS Hi)がオンになるまでの遅延が1.498nsとなっています。一方、ハイサイドFETがオフになり、ローサイドFETがオンになるまでの遅延が1.166nsだということです。測定されたこれらの遅延が両方とも正である場合のデッドタイムは、許容されます。なお、この測定はPWMコントローラ出力のパルス幅が最大のときに行われます。

デッドタイム中は、どちらのデバイスも導通していないため、「デッドタイム」損失が発生します。どの損失にも当てはまることですが、デッドタイム損失も最小限に抑えることがますます重要になってきています。

2番目の重要な問題は、同期整流器の動作と一次スイッチングの動作を調整することです。

図1に示すUCC28251PWRコントローラは、ハーフブリッジ回路やフルブリッジ回路を制御でき、ゲート駆動信号と同期整流器出力の両方をプログラム可能な遅延時間で提供します。UCC28251PWRは、一次側のデッドタイムを制御し、サイクル毎の過電流保護機能も備えています。一次出力と2次同期整流器駆動信号の間の遅延は、二次デッドタイムと呼ばれ、2つの外部抵抗器を使用して別途プログラムできます。

このPWMコントローラは、一次側ハーフブリッジゲート駆動ICである、Texas InstrumentsのUCC27210DDARと組み合わせて使用します。このICは、ハーフブリッジ構成の両NチャンネルFETのゲート~ソース間入力を駆動します。このICは、固有の伝播遅延が18ns(標準)であるため、一次デッドタイムに影響します。伝播遅延の問題は、両ゲート駆動出力間の遅延を一致させることで最小化されます。UCC27210DDARゲートドライバICは、それらの出力の差を2ns以下に抑えます。同期整流器FETの駆動には、タイミング特性が類似する同一ファミリのゲートドライバを使用しています。

まとめ

48Vシステムへの移行は効率、サイズ、重量の点で元々優位ですが、設計者はデッドタイムの原因を理解し、それを最小化する方法を知っておく必要があります。これまで見てきたように、それには、48Vパワーコンバータの動作を保護するのに必要な機能を備えた専用ICを利用することができます。この専用ICは、一次と二次の両方のデッドタイムを制御し、ハーフブリッジとフルブリッジの両方の回路トポロジで発生する可能性のある主な問題を解決します。

Have questions or comments? Continue the conversation on TechForum, Digi-Key's online community and technical resource.

Visit TechForum