航空宇宙および防衛用の適応型SDR通信システムにおけるアジャイルRFトランシーバの使用

DigiKeyの北米担当編集者の提供

2023-11-30

航空宇宙・防衛(ADEF)システムの設計に対して、動的信号環境に機敏に対応できる、より低電力で小型の通信システムを求める声は後を絶ちません。従来の無線アーキテクチャを超えるソフトウェア定義の無線(SDR)技術を活用すれば、急速に変化するADEF無線要件に対応できます。しかし、SDRの実装は、機能要件を満たし、なおかつサイズ、重量、電力(SWaP)の削減ニーズを満たすという点で複数の課題をもたらしました。

この記事では、性能を犠牲にすることなく、低電力の小型アジャイル通信システムの設計を簡素化できる、Analog Devicesのより効果的なSDRソリューションについて説明します。

より厳しい要求をもたらす新たな課題

ミッションクリティカルな産業用アプリケーションの増加に伴い、安全な無線通信、適応レーダ、電子戦、GPSナビゲーションの強化など、より効果的な通信の設計が求められるようになりました。これらの新たな課題により、広帯域動作の強化、より高いダイナミックレンジ、より高い周波数アジリティ、および再構成可能性へのニーズも高まっています。しかし、これらのより厳しい機能要件は、通信システムが無人航空機(UAV)やポータブルユニットなどの小型バッテリ駆動プラットフォームに移行する中で、SWaP削減ニーズと相反する可能性があります。

従来のディスクリートスーパーヘテロダイン無線アーキテクチャに基づく設計ソリューションは、高性能、広いダイナミックレンジ、および最小限のスプリアスノイズを提供します。設計者にとって、このアプローチの核となる中間周波数(IF)から所望の信号を分離するという課題は、通常、SWaPが高く、再構成可能性がほとんどないという複雑な設計を意味します(図1)。

図1:従来のスーパーヘテロダイン無線アーキテクチャは、性能目標を達成することはできますが、その複雑さゆえに、SWaPを最小限に抑えるという新たな目標を達成することはできません。(画像提供:Analog Devices)

図1:従来のスーパーヘテロダイン無線アーキテクチャは、性能目標を達成することはできますが、その複雑さゆえに、SWaPを最小限に抑えるという新たな目標を達成することはできません。(画像提供:Analog Devices)

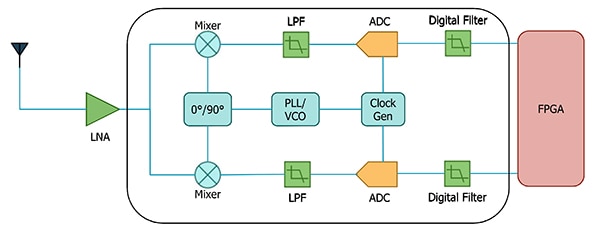

対照的に、直接変換(ゼロIF)アーキテクチャは、フィルタリング要件と非常に広帯域幅のA/Dコンバータ(ADC)の必要性の両方を低減できます。その結果、シングルチップに実装可能なよりシンプルな設計が実現します(図2)。

図2:ゼロIF無線アーキテクチャは、性能強化とSWaP削減のニーズを満たすことができますが、信号絶縁は困難です。(画像提供:Analog Devices)

図2:ゼロIF無線アーキテクチャは、性能強化とSWaP削減のニーズを満たすことができますが、信号絶縁は困難です。(画像提供:Analog Devices)

明らかな利点があるにもかかわらず、直接変換アーキテクチャには実装上の課題があり、その普及には限界があります。このアーキテクチャでは、信号は局部発振器(LO)の周波数で無線周波数(RF)キャリヤに変換されますが、直流(DC)オフセットエラーやLOリークにより、信号チェーンを通じてエラーが伝播する可能性があります。さらに、同一チップ内であっても、信号経路の違いが同相(I)信号と直交(Q)信号のゲインや位相の不一致をもたらし、直交誤差が生じて、信号絶縁が損なわれる可能性があります。

SDR技術は、従来の無線アーキテクチャの限界を克服する可能性を提供しますが、ADEFアプリケーションに関連する広範な要件に対応できるソリューションはほとんどありません。Analog DevicesのADRV9002 RFトランシーバを使用することで、開発者はこのようなアプリケーションで要求される性能と機能の強化およびSWaP削減というニーズを簡単に満たすことができます。 あ

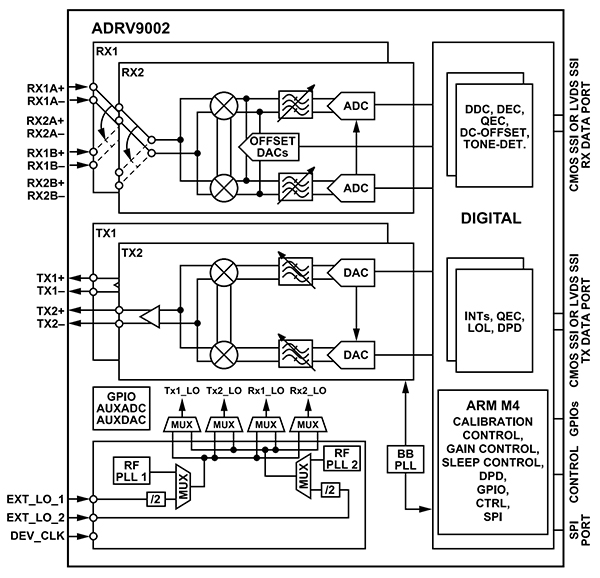

統合された機能により、SWaPの削減とパフォーマンスの最適化を実現

30MHz~6,000MHzの周波数範囲をサポートするADRV9002は、幅広いアプリケーション要件をサポートするために必要なRF、混合信号、デジタル機能をすべて搭載した高度に統合されたトランシーバです。時分割複信(TDD)と周波数分割複信(FDD)の両方の動作が可能なこのデバイスは、プログラム可能デジタルフィルタ、DCオフセット補正、直交誤差補正(QEC)を含む、別々のデュアルチャンネル直接変換レシーバとトランスミッタサブシステムを備えています。

オンチップシンセサイザサブシステム内で、ADRV9002は2つの異なる位相ロックループ(PLL)パスを備えています。1つは高周波数RFパス用、もう1つはデジタルクロックおよびコンバータサンプリングクロック用です。最後に、デバイスのデジタル信号処理ブロックには、自己較正と制御機能を処理するArm® M4組み込みプロセッサが含まれています(図3)。

図3:ADRV9002 RFトランシーバは、デュアル受信(RX)と送信(TX)サブシステムを統合しています。(画像提供:Analog Devices)

図3:ADRV9002 RFトランシーバは、デュアル受信(RX)と送信(TX)サブシステムを統合しています。(画像提供:Analog Devices)

位相ノイズに高感度のアプリケーションのために、ゼロIFモードまたは低IFモードで動作可能なADRV9002は、完全な信号チェーンを提供するトランスミッタとレシーバのサブシステムを備えています。各トランスミッタサブシステムは、1組のデジタル/アナログコンバータ(DAC)、フィルタ、およびI/Q信号を再結合するミキサを提供し、送信用のキャリヤ周波数に変調します。

各レシーバサブシステムは、電流モードパッシブミキサに供給するゲイン制御用の抵抗入力ネットワークを統合します。次に、トランスインピーダンスアンプは、ミキサの電流出力を電圧レベルに変換し、高いダイナミックレンジを備えたADCでデジタル化します。TDD動作時の空きトランスミッタスロットや、レシーバシステムが1つしか使用されないFDDアプリケーションでは、未使用のレシーバ入力を使用してトランスミッタチャネルのLOリークやQECを監視したり、未使用のレシーバ入力を使用してパワーアンプ(PA)の出力信号レベルを監視したりすることができます。

後者の機能は、ADRV9002の統合型デジタルプリディストーション(DPD)機能で発揮されます。これは、監視されているPA信号レベルを使用して、出力を線形化するために必要な適切なプリディストーションを適用します。この機能により、ADRV9002はPAを飽和に近づけて駆動し、効率を最適化することができます。

電力と性能の調整

ADRV9002デバイスは、196ボールのチップスケールパッケージ(CSP)ボールグリッドアレイ(BGA)に完全に統合されたソリューションを提供し、SDR ADEF通信システムのサイズと重量を最小限に抑えます。開発者が消費電力をさらに最適化できるように、ADRV9002は、性能と電力の適切なバランスを見つけられるよう特別に設計された複数の機能を統合しています。

ブロックレベルでは、開発者は個々の信号経路ブロックにパワースケーリングを展開して、性能の低下と消費電力の低下をトレードすることができます。さらに、TDD受信(RX)および送信(TX)フレームのブロックを無効にし、RX/TXまたはTX/RXのターンアラウンド時間を犠牲にして消費電力を下げることができます。開発者の能力をさらに支援して電力性能比を最適化するため、各ADRV9002レシーバサブシステムには、2組のADCが搭載されています。1組目は高性能シグマデルタADCで構成され、2組目は消費電力が重要な場合に代用できます。

周期的な非アクティブ期間が特徴的なアプリケーションでは、ADRV9002のRXモニタモードを使用することができます。このモードでは、ADRV9002はプログラムされたデューティサイクルで最小電力スリープ状態と検出状態を交互に繰り返します。検出状態では、デバイスはレシーバを起動し、開発者によってプログラムされた帯域幅とRX LO周波数で信号の取得を試みます。デバイスがプログラムされた閾値を超える信号パワーレベルを測定した場合、デバイスはモニタモードを終了し、ADRV9002のブロックには希望する信号を処理するために電源が投入されます。

迅速な試作と開発

Analog Devicesは、エンジニアが評価、試作、開発に迅速に移行できるよう、ADRV9002ベースのシステムのハードウェアとソフトウェアを幅広くサポートしています。

ハードウェアサポートにおいて、Analog DevicesはADRV9002ベースのカードを2枚提供しています。

- 30MHz~3GHz帯で動作するローバンドアプリケーション用のADRV9002NP/W1/PCBZ

- 3~6GHz帯のハイバンドアプリケーション用のADRV9002NP/W2/PCBZ

FMCコネクタを搭載したこれらのカードは、パワーレギュレーションを備えたオンボードADRV9002とハードウェアインターフェース、クロックおよびマルチチップ同期(MCS)分配をサポートします。これらのカードは、FMCコネクタを介して、AMDのZCU102評価ボードなどのFPGAマザーボードに接続し、電源とアプリケーションを制御します。

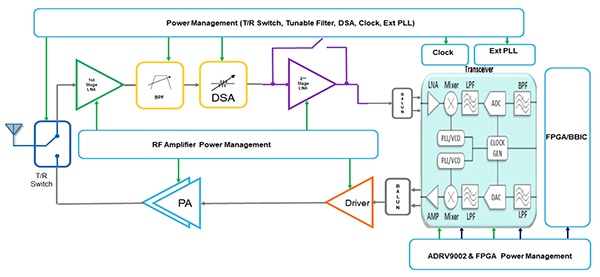

Analog Devicesは、ADRV9002NP無線カードの完全な回路図と部品表(BOM)をサポートパッケージで提供しています。この回路図とBOMは、ほとんどのアプリケーションのカスタムハードウェア開発の効果的な出発点となります。アプリケーションによっては、特定の信号コンディショニング要件を満たすために、RFフロントエンドを追加する必要があります。それらのアプリケーションの場合、開発者は数個のコンポーネントを追加するだけで設計が完了します(図4)。

図4:高度に統合されたADRV9002トランシーバにより、開発者は特殊な設計を迅速に実装することができます。(画像提供:Analog Devices)

図4:高度に統合されたADRV9002トランシーバにより、開発者は特殊な設計を迅速に実装することができます。(画像提供:Analog Devices)

この例では、開発者はAnalog Devicesの以下の電源管理部品を使用して、適切なRFフロントエンドを迅速に実装できます。

- ADRF5160 RFスイッチ

- HMC8411低ノイズアンプ(LNA)

- ADMV8526デジタル調整可能なバンドパスフィルタ

- HMC1119 RFデジタルステップアッテネータ(DSA)

- HMC8413ドライバアンプ

- HMC8205B PA

Analog Devicesは、ドキュメントやダウンロード可能なソフトウェアパッケージを通じて、包括的なソフトウェア開発サポートを提供しています。上記の開発用ハードウェアを使用する開発者は、Analog Devicesの製品ラインソフトウェアまたはオープンソースソフトウェアパッケージに基づいて試作と開発を進めることができます。

この記事の以下の説明は製品ラインソフトウェアに限定されます。オープンソース開発手法の詳細については、Analog Devicesの『ADRV9001/2試作プラットフォームユーザーガイド』を参照してください。Analog Devicesは、同社のサポート文書における「ADRV9001」という用語は、ADRV9002とADRV9001ファミリの他のメンバーを含むファミリ名を意味すると規定しています。したがって、以下の文章や図におけるADRV9001への言及は、この記事の焦点であるADRV9002デバイスに適用されます。

Analog Devicesの製品ラインソフトウェア開発キット(SDK)の配布を通じて入手可能なWindowsベースのトランシーバ評価ソフトウェア(TES)ツールは、トランシーバ性能を迅速に設定・評価するためのアクセス可能な出発点を提供します。

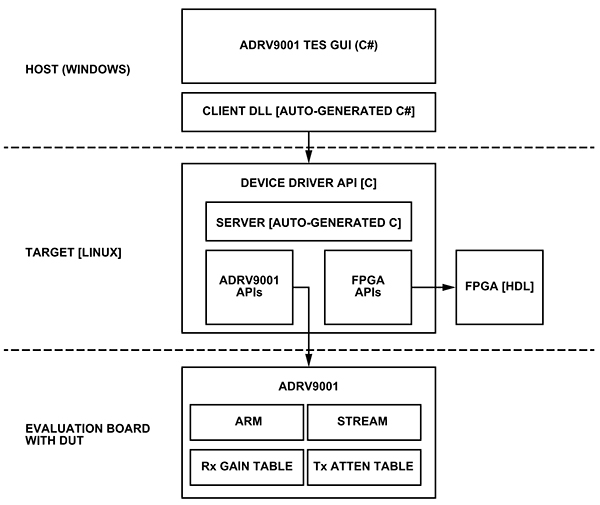

Analog DevicesのADRV9002ベースのカードとAMDのZCU102評価ボードを使用した評価と試作では、TESツールがグラフィカルユーザーインターフェース(GUI)を提供し、ハードウェアの設定とキャプチャされたデータの観測を行います(図5)。

図5:SDKパッケージのTESツールにより、開発者はサポートされている評価プラットフォーム上でADRV9002トランシーバの評価を迅速に開始できます。(画像提供:Analog Devices)

図5:SDKパッケージのTESツールにより、開発者はサポートされている評価プラットフォーム上でADRV9002トランシーバの評価を迅速に開始できます。(画像提供:Analog Devices)

TESツールは、Linux環境、MATLAB環境、またはPythonにコンパイル可能なC#コードを自動生成します。SDKは、AMD ZCU102プラットフォーム用に開発されたADRV9001 APIパッケージを含む、ソフトウェアライブラリおよびアプリケーションプログラミングインターフェース(API)一式を提供します。

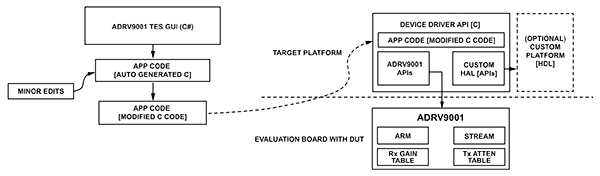

SDKフローは、評価ボードによる評価や試作から開発者のカスタムターゲット環境への移行も直接サポートします(図6)。

図6:SDKアーキテクチャにより、開発者は評価結果を独自のターゲットプラットフォームに簡単に拡張できます。(画像提供:Analog Devices)

図6:SDKアーキテクチャにより、開発者は評価結果を独自のターゲットプラットフォームに簡単に拡張できます。(画像提供:Analog Devices)

この移行フローでは、開発者は以前と同じようにTESにコードを自動生成させます。しかし、開発者はそれを直接使用するのではなく、生成されたコードの編集済みバージョンをターゲットプラットフォームに展開します。実際に必要な編集は、主に、TESツールによって認識されるもののターゲットシステムで必要とされないハードウェアコンポーネントを参照する関数コールを削除することに限定されます。SDKアーキテクチャには、ADRV9001ライブラリと開発者のハードウェア間のハードウェア抽象化レイヤ(HAL)インターフェースが含まれているため、開発者は特定のハードウェアのHALインターフェースコードを実装したカスタムコードを提供するだけで済みます。その結果、開発者はAnalog DevicesのカードとAMDボードを使用した評価から、カスタムターゲット環境の開発へと迅速に移行することができます。

まとめ

ADEFアプリケーションは、複雑化する信号環境において課題の増加に直面しています。開発者は、より広い周波数帯域でより高い性能を求める要求に応えるとともに、こうしたアプリケーションのバッテリ駆動システムへの移行をサポートするために、SWaPを下げる必要があります。Analog Devicesの高度に統合されたトランシーバを使用することで、開発者はSDRソリューションを実装し、これらの要件により効果的に対処することができます。

免責条項:このウェブサイト上で、さまざまな著者および/またはフォーラム参加者によって表明された意見、信念や視点は、DigiKeyの意見、信念および視点またはDigiKeyの公式な方針を必ずしも反映するものではありません。