高効率、高電圧、スイッチモード電源アプリケーションにGaN電界効果トランジスタを適用する理由と方法

DigiKeyの北米担当編集者の提供

2023-01-26

電力効率は、社会的な要求と規制の両方に直面している電子システムにとって優先事項の一つです。特に、電気自動車(EV)から高電圧の通信および産業用インフラに至るまでのアプリケーションでは、電力変換効率と電力密度は設計の成功に欠かせない要素です。

従来のシリコーン(Si)ベースの金属酸化膜電界効果トランジスタ(MOSFET)や絶縁ゲートバイポーラトランジスタ(IGBT)が理論限界に近づいているため、以上の要求を満たすために、スイッチモード電源システムの設計者はそれらを使用しない方向へ移る必要があります。

それらの代わりとして、窒化ガリウム(GaN)などのワイドバンドギャップ(WBG)材料を用いたデバイスを検討する必要があるのです。GaNデバイスは、Siデバイスに比べると、スイッチング速度が速く、高い電圧と電力レベルに対応し、各電力レベルでは小型で、高い効率で動作します。

そこで本稿では、GaN FETの基礎を説明して、スイッチモード電源回路における従来のSiデバイスに対するGaN FETの優位性を示し、Nexperiaの実例を紹介して、その応用について考察します。

GaN FETの基礎

電力変換回路の基本デバイス(素子)は、高電圧の半導体スイッチです。設計者はこれらのデバイスの性能向上に努力してきました。具体的には、オン状態直列抵抗の削減による伝導損失の低減、遷移速度の向上によるスイッチング損失の低減、寄生効果の低減などです。このような設計は、シリコーンMOSFETおよびIGBTでは概ね成功していますが、これらのデバイスの動作が理論的な限界に達するにつれて、改善速度が鈍化してきています。

そのため、ここ数年、SiC(シリコーンカーバイド)やGaNを用いたWBGデバイスが登場し、量産化に至っています。これらのデバイスは、Siを用いたデバイスよりも、高い動作電圧範囲、短いスイッチング時間、高い効率を提供します。

半導体のバンドギャップとは、電子を励起して結合状態から自由な状態にして電気を通すのに必要となる、最小エネルギーのことです(表1)。

|

表1:GaNやSiCなどのワイドバンドギャップ半導体が持つ特性のうち、Siと異なる主な特性をまとめたものです。(表提供:Art Pini)

広いバンドギャップの半導体で製造されたデバイスは、Siなどの従来の半導体材料よりも大幅に高い電圧、周波数、温度で動作させることができます。広いバンドギャップは、デバイスをより高い温度で動作できるようにするうえで特に重要です。高い温度耐性は、通常の条件下では、これらのデバイスがより高い電力レベルで動作できることを意味しています。臨界電界が高く電子移動度の高いWBG半導体は、ドレイン~ソース間オン状態抵抗(RDS(ON))が最も低くなるので、伝導損失を低減することができます。

また、バンドギャップが広い材料の多くは自由電子速度が速いため、より高速なスイッチング速度で動作させることができます。

バンドギャップが1.12電子ボルト(eV)のSiに比べ、GaNとSiCはそれぞれ3.4eVと3.3eVと、約3倍も高いバンドギャップを持つ化合物半導体です。つまり、どちらもより高い電圧とより高い周波数に対応することができるのです。

GaNは電子移動度が高いため、高性能・高周波のアプリケーションに適しています。GaNパワーFETによって可能になるスイッチング速度と動作周波数の向上により、信号制御の改善、カットオフ周波数の高いパッシブフィルタ設計、リップル電流の低減が実現されます。これにより、小型のインダクタ、コンデンサ、およびトランスを使用できるようになるので、全体的に小型軽量化されます。

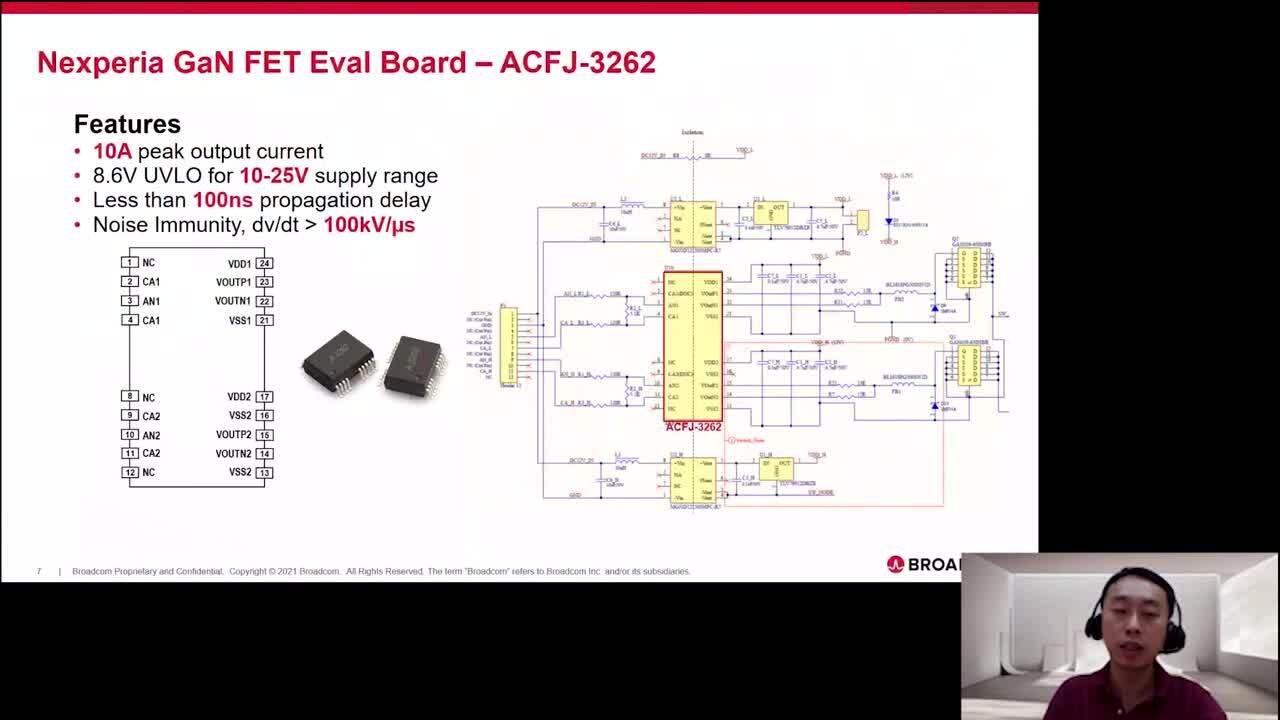

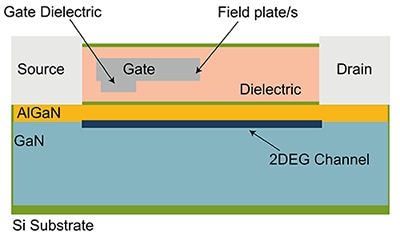

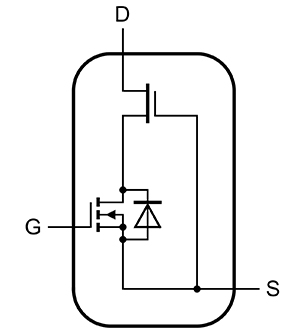

GaN FETは高電子移動度トランジスタ(HEMT)と呼ばれています。高電子移動度は、FETの構造によるものです(図1)。

図1:Si基板上のGaN FETの断面図(画像提供:Nexperia)

図1:Si基板上のGaN FETの断面図(画像提供:Nexperia)

GaN FETは、生産するのに既存のシリコーンCMOSの生産設備を利用できるため、コスト面でも優れています。Si基板上で、シード層と、絶縁層としてのGaNと窒化アルミニウムガリウム(AlGaN)のグラデーション層(図には含まれず)を成膜することで、GaN層を形成します。さらに、GaN層の上に第2層であるAlGaN層を成膜します。これにより、圧電分極が設定され、AlGaNの直下に発生する過剰な電子が高導電性チャンネルとなります。この過剰な電子は、2次元電子ガス(2DEG)と呼ばれています。こう名付けられた理由は、この層の電子移動度が非常に高いからです。

ゲートの下には空乏領域が形成されます。ゲートの動作は、Nチャンネル & エンハンスメントモード(エンハンスメント型)のパワー半導体MOSFETの動作に似ています。このデバイスのゲートに正電圧をかけると、デバイスに電源が入ります。

電源デバイスを作成するために、この構造を何回か重ねます。これにより、基本的にシンプルでエレガント、かつコスト効率の高いパワースイッチング用ソリューションが完成します。

より高電圧のデバイスを得るには、ドレインとゲートの間の距離を広げます。GaNの2DEG(two dimensional electron gas、2次元電子ガス)は抵抗率が非常に低いため、ブロッキング電圧能力を上げることによる抵抗への影響は、シリコーンデバイスと比較して非常に小さくなります。

GaN FETは、エンハンスメントモードと空乏(またはデプレッションあるいはデプリーション)モード(または空乏型)の2つの構成で動作するように製造することができます。エンハンスメントモードのFETはノーマリオフなので、FETの電源を入れるには、ドレインとソースに正のゲート電圧を印加する必要があります。空乏モードのFETはノーマリオンなので、FETの電源を切るには、ドレインとソースに負のゲート電圧を印加する必要があります。電力システムに電源を投入する前に、空乏モードのGaN FETに負バイアスを印加する必要があるため、空乏モードのGaN FETは電力システムにおいて問題があります。

この問題を回避する方法として、低電圧シリコーンFETと空乏モードGaN FETを組み合わせたカスコード回路構成があります(図2)。

図2:低電圧シリコーンMOSFET(S)と空乏モードGaN FET(G)のカスコード構成により、Siゲート構造が堅牢になるとともに、GaNデバイスの高電圧クロック特性が改善され、さらに(空乏モードGaN FETの場合)電源投入時にこの複合デバイスの電源が切断されます。(画像提供:Nexperia)

図2:低電圧シリコーンMOSFET(S)と空乏モードGaN FET(G)のカスコード構成により、Siゲート構造が堅牢になるとともに、GaNデバイスの高電圧クロック特性が改善され、さらに(空乏モードGaN FETの場合)電源投入時にこの複合デバイスの電源が切断されます。(画像提供:Nexperia)

カスコード回路はSi MOSFETゲート構造を採用しています。このため、メリットとして、ゲート駆動制限が既存のMOSFETゲートドライバICに合わせて高いほか、電源投入時に空乏モードGaN FETの電源が切断されます。

GaN FETの大きな特長のひとつは、その効率の高さです。その理由は、直列抵抗が低いため伝導損失が少ないこと、スイッチング時間が短いためスイッチング損失が少ないこと、逆回復電荷が少ないため逆回復損失が少ないことによります。

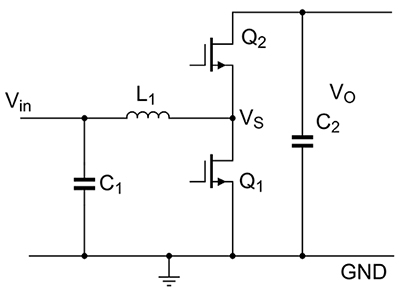

一般的なハーフブリッジブーストコンバータのトポロジを用いて、GaN FETとSi MOSFETを効率面で比較することが可能です(図3)。

図3:MOSFETとGaN FETを効率面で比較するために、トランジスタQ1、Q2を互いに交換したハーフブリッジブーストコンバータの回路図が示されています。(画像提供:Nexperia)

図3:MOSFETとGaN FETを効率面で比較するために、トランジスタQ1、Q2を互いに交換したハーフブリッジブーストコンバータの回路図が示されています。(画像提供:Nexperia)

このブーストコンバータは、入力電圧が240ボルト、出力が400ボルト、スイッチング周波数が100キロヘルツ(kHz)です。効率と損失を3500ワットまでのパワーレンジで比較しました(図4)。

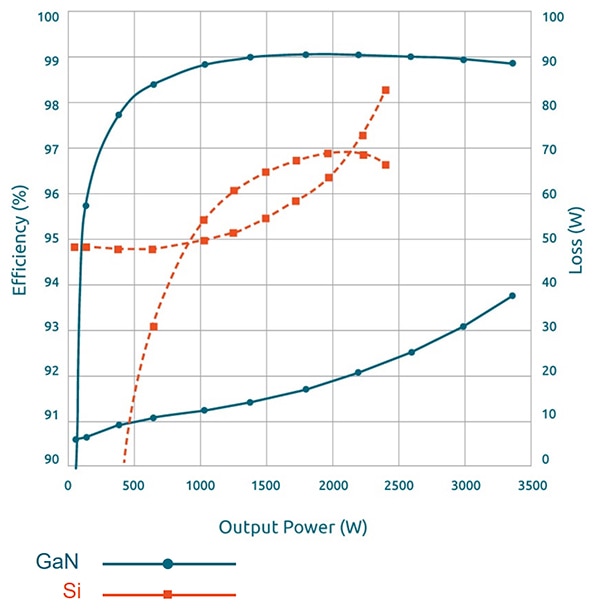

図4:同等の回路におけるGaN FETとMOSFETを効率と電力損失で比較し、GaN FETの優位性を示したものです。(画像提供:Nexperia)

図4:同等の回路におけるGaN FETとMOSFETを効率と電力損失で比較し、GaN FETの優位性を示したものです。(画像提供:Nexperia)

GaN FETはMOSFETに比べて約20%効率が高く、電力損失は約3分の1に低減しています。2000ワットの場合、損失はMOSFETでは約62ワットですが、GaN FETではわずか19ワットです。つまり、GaN FETでは冷却システムを小型化できるので、ブーストコンバータの体積効率を向上させることができるのです。

上のグラフをよく見ると、GaN FETは最大電圧の上限が高いため、3500W近くまで測定が行われていることに気づきます。このように、GaN FETは決定的な優位性を持っているのです。

高電圧用GaNの使用を開始

より高電圧のアプリケーション向けに、Nexperiaでは2つの650V GaN FET、GAN063-650WSAQとGAN041-650WSBQを提供しています。どちらもNチャンネルFETであり、通常はノーマリオフです。GAN063-650WSAQは、650ボルトまでのドレイン~ソース間電圧を処理できる定格であり、800ボルトの過渡電圧(パルス幅は1マイクロ秒未満)に耐えることができます。定格ドレイン電流は34.5アンペア(A)、消費電力は25°Cで143ワットです。ドレイン~ソース間のオン状態抵抗は通常50ミリオーム(mΩ)であり、最大限界は60mΩです。

GAN041-650WSBQも、GAN063-650WSAQと同じ650ボルトの最大ドレイン~ソース間電圧定格と800ボルトの過渡限界を備えています。GAN063-650WSAQと異なるのは、室温で最大ドレイン電流47.2Aと最大許容損失187ワットを処理できることです。チャンネル抵抗は、標準値が35mΩ(最大値が41mΩ)です。

GAN063-650WSAQをハーフブリッジ構成で使用したNexperiaのリファレンス設計を図5に示します。

図5:GaN FET GAN063-650WSAを使用したハーフブリッジパワー段の推奨設計。この回路図には、FETドライバとハーフブリッジ出力段、および関連部品のみを示しています。(画像提供:Nexperia)

図5:GaN FET GAN063-650WSAを使用したハーフブリッジパワー段の推奨設計。この回路図には、FETドライバとハーフブリッジ出力段、および関連部品のみを示しています。(画像提供:Nexperia)

この回路図は、GaN FETのゲートを駆動するための高/低デュアル絶縁型ゲートドライバSi8230を示したものです。このゲートドライバの出力は、すべてのGaNデバイスで必要とされる30Ωのゲート抵抗を介して、ゲートに接続されます。このゲート抵抗は、ゲート容量の充電時間を制御できるので、動的スイッチング性能に影響します。また、FETのドレイン~ソース間のRC回路網も、スイッチング性能を制御するのに役立ちます。GaN FETのゲート駆動レベルは、0ボルトから10~12ボルトです。

GaN FETはスイッチング速度が10~11ナノ秒と速いため、寄生インダクタンスを最小にするための綿密なレイアウトや、過渡電圧・過渡電流によるリンギングを抑制するためのRCスナバが必要となります。設計では、高電圧電源とグランドの間に複数のRCスナバ(R17~19、C33~35)があります。スナバは、GaN FETとバイパスネットワークの相互作用によって生じるリンギングを低減します。ハイサイドFETのドレインにできるだけ近いところにスナバを接続してください。スナバは、リード線インダクタンスを最小限に抑えるために、面実装抵抗と低ESR(実効直列抵抗値)セラミックコンデンサで実装されています。

R4、D1、C12、C13で形成される部品ネットワークは、ハイサイドゲートドライバのブートストラップ用電源となります。D1は、その接合静電容量がスイッチング損失の要因となるため、高速で低容量のダイオードにする必要があります。R4 は、充電の突入電流を制限するもので、10~15Ωの範囲の値が有効です。

まとめ

EVから通信、産業用インフラに至るまで、電力変換効率と電力密度の向上が要求されている中、従来のSi構造からの転換が求められています。ご説明してきたように、GaN FETは、より高い動作電圧、より短いスイッチング時間、より高い効率を提供することで、次世代の設計に道を開くものです。リファレンス設計によってサポートされている場合もある既製の部品は、設計者がプロジェクトを迅速に立ち上げて実行するのに役立ちます。

免責条項:このウェブサイト上で、さまざまな著者および/またはフォーラム参加者によって表明された意見、信念や視点は、DigiKeyの意見、信念および視点またはDigiKeyの公式な方針を必ずしも反映するものではありません。