Xilinx ZCU102評価キットでNVMe SSDインターフェースを有効化

DigiKeyの北米担当編集者の提供

2020-05-12

概要

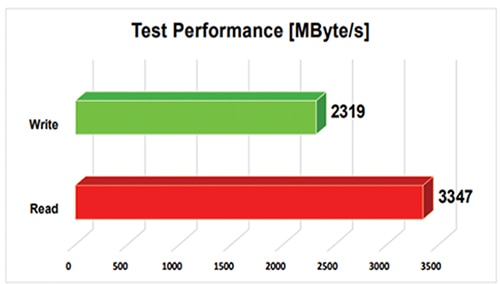

Xilinx® UltraScale™ MPSoCアーキテクチャに基づくZynq® UltraScale+™ MPSoCファミリは、機能豊富な64ビットクアッドコア/デュアルコアARMベースの処理システム(PS)とXilinxプログラマブルロジック(PL)UltraScaleアーキテクチャを単一デバイスに統合します。また、オンチップメモリ、マルチポート外部メモリインターフェース、ペリフェラルコネクティビティインターフェースの豊富なセットも含まれています。特に、GTH 16.3Gbpsトランシーバには、NVMe SSDドライブなどのPCI Express® Gen3ストレージデバイスインターフェースをサポートする機能があります。この記事では、非常に高速な性能を実現可能なDesign GatewayのNVMeG3-IP Coreを使用することにより、XilinxのZCU102評価キットでNVMe SSD(ソリッドステートドライブ)インターフェースを実装するソリューションについて説明します(書き込み速度2,319MB/s、読み取り速度3,347MB/s)。

Zynq® UltraScale+ MPSoC ZCU102評価キットの紹介

ZCU102は、XCZU9EG-2FFVB1156E MPSoCデバイスに基づく迅速な試作を実現する汎用評価ボードです。このボードには、高速DDR4 SODIMMおよびコンポーネントメモリインターフェース、FMC拡張ポート、マルチギガビット/秒のシリアルトランシーバ、多様なペリフェラルインターフェース、ユーザーカスタマイズ設計用のFPGAロジックが含まれます。これらはすべて、柔軟な試作プラットフォームを提供します。

図1:ZCU102評価キット。(画像提供:Xilinx Inc.)

図1:ZCU102評価キット。(画像提供:Xilinx Inc.)

ZCU102は、5Gワイヤレス、次世代先進運転支援システム(ADAS)、および産業用モノのインターネット(IIoT)ソリューションなどの最先端アプリケーションを作成するためのプログラマブルロジック機能を提供します。

どちらにしても、NVMe SSDドライブなどの高性能で信頼性の高い外部データストレージを必要とするアプリケーションには、PCI Express® Gen3対応インターフェース向けのGTHトランシーバを活用する適切なソリューションが必要です。

NVMe SSDストレージの紹介

NVM Express(NVMe)は、PCI ExpressによりSSDとしてアクセスするホストコントローラのインターフェースを定義します。NVM Expressは、たった2つのレジスタ(コマンド発行およびコマンド完了)を使用するだけで、コマンドの発行および完了プロセスを最適化します。他にも、1つのキュー内で最大64Kのコマンドをサポートすることにより、NVMeは並列動作をサポートします。64Kコマンド入力により、シーケンシャルおよびランダムアクセスの両方において伝送性能が向上します。

NVMeドライブは、データストレージや非常に高速なコンピューティングへの道を開きました。PCIe Express® Gen3技術を使用することにより、最新のNVMe SSDドライブはピーク性能40Gbit/sの速度を達成できます。

NVMeストレージデバイスの例については、こちらを参照してください。

ZCU102でのNVMeホストコントローラの実装

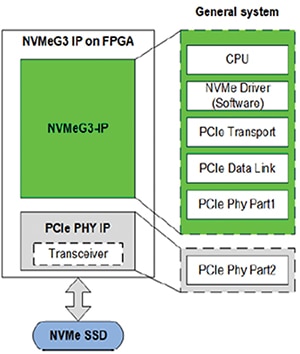

図2:NVMeの実装。(画像提供:Design Gateway)

図2:NVMeの実装。(画像提供:Design Gateway)

従来、NVMeホストは、NVMe SSDとデータを送受信するために、PCIeコントローラで動作するホストプロセッサを使用して実装されます。NVMeプロトコルは、非常に高速なバスを介して接続されたPCIeコントローラのハードウェアCPUペリフェラルとのデバイスドライバ通信用に実装されます。外部DDRメモリは、データバッファリングおよびコマンドキューがPCIeコントローラとSSD間でデータを伝送するために必要です。

PCIe Gen3統合ブロックは、ZCU102上のXCZU9EG-2FFVB1156E FPGAデバイスで使用できないため、従来の実装アプローチは不可能です。

Design Gatewayは、図2に示すNVMeG3-IP Coreを使用して、PCIe統合ブロックが使用できないZynq® UltraScale+™ MPSoCデバイス用にNVMe SSDインターフェースを有効化するソリューションを提案しています。ZCU102用のNVMeインターフェースにより、非常に高い性能と最小限のFPGAリソース消費で、マルチチャンネルRAIDシステムを構築できます。NVMeG3-IPコアライセンスには、設計者が開発にかける時間とコストを軽減するのに役立つサンプルリファレンス設計が含まれます。

Design GatewayのNVMeG3-IPの概要

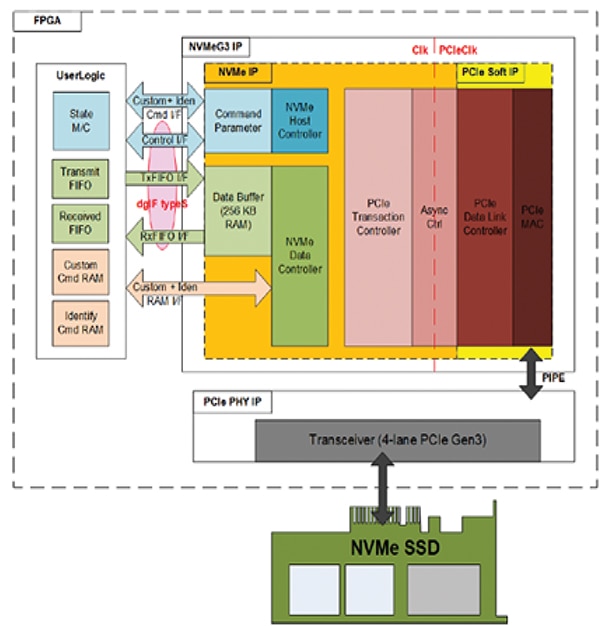

PCIe Gen3ソフトIP(NVMeG3-IP)を備えたNVMe IP Coreは、PCIe統合ブロック、CPU、および外部メモリなしでNVMe SSDにアクセスするのに最適です。NVMeG3-IPには、PCIe Gen3ソフトIPおよび256Kバイトのメモリが含まれます。このソリューションは、PCIe統合ブロックを含まない低コストのFPGAを使用することにより、超高速性能を備えたNVMe SSDストレージを必要とするアプリケーションに推奨されています。

図3:NVMeG3-IPのブロック図。(画像提供:Design Gateway)

図3:NVMeG3-IPのブロック図。(画像提供:Design Gateway)

NVMeG3-IPの特長

NVMeG3-IPには多くの特長がありますが、その一部を以下に示します。

- アプリケーションレイヤ、トランザクションレイヤ、データリンクレイヤ、および物理レイヤの一部を実装して、CPUを使用せずにMVMe SSDにアクセスする

- 4レーンPCI Gen3(128ビットバスインターフェース)として構成されたXilinx PCIe PHY IPで動作する

- 256KバイトのRAMデータバッファを含む

- dgIF typeSを介したシンプルなユーザーインターフェース

- 6つのコマンド(Identify、Shutdown、Write、Read、SMART、およびFlush)をサポート(オプションで追加コマンドをサポート)

- サポートされるNVMeデバイス:

- Base Class Code:01h(マスストレージ)、Sub Class Code:08h(不揮発性)、プログラミングインターフェース:02h(NVMHCI)

- MPSMIN(メモリページ最小サイズ):0(4Kバイト)

- MDTS(最大データ転送サイズ):最低5(128Kバイト)または0(制限なし)

- LBAユニット:512バイトまたは4096バイト

- ユーザークロック周波数は、PCIeクロック(Gen3の場合250MHz)以上である必要があります。

- 使用可能なリファレンス設計:

- AB17-M2FMCアダプタボードを備えたZCU102

- AB18-PCIeX16/AB16-PCIeXOVRアダプタボードを備えたKCU105

- AB18-PCIeX16アダプタボードを備えたVCU118

Design Gatewayは、NVMe SSDにアクセスするためのNVMeホストコントローラとして実行するNVMeG3-IPを開発しました。ユーザーインターフェースと標準機能は、NVMeプロトコルの知識がなくても簡単に使用できるように設計されています。NVMeG3-IPの追加機能は、純粋なロジックによりPCIeプロトコルのデータリンクレイヤおよび物理レイヤの一部を実装する内蔵PCIeソフトIPです。したがって、内蔵PCIeソフトIPおよびXilinx PCIe PHY IPコアを使用することで、PCIe統合ブロックのないFPGAでもNVMeG3-IPを実行できます。Xilinx PCIe PHY IPは、トランシーバとロジックイコライザを含む無料のIPコアとして使用できます。

NVMeG3-IPは、6つのNVMeコマンド(Identify、Shutdown、Write、Read、SMART、およびFlush)をサポートしています。NVMeG3-IPに内蔵される256KバイトのBlockRAMは、データバッファとして機能します。このシステムはCPUや外部メモリを必要としません。NVMeG3-IPの詳細については、当社ウェブサイトからダウンロード可能なデータシートで説明されています。

下の表1は、XCZU9EG-2FFVB1156E FPGAデバイス上のFPGAリソースの使用方法を示しています。

|

表1:Ultrascale/Ultrascale+デバイスのサンプル実装統計

ZCU102での実装と性能結果

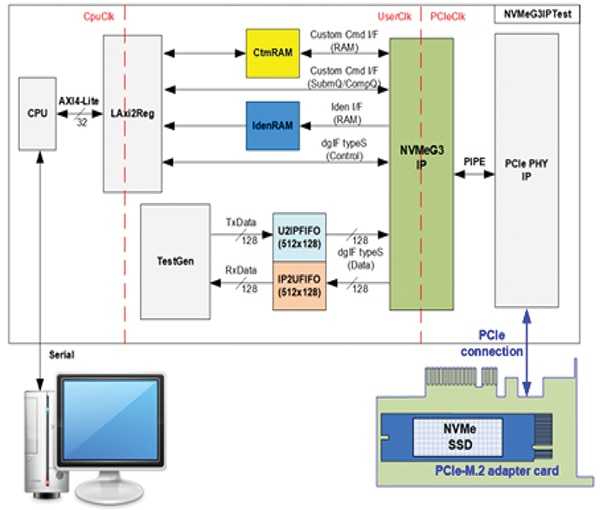

図4は、NVMeG3-IPの動作を実証するために、ZCU102に基づくリファレンス設計の概要を示しています。デモシステムのNVMeG3IPTestモジュールには、以下のモジュールが含まれます。TestGen、LAxi2Reg、CtmRAM、IdenRAM、およびFIFO。

NVMeG3-IPリファレンス設計の詳細については、Design Gatewayのウェブサイトで提供されているNVMeG3-IPリファレンス設計ドキュメントを参照してください。

図4:NVMeG3-IPリファレンス設計の概要。(画像提供:Design Gateway)

図4:NVMeG3-IPリファレンス設計の概要。(画像提供:Design Gateway)

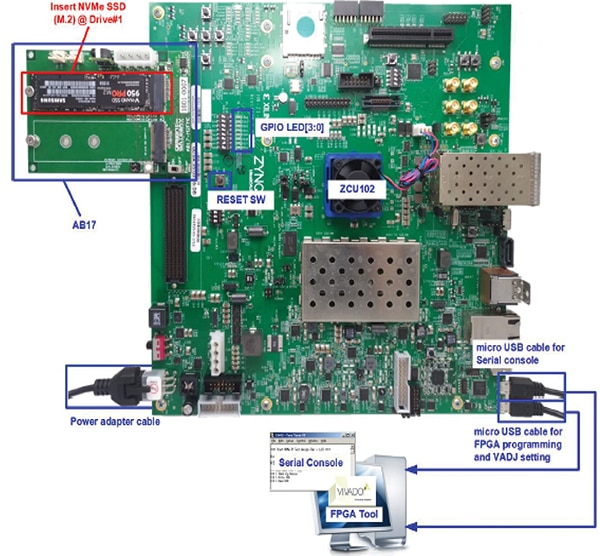

デモシステムは、ZCU102上のNVMe SSDでデータを書き込み/検証するように設計されています。ユーザーは、シリアルコンソールによりテスト動作を制御します。NVMe SSDがZCU102とインターフェースするためには、図5に示すAB17-M2FMCアダプタボードが必要です。

図5:ZCU102上にセットアップされたNVMeG3-IPデモ環境。(画像提供:Design Gateway)

図5:ZCU102上にセットアップされたNVMeG3-IPデモ環境。(画像提供:Design Gateway)

図6は、512GBのSamsung 970 Proを使用したZCU102でデモシステムを実行する場合のサンプルテスト結果を示しています。

図6:Samsung 970 PRO Sを使用したZCU102でのNVMe SSD読み取り/書き込み性能。(画像提供:Design Gateway)

図6:Samsung 970 PRO Sを使用したZCU102でのNVMe SSD読み取り/書き込み性能。(画像提供:Design Gateway)

結論

NVMeG3-IP Coreは、ZCU102評価キットでNVMe SSDインターフェースを有効化するソリューション、さらにはPCIe統合ブロックが使用できないXilinx®のZynq® UltraScale+™ MPSoCデバイスファミリ向けのソリューションを提供します。NVMeG3-IPは、CPUを要することなくNVMe SSDへのアクセスに最小限のFPGAリソースを使用して、可能な限り最高の性能を実現するために設計されています。NVMeG3-IPは、CPUの介入を受けない高性能NVMeストレージに最適であり、FPGAデバイス上のPCIe統合ブロックの数による制限なしでGTHトランシーバを活用することにより、複数のNVMe SSDインターフェースを実装できます。

免責条項:このウェブサイト上で、さまざまな著者および/またはフォーラム参加者によって表明された意見、信念や視点は、DigiKeyの意見、信念および視点またはDigiKeyの公式な方針を必ずしも反映するものではありません。