変換ループモジュールを使用して低ジッタ、高周波クロックを素早く生成

DigiKeyの北米担当編集者の提供

2021-08-04

計装/計測システムの設計者は、信号対ノイズ比(SNR)やエラーベクトル振幅(EVM)を提供するために、低ジッタでスプリアスのない信号を必要とします。SNRやEVMは、ますます厳しくなる顧客の要件に応えるために必要です。その一方で、基板占有面積の削減、設計コストの削減、複雑さの削減という大きなプレッシャーにもさらされています。後者は、短くなる市場投入までの開発期間を短縮するために重要です。

多くのアプリケーションの課題に対処するために、技術者は、計装/計測のクロックソリューションを、従来のカスタムメイドのディスクリート設計から、より統合されたソリューションへと移行させる必要があります。そのための重要なステップは、統合型の変換PLL(位相ロックループ)を使用することです。これにより、外部固定の局部発振器(LO)のジッタや位相ノイズを維持しながら、従来の電圧制御発振器(VCO)の信号を周波数アップコンバージョンすることができます。

この記事では、業界最小の統合位相ノイズを実現するための変換ループの役割について説明します。たとえば、この記事ではAnalog DevicesのADF4401A変換ループシステムインパッケージ(TL SiP)を紹介しています。 ADF4401Aは、さまざまな性能要件に対応していることが分かります。出力信号は、10フェムト秒(fs)未満のrms広帯域統合ジッタ能力を備えています。スプリアス成分を減衰させるために絶縁を強化しています。また、統合性、コスト、複雑性、市場投入までの時間など、設計者のニーズにも応えます。

従来のPLLと変換ループの動作

変換ループの主な目的は、従来のPLLに比べて帯域内の位相ノイズを大幅に低減し、入力されたリファレンス信号にロックされた出力信号を生成することです。

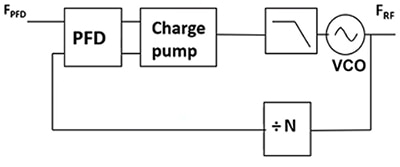

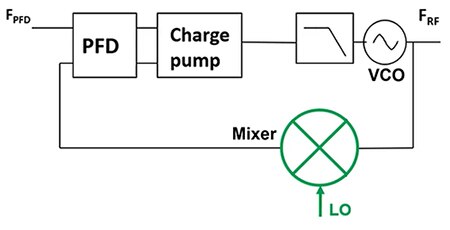

標準的なPLLは、位相周波数検出器(PFD)、チャージポンプ、ローパスフィルタ(LPF)、VCO、フィードバック分周器Nを含むフィードバックシステムで構成されています(図1)。

図1:標準的なPLLは、低い周波数(FPFD)のリファレンスにロックして、出力周波数(FRF)を生成します。(画像提供:ボニー・ベイカー氏)

図1:標準的なPLLは、低い周波数(FPFD)のリファレンスにロックして、出力周波数(FRF)を生成します。(画像提供:ボニー・ベイカー氏)

PFDは、入力リファレンスの位相とフィードバック信号の位相を比較し、両者の位相差に比例した一連のパルスを発生させます。チャージポンプは、PFDパルスを受信し、電流源またはシンクパルスに変換して、VCOの周波数を上下に調整します。LPFは、パルスの高周波エネルギーをすべて除去し、VCOが使用できる電圧に変換します。VCOの出力信号は、分周器Nを介してPFDブロックにフィードバックされ、ループが完成します。

図1の周波数伝達関数は、式1を使用して計算できます。

![]() 式1

式1

FRFは出力周波数

Nはフィードバック分周比(整数または分数)

FPFDはPFDの周波数

図1の帯域内ノイズフロアは、式2を使用して計算できます。

![]() 式2

式2

FOMPLLは、PLLの帯域内位相ノイズフロア性能指数(FOM)

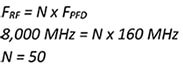

たとえば、帯域内の位相ノイズフロアFOMが-234dB/Hz、PFD周波数(FPFD)が160MHz、出力周波数(FRF)が8GHzの場合を考えてみましょう。

このシステムでは、式1を使用してNの値を計算できます。

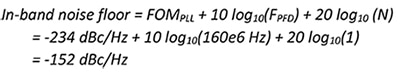

式2を使用して、帯域内ノイズフロアを計算できます。

上の計算では、分周器Nは帯域内のノイズフロア全体に大きく影響しており、20 log10 (50)で34dBとなります。N値を小さくすると、帯域内のノイズフロアは減少しますが、出力周波数も減少します。では、高い出力周波数を発生させながら、ループゲイン(N)を低く抑えるにはどうすればよいのでしょうか。

図2:この例の標準的なPLLでは、フィードバック分周器からのノイズ(20 log10(N))は、N=1の場合の下の黄色のプロットと比較して、帯域内のノイズが34dB高くなっています。(画像提供:ボニー・ベイカー氏)

図2:この例の標準的なPLLでは、フィードバック分周器からのノイズ(20 log10(N))は、N=1の場合の下の黄色のプロットと比較して、帯域内のノイズが34dB高くなっています。(画像提供:ボニー・ベイカー氏)

この問題を解決するには、分周器Nをダウンコンバートミキシングステージに置き換える必要があります(図3)。

図3:変換ループは、従来のフィードバック分周器を使用する代わりに、ミキサを使用してVCOの周波数をPFDの周波数にダウンコンバートします。(画像提供:ボニー・ベイカー氏)

図3:変換ループは、従来のフィードバック分周器を使用する代わりに、ミキサを使用してVCOの周波数をPFDの周波数にダウンコンバートします。(画像提供:ボニー・ベイカー氏)

図3では、ミキサが分周器Nを置き換えているため、ループゲインは1になります(N=1)。この操作により、帯域内のノイズフロアに対するフィードバックループの影響が大幅に減少します。帯域内ノイズの計算では、Nの値は1になりました。式2を使用すると、変更したシステムの帯域内ノイズフロアは以下のようになります。

新しい帯域内ノイズは、34dBc/Hzの改善を示しています。

図3では、ミキサはオフセットLOと呼ばれる極めて低ノイズのLOに依存しています。ロックを実現するためには、FLO ± FRFがFPFDと等しくなければなりません。

変換ループアーキテクチャでは、RF出力で最高の性能を得るために、オフセットLOの位相ノイズが非常に重要になります。このため、技術者は通常、電圧制御の表面弾性波(SAW)や発振器(VCSO)、コム発生器、誘電体共振器発振器(DRO)に基づいてオフセットLOを設計します。オフセットLOの設計についてのサポートは、Analog Devicesにお問い合わせください。

変換ループの課題

従来、低ノイズの変換ループを設計するには、多数の回路ブロックを実装する必要がありました。その結果、複雑な設計となり、通常は大きく、柔軟性にも限界がありました。さらに、対象となる動作のために回路全体の検証と特性評価を行う必要があります。たとえば、主要な設計上の懸念事項として、RF出力信号へのLOリーク(LOとRF間の絶縁)があります。これは、技術者にとって重要な課題です。従来の設計では、技術者は通常、最適な性能と適切な絶縁を実現するために、何度も設計を繰り返していました。

図3では、ADF4401Aが主要な回路ブロックを統合し、完全に特性化されたソリューションを提供していることが分かります。また、変換ループ設計における性能と絶縁に関する従来の課題を解消していることも分かります。このプログラマブルなソリューションにより、技術者は最初の取り組みで最適な性能を実現し、市場投入までの時間を短縮することができます。

ADF4401Aの評価

ADF4401Aは、62.5MHz~8GHzのRF帯域幅を持つ周波数生成ソリューションを使用して、高性能機器の市場投入までの時間を短縮できるように設計されています。ADF4401Aは、ダウンコンバートミキサの採用により、非常に低い帯域内ノイズを実現しています。100Hzから100MHzの広帯域でジッタは約9フェムト秒(fs)です。ADF4401Aの設計とレイアウト技術により、90dBc(標準)のスプリアスフリーのダイナミックレンジを実現しています。パッケージサイズは18 x 18 x 2.018mmで、従来のディスクリート設計に比べて大幅に基板面積を削減しています。

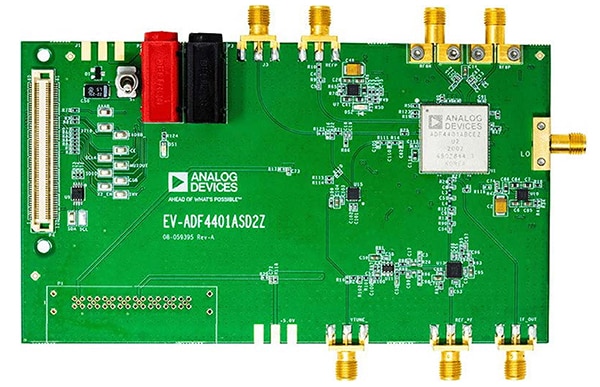

このデバイスの性能を評価するために、設計者はEV-ADF4401ASD2Z評価ボードを使用することができます(図4)。このボードには、外部PFD(HMC3716)、アクティブフィルタ(LT6200)、マルチプレクサ(ADG1609)を含む完全な変換ループが搭載されています。

図4:ADF4401A変換ループモジュール用EV-ADF4401ASD2Z評価ボードには、外部PFD、USBインターフェース、電圧レギュレータが搭載されています。(画像提供:Analog Devices)

図4:ADF4401A変換ループモジュール用EV-ADF4401ASD2Z評価ボードには、外部PFD、USBインターフェース、電圧レギュレータが搭載されています。(画像提供:Analog Devices)

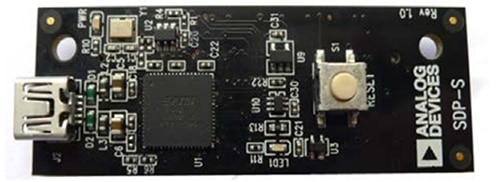

EV-ADF4401ASD2Zは、ADF4401A TL SiPに、VCO、ループフィルタ(5MHz)、PFD、USBインターフェース、電圧レギュレータを内蔵しています。また、EV-ADF4401ASD2Zには、EVAL-SDP-CS1Z(SDP-S)システムデモンストレーションプラットフォーム(SDP)(シリアル)のコントローラボードが必要です(図5)。このボードには、PCからEV-ADF4401ASD2ZへのUSB接続が用意されており、プログラミングが可能です。EV-ADF4401ASD2Zのキットには、コントローラボードは含まれていません。

図5:EV-ADF4401ASD2ZからPCにUSB接続してプログラミングを行うためには、EVAL-SDP-CS1Z(またはSDP-S)コントローラボードが必要です。(画像提供:Analog Devices)

図5:EV-ADF4401ASD2ZからPCにUSB接続してプログラミングを行うためには、EVAL-SDP-CS1Z(またはSDP-S)コントローラボードが必要です。(画像提供:Analog Devices)

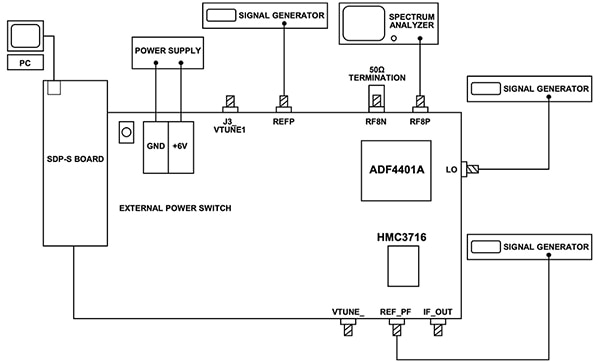

図6は、EV-ADF4401ASD2Zシステムの物理的接続を示しています。関連する分析 | 制御 | 評価用(ACE)ソフトウェアは、TL SiPの機能を制御します。電源は外部からの6V電源を使用しています。

図6:EV-ADF4401ASD2Zのセットアップ図には、SDP-Sコントロールボード、PC、電源、信号発生器、スペクトラムアナライザなど、ADF4401Aの評価に必要な機器と接続が示されています。(画像提供:Analog Devices)

図6:EV-ADF4401ASD2Zのセットアップ図には、SDP-Sコントロールボード、PC、電源、信号発生器、スペクトラムアナライザなど、ADF4401Aの評価に必要な機器と接続が示されています。(画像提供:Analog Devices)

この評価ボードを使用するための推奨機器には、Windows PC、スペクトラムアナライザまたは信号源アナライザ、3つの信号発生器などがあります。

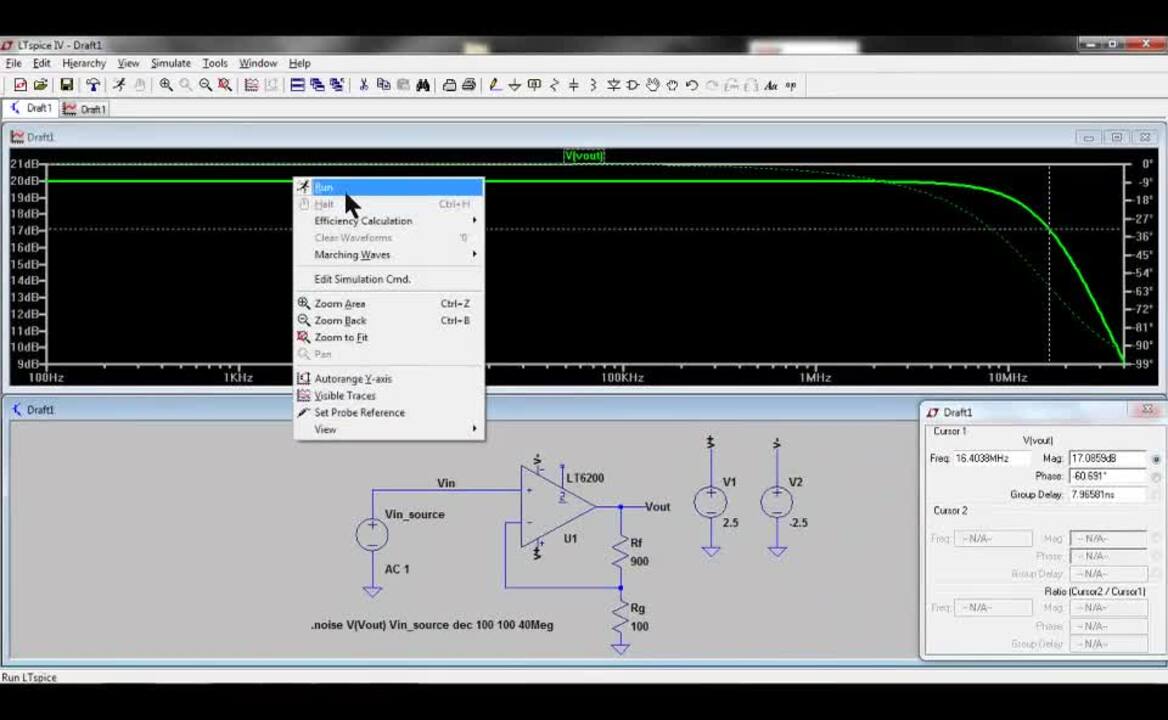

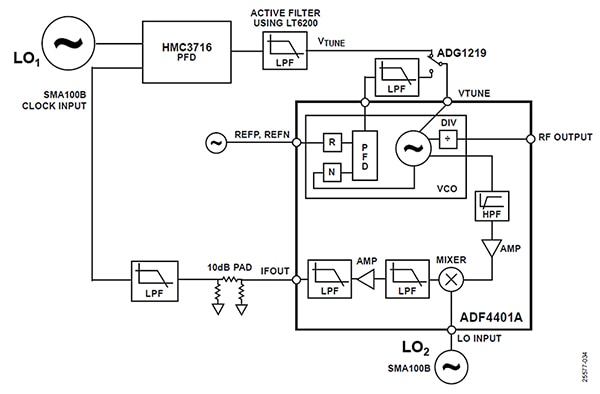

EV-ADF4401ASD2Zのブロック図には、ADF4401Aモジュールに加えて、Analog DevicesのHMC3716 PFD、LT6200オペアンプ、ADG1219 SPDTスイッチが示されています(図7)。

図7:EV-ADF4401ASD2Z評価ボードのブロック図は、AD4401Aの変換ループをサポートする主要なコンポーネントを示しています。(画像提供:Analog Devices)

図7:EV-ADF4401ASD2Z評価ボードのブロック図は、AD4401Aの変換ループをサポートする主要なコンポーネントを示しています。(画像提供:Analog Devices)

高周波数で動作可能なPFDを使用することが重要です。これにより、分周器の必要性を最小限に抑えることができるためです。分周器は、帯域内のノイズ応答を劣化させる可能性があります。Analog DevicesのHMC3716は、1.3GHzの位相比較周波数に対応しているため、ADF4401AのIFレンジでの使用に適しています。このような回路では、周波数と位相の両方を比較することができるため、意図した出力周波数に周波数を誘導するための追加の回路が必要ありません。HMC3716は、オフセットループを完成させるための外部PFDとなります。HMC3716の高周波動作範囲と超低位相ノイズフロアにより、広帯域のループフィルタの設計が可能になります。

図7では、LPF構成のLT6200オペアンプが高周波のスプリアスを減衰させ、ADG1219スイッチがシステムの変換ループを完成させています。

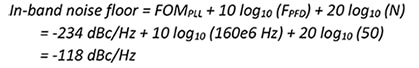

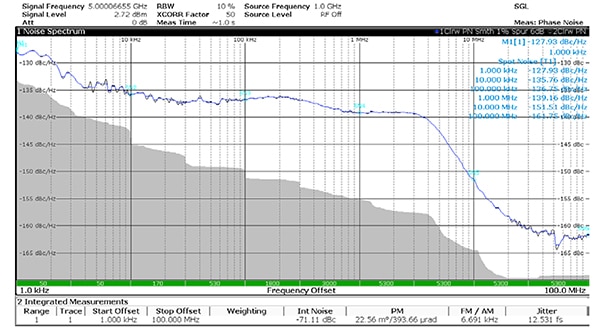

EV-ADF4401ASD2Z評価ボードのセットアップは、図8のように、帯域内ノイズプロットとジッタ測定を示しています。

図8:HMC3716の外部リファレンスを500MHz、外部LOを4.5GHzとした場合の、5GHz出力におけるシングルサイドバンドの位相ノイズ。(画像提供:Analog Devices)

図8:HMC3716の外部リファレンスを500MHz、外部LOを4.5GHzとした場合の、5GHz出力におけるシングルサイドバンドの位相ノイズ。(画像提供:Analog Devices)

図8では、LO2とHMC3716の入力は、SMA100BのRFおよびマイクロ波信号発生器です。評価ボードのLO2の帯域内ノイズは約-135dBc/Hzで、300kHzまでの低オフセットで明らかになります。LO2、ADF4401Aモジュール、HMC3716 PFD、ループフィルタにより、帯域内ノイズは約-140dBc/Hzとなっています。内部の位相ノイズは5MHzから50MHzの間に現れ、セットアップの位相ノイズフロアは約-160dBc/Hzです。これらを合計すると、rmsのジッタは12.53fsとなります。

まとめ

高速計測システムでは、出力データに妥協を許さないために、極めて低いジッタのクロックが必要です。技術者にとっての課題は、高速ギガヘルツクロックシステムを構築できる適切なデバイスを見つけることです。ADF4401A変換ループは、クロックシステムを構築するためのデバイス選択を大幅に簡素化し、高い周波数で低ジッタを保証するコンパクトなモジュールを提供します。また、基板面積やコストを削減し、市場投入までの時間を短縮することができます。

免責条項:このウェブサイト上で、さまざまな著者および/またはフォーラム参加者によって表明された意見、信念や視点は、DigiKeyの意見、信念および視点またはDigiKeyの公式な方針を必ずしも反映するものではありません。