RISC-Vの紹介

RISC-Vは比較的新しいコンピュータ技術であり、多くの有償アーキテクチャに競合する技術として積極的なプロモーションが展開されています。

RISCは「Reduced Instruction Set Computer(縮小命令セットコンピュータ)」の略称です。 また、Vはローマ数字の5です。つまりRISC-Vは、1つのコンピュータコアファミリの第5世代を表しており、 「リスクファイブ」と発音します。 他の大半のISA設計とは異なり、RISC-V ISAはオープンソースライセンスとして無償で提供されます。 RISC-Vはライセンスが不要なオープンソースおよびオープンアーキテクチャであるため、設計を変更したり、特別な命令を作成して性能を強化したり、ハッカーが入り込むのを難しくしたりすることができます。詳細については、こちらのリンクからRISC-V紹介ガイドの電子書籍をご覧ください。

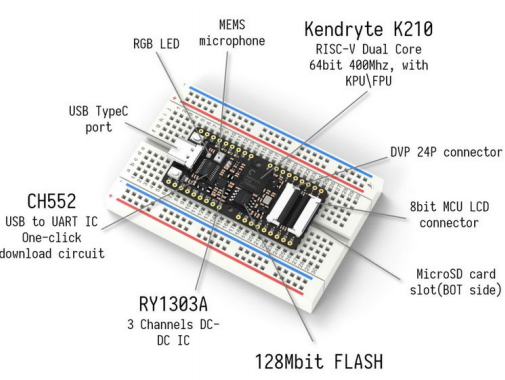

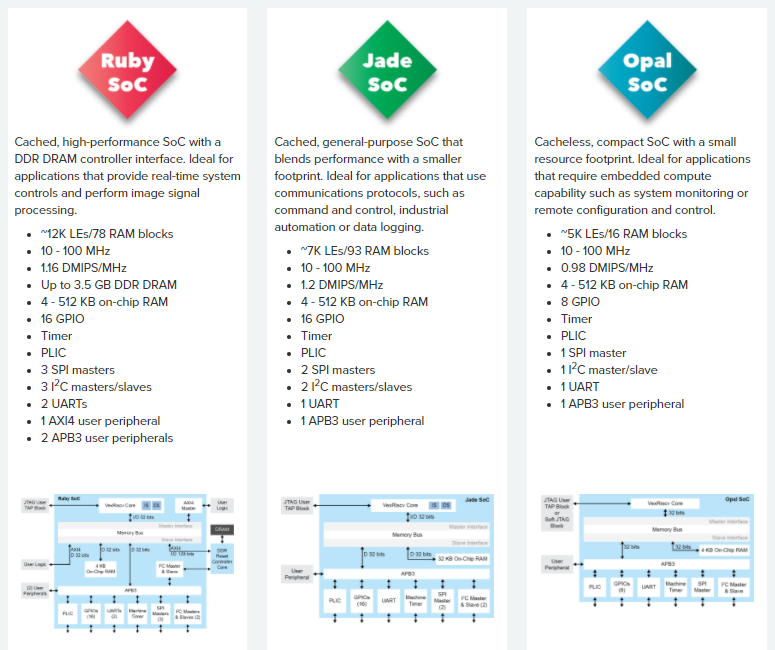

増えつつある製品およびサプライヤの中で、Microchip、Seeed、Xilinx、Digilentなどの製品を以下でご紹介します。

Related Content

専用IPとソフトウェアにより、FPGAの経験がない開発者でもFPGAベースのエッジAIを迅速に展開することができます。

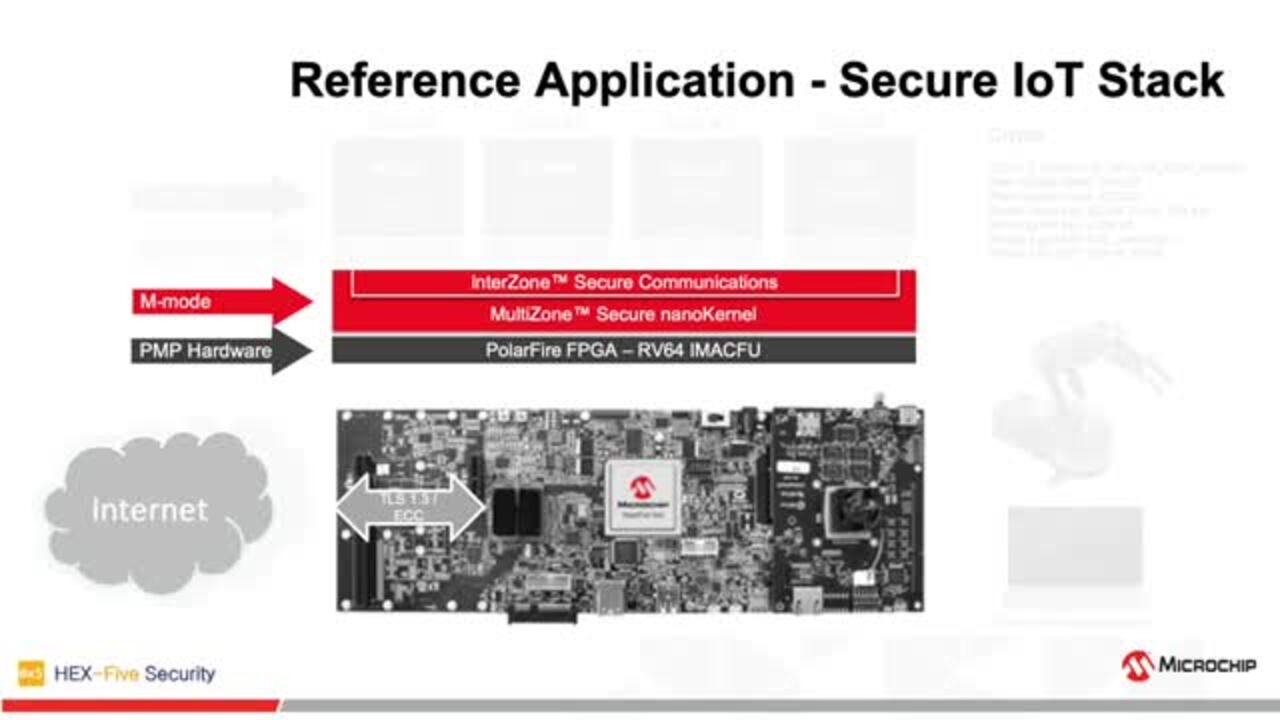

This session will appeal to anyone with an interest in embedded security in general and in RISC-V in particular.

The MultiZone™ demo shows how to secure the deterministic behavior of mixed-criticality systems where Linux and Real-Time come together in a single PolarFire SoC device.

Introduction to RISC V

Introduction to RISC V

A quick introduction to, and overview of the open-source RISC-V architecture.

開発者は、Intel(Altera)製FPGAやその他のプログラム可能なデバイスを、極めて幅広いアプリケーションで利用することができます。