FPGAを使用して、高性能で電力効率の高いエッジAIアプリケーションを素早く構築します。

DigiKeyの北米担当編集者の提供

2021-01-12

エッジの推論プロセッサに人工知能(AI)アルゴリズムを実装しようとしている設計者は、処理需要の増加に伴い、消費電力と開発時間の削減を常に迫られています。フィールドプログラマブルゲートアレイ(FPGA)は、エッジAIに必要なニューラルネットワーク(NN)推論エンジンを実装するために速度と電力効率の特に効果的な組み合わせを提供します。しかし、FPGAに慣れていない開発者にとっては、従来のFPGA開発手法は複雑に見えてしまい、最適なソリューションを見つけにくくなってしまうことがよくあります。

この記事では、Microchip Technologyのシンプルなアプローチについて説明します。このアプローチでは、開発者は従来のFPGA開発を回避して、 FPGAとソフトウェア開発キット(SDK)を使用してトレーニングされたNNを作成することができます。または、FPGAベースのビデオキットを使用して、スマートな組み込みビジョンアプリケーションの開発にすぐに移行できます。

エッジでAIを使う理由

エッジコンピューティングは、産業用オートメーション、セキュリティシステム、スマートホームなど、さまざまな分野でモノのインターネット(IoT)アプリケーションに多くのメリットをもたらします。工場現場を対象とした産業用IoT(IIoT)アプリケーションにおいて、エッジコンピューティングは、クラウドベースのアプリケーションへの往復の遅延をなくすことで、プロセス制御ループの応答時間を劇的に向上させることができます。同様に、エッジベースのセキュリティシステムやスマートホームのドアロックは、クラウドへの接続が誤って、あるいは意図的に失われた場合でも機能を継続することができます。多くの場合、これらのアプリケーションのいずれかでエッジコンピューティングを使用すると、製品のクラウドリソースへの依存度が低下するため、全体的な運用コストを削減できます。開発者は、自社製品の需要の増加に伴い、高価なクラウドリソースを追加するという予期せぬニーズに直面するのではなく、自社製品に組み込まれたローカル処理機能に依存することで、より安定した運用コストを維持することができます。

機械学習(ML)推論モデルが急速に受け入れられ、需要が増加していることで、エッジコンピューティングの重要性が飛躍的に高まっています。開発者にとって、推論モデルのローカル処理は、クラウドベースの推論に必要な応答レイテンシとクラウドリソースのコストを削減するのに役立ちます。ユーザーにとっては、ローカル推論モデルを使用することで、インターネット接続が失われたり、製品ベンダーのクラウドベースの製品が変更されたりしても、製品が機能し続けるという安心感が得られます。さらに、セキュリティとプライバシーへの懸念は、公共のインターネット上でクラウドに転送されるセンシティブな情報の量を制限するために、ローカル処理と推論の必要性をさらに高める可能性があります。

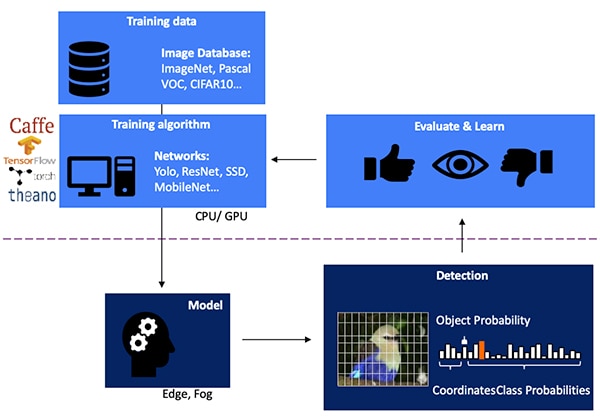

ビジョンベースの物体検出向けのNN推論モデルの開発は、モデルトレーニングから始まる多段階のプロセスであり、通常、公開されているラベル付き画像やカスタムラベル付き画像を使用して、TensorFlowなどのMLフレームワークで実行されます。その処理需要により、モデルトレーニングは通常、クラウドまたは別の高性能コンピューティングプラットフォームのグラフィックスプロセッシングユニット(GPU)を使用して実行されます。トレーニングが完了すると、モデルはエッジまたはフォグコンピューティングリソース上で実行可能な推論モデルに変換され、推論結果はオブジェクトクラスの確率のセットとして提供されます(図1)。

図1:エッジAI向けの推論モデルの実装は、多段階のプロセスの最後にあります。この推論モデルを実装するには、利用可能な、またはカスタムのトレーニングデータを使用して、フレームワークでNNのトレーニングと最適化を行う必要があります。(画像提供:Microchip Technology)

図1:エッジAI向けの推論モデルの実装は、多段階のプロセスの最後にあります。この推論モデルを実装するには、利用可能な、またはカスタムのトレーニングデータを使用して、フレームワークでNNのトレーニングと最適化を行う必要があります。(画像提供:Microchip Technology)

推論モデルが計算上困難な理由

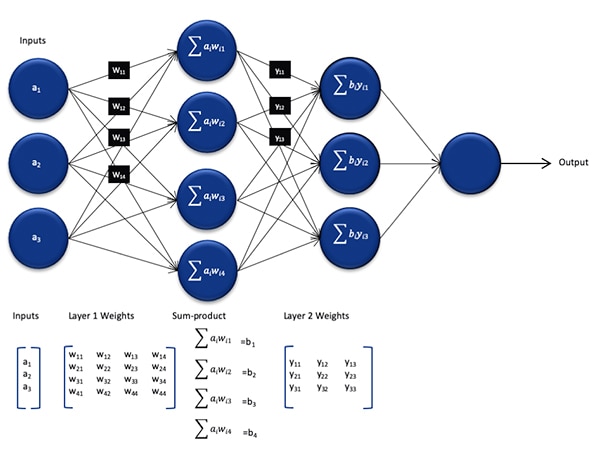

NN推論モデルは、トレーニングプロセスで使用されるモデルに比べてサイズと複雑さが低減されていますが、必要とする計算数が多いため、汎用プロセッサにはまだ計算上の課題が残っています。一般的な形態では、ディープNNモデルは、ニューロンのセットの複数層で構成されています。完全に接続されたネットワークの各層内で、各ニューロンnijは、関連する重み付けwijを使用して各入力の積の合計を計算する必要があります(図2)。

図2:NNでの推論に必要な計算数は、かなりの計算負荷を課す可能性があります。(画像提供:Microchip Technology)

図2:NNでの推論に必要な計算数は、かなりの計算負荷を課す可能性があります。(画像提供:Microchip Technology)

図2には示されていませんが、追加の計算要件があります。この計算要件は、負の値をゼロにマッピングし、1より大きい値を1にマッピングし、類似の関数によって各ニューロンの出力を変更する活性化関数によって課せられます。各ニューロンnijの活性化関数の出力は、次の層i+1への入力として機能し、各層ごとにこのように続けられます。最後に、NNモデルの出力層は出力ベクトルを生成します。この出力ベクトルは、元の入力ベクトル(または行列)が、教師あり学習プロセスの間に使用されたクラス(またはラベル)の1つに対応する確率を表します。

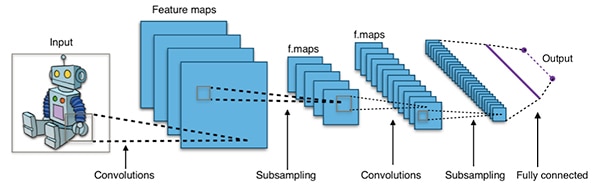

効果的なNNモデルは、上記の代表的な汎用NNアーキテクチャよりもはるかに大きく複雑なアーキテクチャで構築されています。たとえば、画像物体検出に使用される一般的な畳み込みNN(CNN)は、これらの原理を区分的に適用し、入力画像の幅、高さ、色深度をスキャンして一連の特徴マップを生成し、最終的に出力予測ベクトルを生成します(図3)。

図3:画像物体検出に使用されるCNNは、多くの層で多数のニューロンを使用しているため、計算プラットフォームへの要求が大きくなります。(画像提供:Aphex34 CC BY-SA 4.0)

図3:画像物体検出に使用されるCNNは、多くの層で多数のニューロンを使用しているため、計算プラットフォームへの要求が大きくなります。(画像提供:Aphex34 CC BY-SA 4.0)

FPGAを使用してNN数学を高速化

エッジで推論モデルを実行するためのオプションは数多く出てきていますが、エッジでの実用的な高速推論に必要な柔軟性、性能、電力効率を最適に組み合わせたものはほとんどありません。エッジAIにすぐに使用できる代替手段としては、FPGAが特に効果的です。これは、消費電力が比較的少なく、計算集約型の操作をハードウェアベースで高性能に実行できるためです。

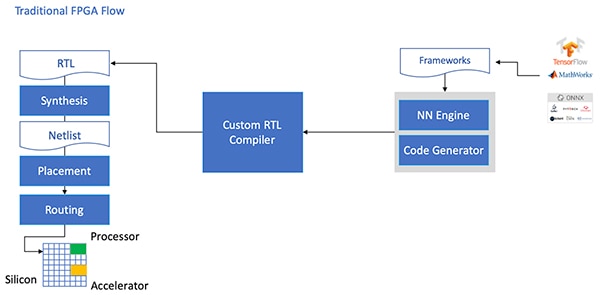

このような利点があるにもかかわらず、FPGAは従来の開発フローのために回避されることがあります。FPGAは、使用経験に乏しい開発者にとっては困難なものになる可能性があります。NNフレームワークで生成されたNNモデルの効果的なFPGA実装を作成するには、開発者は、モデルをレジスタ転送言語(RTL)に変換し、設計を合成するという詳細を理解する必要があります。最後に、最適化された実装を作成するための物理的設計を作成する必要があります(図4)。

図4:FPGAにNNモデルを実装するには、これまで開発者はモデルをRTLに変換して、従来のFPGAフローで作業する方法を理解する必要がありました。(画像提供:Microchip Technology)

図4:FPGAにNNモデルを実装するには、これまで開発者はモデルをRTLに変換して、従来のFPGAフローで作業する方法を理解する必要がありました。(画像提供:Microchip Technology)

Microchip Technologyは、PolarFire FPGA、専用ソフトウェア、関連する知的財産(IP)を通してソリューションを提供しています。このソリューションにより、FPGAの経験のない開発者でも、エッジでの高性能で低電力の推論を幅広く利用できます。

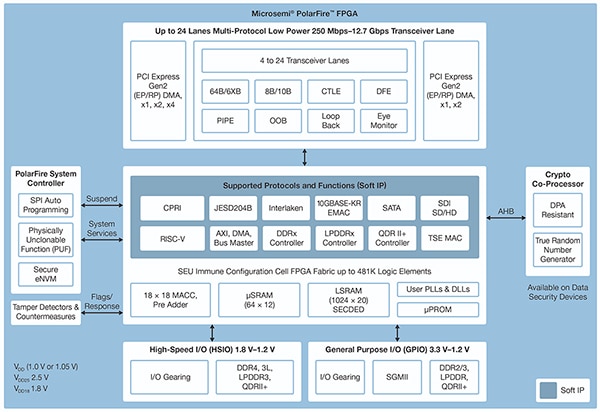

高度な不揮発性プロセス技術で製造されたPolarFire FPGAは、消費電力を最小限に抑えながら、柔軟性と性能を最大限に発揮できるように設計されています。通信や入出力(I/O)用の高速インターフェースが豊富に用意されているほか、RISC-Vプロセッサや高度なメモリコントローラ、その他の標準インターフェースサブシステムなど、ソフトIPコアを使用した高度な機能をサポートするディープFPGAファブリックを備えています(図5)。

図5:Microchip TechnologyのPolarFireアーキテクチャは、計算集約型の推論モデルの実装など、高性能な設計要件をサポートするように設計されたディープファブリックを提供します。(画像提供:Microchip Technology)

図5:Microchip TechnologyのPolarFireアーキテクチャは、計算集約型の推論モデルの実装など、高性能な設計要件をサポートするように設計されたディープファブリックを提供します。(画像提供:Microchip Technology)

PolarFire FPGAファブリックは、MPF100T、MPF200T、MPF300T、MPF500Tシリーズなど、PolarFire FPGAファミリの異なる製品によってさまざまな容量でサポートされている広範なロジックエレメントと特殊ブロックを提供します(表1)。

|

表1:PolarFireシリーズでは、さまざまなFPGAファブリックの特長と容量を利用できます。(表提供:DigiKey、Microchip TechnologyのPolarFireのデータシートに基づく)

推論の高速化で特に興味深い機能の中でも、PolarFireアーキテクチャには、専用の数学ブロックが含まれています。この数学ブロックは、プリ加算器を備えた18ビット x 18ビットの符号付き積和関数(MAC)を提供します。内蔵のドット積モードでは、1つの数学ブロックで2つの8ビット乗算演算を行い、モデル量子化の精度への影響が少ないことを利用して大容量化を図る仕組みを提供しています。

数学演算を高速化するだけでなく、PolarFireアーキテクチャは、NNアルゴリズム実行中に作成された中間結果を保存するための小さな分散メモリなど、汎用アーキテクチャ上で推論モデルを実装する際に発生するメモリの混雑を緩和するのに役立ちます。また、NNモデルの重み付けとバイアス値は、数学ブロックの近くにあるロジックエレメントから構築された、深度16 x 18ビット係数の読み取り専用メモリ(ROM)に保存することができます。

PolarFire FPGAファブリックの他の特長と組み合わせることで、数学ブロックはMicrochip Technologyの高レベルなCoreVectorBlox IPの基盤となります。これは、さまざまなタイプのNNを実行できる柔軟なNNエンジンとして機能します。制御レジスタのセットとともに、CoreVectorBlox IPには3つの主要な機能ブロックが含まれています。

- マイクロコントローラ:Microchipファームウェアのバイナリラージオブジェクト(BLOB)とユーザー固有のNN BLOBファイルを外部ストレージから読み取るシンプルなRISC-Vソフトプロセッサです。ファームウェアBLOBからの命令を実行することで、CoreVectorBloxの全体的な動作を制御します。

- マトリックスプロセッサ(MXP):8つの32ビット算術論理ユニット(ALU)からなるソフトプロセッサです。このソフトプロセッサは、必要に応じて、8ビット、16ビット、32ビット精度の混合の要素別テンソル演算を使用してデータベクトルの並列演算を行うように設計されています。これらの演算の例としては、add、sub、xor、shift、mul、dotprodなどがあります。

- CNNアクセラレータ:MAC関数の2次元配列を使用してMXP操作を高速化します。これらのMAC関数は数学ブロックを使って実装され、8ビット精度で動作します。

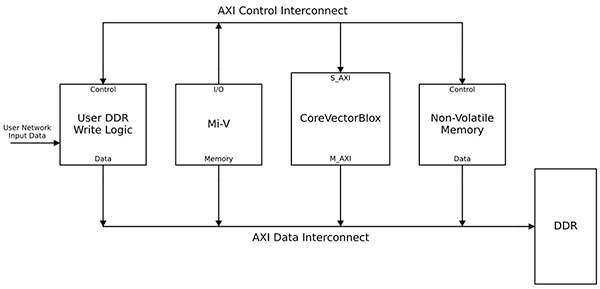

完全なNN処理システムは、CoreVectorBlox IPブロック、メモリ、メモリコントローラ、およびMicrosoft RISC-V(Mi-V)ソフトウェアプロセッサコアなどのホストプロセッサを組み合わせます(図6)。

図6:CoreVectorBlox IPブロックは、MicrochipのMi-V RISC-Vマイクロコントローラなどのホストプロセッサと連携してNN推論モデルを実装します。(画像提供:Microchip Technology)

図6:CoreVectorBlox IPブロックは、MicrochipのMi-V RISC-Vマイクロコントローラなどのホストプロセッサと連携してNN推論モデルを実装します。(画像提供:Microchip Technology)

ビデオシステムの実装では、ホストプロセッサはシステムフラッシュメモリからファームウェアとネットワークBLOBをロードし、CoreVectorBloxブロックで使用するためにダブルデータレート(DDR)ランダムアクセスメモリ(RAM)にコピーします。ビデオフレームが到着すると、ホストプロセッサはそれらをDDR RAMに書き込み、CoreVectorBloxブロックに信号を送り、画像の処理を開始します。ネットワークBLOBで定義された推論モデルを実行した後、CoreVectorBloxブロックは、画像分類を含む結果をターゲットアプリケーションで使用するためにDDR RAMに書き戻します。

開発フローはNN FPGAの実装を簡素化

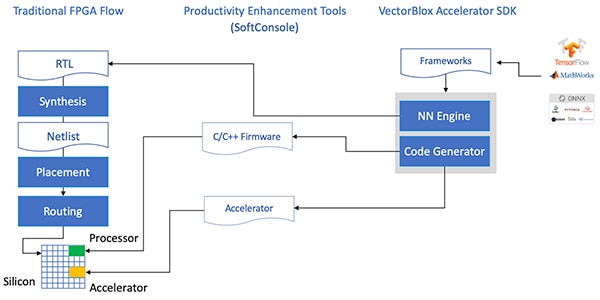

Microchipは、PolarFire FPGAにNN推論モデルを実装する際の複雑さから開発者を守ります。NNモデルの開発者は、従来のFPGAフローの詳細を扱う代わりに、通常通りにNNフレームワークを使用して作業を行い、その結果得られたモデルをMicrochip TechnologyのVectorBloxアクセラレータソフトウェア開発キット(SDK)にロードします。SDKは、通常のFPGA開発フローに必要なファイルや、前述のファームウェアおよびネットワークBLOBファイルなど、必要なファイルのセットを生成します(図7)。

図7:VectorBloxアクセラレータSDKは、FPGAにNNモデルを実装する際の詳細を管理し、FPGAベースの推論モデルの設計と実行に必要なファイルを自動的に生成します。(画像提供:Microchip Technology)

図7:VectorBloxアクセラレータSDKは、FPGAにNNモデルを実装する際の詳細を管理し、FPGAベースの推論モデルの設計と実行に必要なファイルを自動的に生成します。(画像提供:Microchip Technology)

VectorBloxアクセラレータSDKフローは、FPGAに実装されたNNエンジンにNN設計をオーバーレイするため、FPGA設計の合成フローをやり直すことなく、異なるNNを同じFPGA設計上で実行することができます。開発者は、結果として得られるシステム用のC/C++コードを作成し、システム内のモデルをその場で切り替えたり、タイムスライシングを使用してモデルを同時に実行したりすることができます。

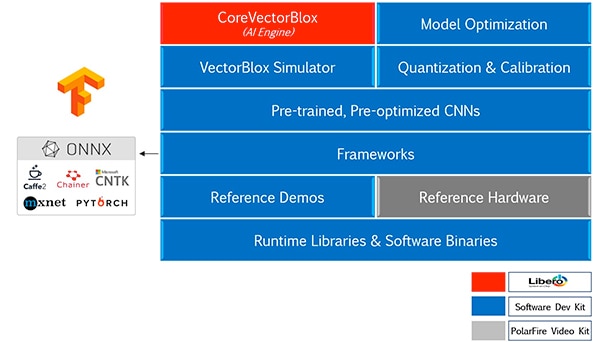

VectorBloxアクセラレータSDKは、Microchip TechnologyのLibero FPGA設計スイートとNN推論モデル開発のための包括的な機能セットを統合しています。モデルの最適化、量子化、較正サービスに加えて、SDKはNNシミュレータを提供しています。このNNシミュレータにより、開発者は同じBLOBファイルを使用して、FPGAハードウェア実装で使用する前にモデルを評価することができます(図8)。

図8:VectorBloxアクセラレータSDKは、フレームワークで生成された推論モデルのFPGA実装を最適化するために設計された包括的なサービスセットを提供します。(画像提供:Microchip Technology)

図8:VectorBloxアクセラレータSDKは、フレームワークで生成された推論モデルのFPGA実装を最適化するために設計された包括的なサービスセットを提供します。(画像提供:Microchip Technology)

VectorBloxアクセラレータSDKは、Open Neural Network Exchange(ONNX)フォーマットのモデルだけでなく、TensorFlow、Caffe、Chainer、PyTorch、MXNETなどの多くのフレームワークのモデルもサポートしています。サポートされているCNNアーキテクチャには、MNIST、MobileNetバージョン、ResNet-50、Tiny Yolo V2、Tiny Yolo V3などがあります。Microchipは、オープンソースOpenVINOツールキット向け事前トレーニング済みモデルのopen model zooに、ほとんどのネットワークを追加するため、サポートの拡大に取り組んでいます。open model zooのモデルには、Yolo V3、Yolo V4、RetinaNet、SSD-MobileNetなどが含まれています。

ビデオキットでFPGA推論をデモ

開発者がスマートな組み込みビジョンアプリケーション開発に迅速に移行できるように、Microchip Technologyは、同社のMPF300-VIDEO-KIT PolarFire FPGAビデオおよびイメージングキットとリファレンス設計で動作するように設計された包括的なサンプルアプリケーションを提供しています。

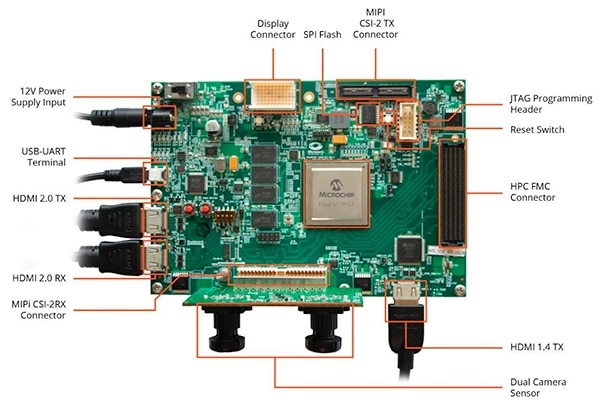

MicrochipのMPF300T PolarFire FPGAをベースにしたこのキットのボードは、デュアルカメラセンサ、ダブルデータレート4(DDR4)RAM、フラッシュメモリ、電源管理、各種インターフェースを組み合わせています(図9)。

図9:MPF300-VIDEO-KIT PolarFire FPGAビデオおよびイメージングキットと関連ソフトウェアにより、開発者はスマートな組み込みビジョンアプリケーションでFPGAベースの推論を素早く始めることができます。(画像提供:Microchip Technology)

図9:MPF300-VIDEO-KIT PolarFire FPGAビデオおよびイメージングキットと関連ソフトウェアにより、開発者はスマートな組み込みビジョンアプリケーションでFPGAベースの推論を素早く始めることができます。(画像提供:Microchip Technology)

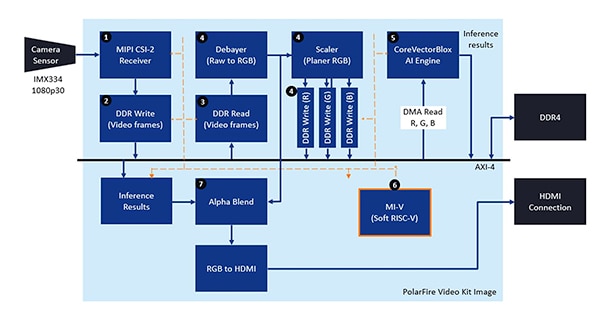

このキットには、ファームウェアとネットワークBLOBファイルを生成するためのLibero設計プロジェクト一式が付属しています。開発者は、BLOBファイルをオンボードのフラッシュメモリにプログラミングした後、Liberoの実行ボタンをクリックしてデモを開始し、カメラセンサからのビデオ画像を処理して推論結果をディスプレイに表示できます(図10)。

図10:Microchip TechnologyのPolarFire FPGAビデオおよびイメージングキットは、スマートな組み込みビジョンシステムのFPGA実装を設計し使用する方法を実証します。この組み込みビジョンシステムは、MicrochipのCoreVectorBlox NNエンジンをベースに構築されています。(画像提供:Microchip Technology)

図10:Microchip TechnologyのPolarFire FPGAビデオおよびイメージングキットは、スマートな組み込みビジョンシステムのFPGA実装を設計し使用する方法を実証します。この組み込みビジョンシステムは、MicrochipのCoreVectorBlox NNエンジンをベースに構築されています。(画像提供:Microchip Technology)

各入力ビデオフレームについて、FPGAベースのシステムは次のステップを実行します(ステップ番号は図10に対応しています)。

- カメラからフレームをロードする

- フレームをRAMに保存する

- RAMからフレームを読み取る

- 生の画像をRGBに変換し、プレーナRGBに変換し、その結果をRAMに保存する

- Mi-VソフトRISC-Vプロセッサは、CoreVectorBloxエンジンを起動する。CoreVectorBloxエンジンは、RAMから画像を取り出して推論を行い、分類確率の結果をRAMに保存する

- Mi-Vでは、結果を利用してバウンディングボックスや分類結果などのメタデータを含むオーバーレイフレームを作成し、RAMに保存する

- オリジナルフレームとオーバーレイフレームを融合してHDMIディスプレイに書き込む

デモではTiny Yolo V3とMobileNet V2モデルのアクセラレーションをサポートしていますが、開発者は、2つのデフォルトモデルを含む既存のリストにモデル名とメタデータを追加する小さなコード変更を行うことで、上記で述べた方法で他のSDKサポートモデルを実行することができます。

まとめ

NNモデルなどのAIアルゴリズムは通常、計算集約型の負荷を課します。このような負荷は、汎用プロセッサで利用可能なリソースよりも高性能な計算リソースを必要とします。FPGAは、推論モデル実行の性能と低電力の要件を十分に満たすことができますが、従来のFPGA開発手法は複雑に見え、開発者はしばしば最適でないソリューションを選択してしまうことがあります。

前述のように、Microchip Technologyの特殊なIPとソフトウェアを使用することで、FPGAの経験のない開発者でも、推論ベースの設計を実装することができ、性能、電力、設計スケジュールの要件を満たすことが可能になります。

免責条項:このウェブサイト上で、さまざまな著者および/またはフォーラム参加者によって表明された意見、信念や視点は、DigiKeyの意見、信念および視点またはDigiKeyの公式な方針を必ずしも反映するものではありません。