RISC-Vのアトミック拡張機能で優れたビット操作機能を提供する方法

RISC-Vアーキテクチャの採用率は雪だるま式に増加しており、もっともな理由により、業界内でその影響力が高まっています。

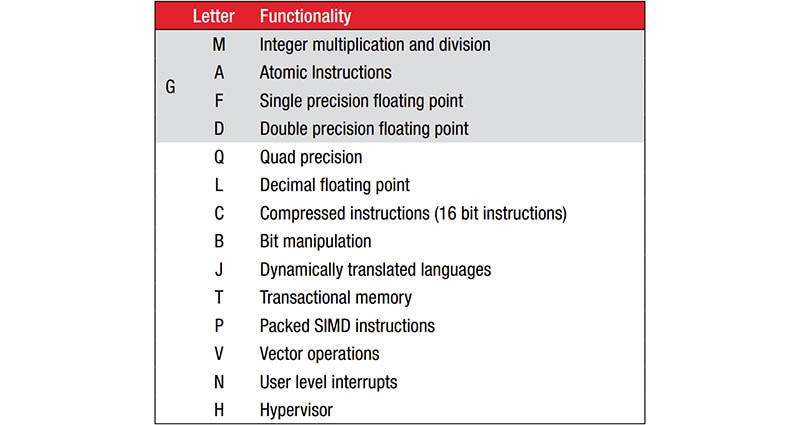

RISC-Vは、コアアーキテクチャとその真の縮小命令セットアーキテクチャ(ISA)に加えて、標準化された一連の拡張機能によって強化されています(図1)。たとえば、単精度浮動小数点と圧縮命令をサポートする32ビットRISC-Vコア(RV32)は、図の拡張リストに基づいてRV32FCと指定されています。

図1:RISC-V ISAは、標準化された一連の命令拡張機能によって強化されており、コア名の後の文字サフィックスで示されています。(画像提供:RISC-V.org)

図1:RISC-V ISAは、標準化された一連の命令拡張機能によって強化されており、コア名の後の文字サフィックスで示されています。(画像提供:RISC-V.org)

多くの人工知能(AI)や機械学習(ML)アプリケーションおよび高度な組み込みシステムにとって、最も必要な4つの拡張機能は、整数の乗除算(M)、アトミック命令(A)、単精度浮動小数点(F)、倍精度浮動小数点(D)です。しかし、「RV32MAFD」としてコアを指定するのではなく、「RV32G」のようにGサフィックスでまとめられています。

さまざまな拡張機能やRISC-V全般については、EDUサイトにあるDigiKeyのRISC-V電子ブックを参照してください。

私の場合、高度な組み込みシステムで初めてプロセッサを扱う経験をしたので、データメモリ上のアーキテクチャのリード、モディファイ、ライトのビット操作サポートに注目する傾向があります。これらのアプリケーションでは、ペリフェラルレジスタやセマフォのビットの設定とクリアが非常に一般的です。ネイティブのビット操作命令がない場合、コアはデータメモリロケーションの内容をコアレジスタにコピーし、OR、AND、XOR命令でビットをセット、クリア、トグルし、その結果をデータメモリロケーションに戻す必要があります。これには別途時間がかかるだけでなく、一部の組み込み制御アプリケーションでは、コードの肥大化が20%にも達するケースも見られます。

アプリケーションによっては、コードの肥大化や性能の低下を許容できる場合もあります。しかし、これらの3つの命令が処理されている間に、割り込みによってプログラム制御が突然取り除かれる場合があります。さらに悪いことに、マルチプロセッサシステムでは、別のコアがそのメモリロケーションから読み出しを行う可能性もあります。これらのイベントがデータメモリを破壊しないように、割り込みを無効にしたり、メモリをロックしたりするには、追加の命令や複雑な処理が必要となり、性能上の問題が生じます。

Armは、単純なビット演算で動作するビットバンディングを実装することで、このような問題の解決を試みました。しかし、私の意見では、RISC-Vはよりエレガントで柔軟なソリューションを実装しました。

アトミック拡張機能が非常にエレガントな理由

RISC-V A(アトミック)拡張機能は、ここでは説明しないLoad-Reserved/Store-Conditional命令と、データメモリ上で簡単なビット操作を行うバイナリ/ビット単位命令という、2つの操作をサポートしています。RISC-V Bビット操作拡張機能は、一連の複雑なビット制御命令をサポートしていますが、アトミック拡張機能は、マルチプロセッサシステムだけを対象としたものではありません。これは、必要なビット操作がよりシンプルな、小型の組み込みシステムにも役立ちます。このようなシステムの例として、Seeed Technologyの114991684デュアルコア、64ビット、RISC-Vモジュールがあります。このモジュールは、2つのRV64GCコアを搭載しており、共有されたデータSRAMと協調して動作する必要があります。

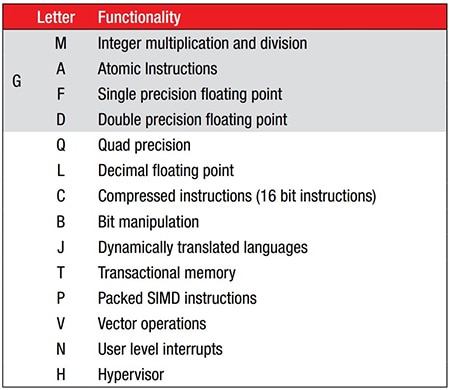

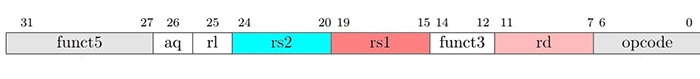

RISC-V A拡張機能のアトミックメモリ操作(AMO)のフォーマットを、図2に示します。

図2:RISC-VのAMO命令フォーマットは、たった1つの命令でデータメモリ上のアトミックバイナリ演算をサポートしています。(画像提供:RISC-V.org(ビル・ジオビーノによる改良)

図2:RISC-VのAMO命令フォーマットは、たった1つの命令でデータメモリ上のアトミックバイナリ演算をサポートしています。(画像提供:RISC-V.org(ビル・ジオビーノによる改良)

AMOは、rs1で示されたデータメモリに直接、1つの命令でさまざまなバイナリ演算をサポートする、強力なリードモディファイライト命令です。図2を参照すると、この演算はrs1のデータメモリのアドレス位置の内容をロードし、その値をレジスタrdに格納します。次に、rdの値とrs2の値でバイナリ演算を実行し、その結果をrdに格納し、rs1のデータメモリのアドレス位置に戻します。

対応するビット演算は、OR(ビットセット)、AND(ビットクリア)、XOR(ビットトグル)です。これにより、データメモリ上で直接、1つ以上のビットのアトミックビット操作が可能になります。また、2つのRV64GCコアが同時に同じメモリアドレスを使用している場合のメモリ衝突を防止します。これは、小型の組み込みアプリケーションでメモリ内のペリフェラルレジスタを構成する際に非常に有用であり、またセマフォの操作も簡素化されます。

RISC-VのAMOがサポートするその他の演算は、整数の最大値、整数の最小値、およびスワップです。また、データメモリ内のカウンタを直接インクリメントするなど、直接的な2進加算が可能なBinary ADDにも対応しています。

RV64コアは、32ビットと64ビットの両方の演算に対応しています。RV64でのビット操作では、rdに配置された32ビットデータを符号拡張するため、64ビットデータのみで動作することが重要です。

まとめ

RISC-V ISAは、Arm ISAに挑戦する最初の本格的な候補です。そのISA拡張機能は、アプリケーションの性能をコスト効率よく向上させる命令によってコアを強化するための、標準化された方法を提供します。私は特に、オプションのアトミック拡張機能に期待しています。

アトミック拡張機能は、マルチプロセッサシステムでは有用でほぼ必須ですが、データメモリ上で直接ビット操作制御を行う効率的な方法でもあります。これは、コードサイズの縮小と性能の向上により、既存の多くのアーキテクチャと比較して大きな利点をもたらします。

Have questions or comments? Continue the conversation on TechForum, Digi-Key's online community and technical resource.

Visit TechForum