SiCベースのMOSFETを使用したパワー変換効率の改善

DigiKeyの北米担当編集者の提供

2019-10-29

厳しさを増す電力要件、規制上の義務、効率基準、そしてEMI問題により、効率が高く動作範囲の広いスイッチング電源デバイスへのニーズが高まっています。同時に、設計者たちは常に、コスト削減と省スペース化のプレッシャーにさらされています。こうした要求に応えるため、従来のシリコン(Si)ベースのMOSFETに代わるものが求められています。

シリコンカーバイド(SiC)は成熟して第3世代となり、今や有力な選択肢となりました。SiCベースのFETは性能面で、効率性、信頼性の向上、熱管理上の問題の少なさ、実装面積の小ささをはじめとする、多くの利点を持っています。これらの利点は電力スペクトラム全体で享受でき、設計手法に若干の調整は必要になるかもしれませんが、大幅な変更は必要ありません。

この記事では、SiとSiCを簡単に比較し、WolfspeedのSiCデバイスの例をご紹介し、それらを使用した設計の始め方についてご説明します。

SiC MOSFETとSi MOSFETの比較

まず重要なのは、技術と関連用語を明確にしておくことです。SiCベースのFETは、これまでのシリコンベースのFETと同様に、MOSFETです。大ざっぱに言えば、この2つの内部の物理構造は同じであり、どちらも、ソース、ドレイン、ゲートを接続する3つ端子を持つデバイスです。

違いは、名前から分かるように、SiCベースのFETでは基材に、シリコン単独ではなく、シリコンカーバイドを使用している点です。業界ではこれを、MOSFETを付けずに、SiCデバイスと呼ぶことが多くあります。この記事では、SiC FETと呼ぶことにします。

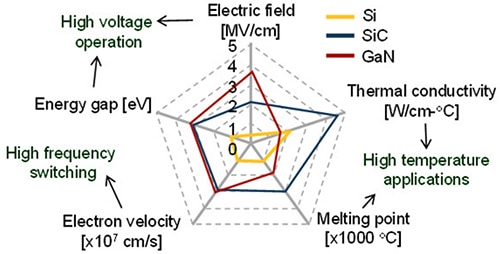

なぜ、素材としてSiC化合物を使うのでしょうか?さまざまな訳ありの物理的理由から、SiCには3つの重要な電気特性があり、シリコンとの大きな違いとなっており、それぞれの特性が動作上の利点をもたらします。そのほかに、それほど目立たない特長もいくつかあります(図1)。

図1:SiC、Si、およびGaNの固体材料の主要な材料特性の大まかな比較。Siに比べて、SiCは破壊強度が高く、熱伝導率が高く、バンドギャップが広くなっています。(画像提供:Researchgate)

図1:SiC、Si、およびGaNの固体材料の主要な材料特性の大まかな比較。Siに比べて、SiCは破壊強度が高く、熱伝導率が高く、バンドギャップが広くなっています。(画像提供:Researchgate)

3つの特性とは、以下のとおりです。

- Siでは破壊電界強度が1センチメートルあたり0.3メガボルト(Mvolts/cm)なのに対し、SiCでは2.8Mvolts/cmと高くなっています。そのため、同じ電圧定格でも、ずっと薄い膜厚で動作可能となり、オン抵抗を大幅に抑えられます。

- 熱伝導率が高いため、断面積における電流密度を高くできます。

- バンドギャップ(半導体(および絶縁体)の価電子帯の上部から、伝導帯の下部までのエネルギー幅(単位:eV))が広いため、高温でのリーク電流を低く抑えられます。こうした理由から、SiCダイオードとFETはよく、ワイドバンドギャップ(WBG)デバイスと称されます。

結果として、大まかに言うと、SiCベースのデバイスはシリコンデバイスの最大10倍の耐圧を持ち、25°Cではオン抵抗が半分以下になるため、約10倍の速さでスイッチングができます。同時に、シリコンの125°Cに対し、SiCは200°Cという高温での動作が可能なため、熱設計と熱管理が容易になります。

利点を発揮するために不可欠なゲートドライバ

電源デバイスはゲートドライバなしでは機能しません。ゲートドライバは、低レベルのデジタル制御信号を、電源デバイスが求めるタイミングに従い、必要な電流信号および電圧信号に変換します(同時に、ほとんどの種類の外部障害にも対策を施します)。SiC FETの場合、ドライバで以下のことを行うために追加機能が必要です。

- 伝導損失、スイッチング損失、およびゲート損失を最小限に抑えること。こうした損失には、ターンオンおよびターンオフエネルギー、ミラー効果、ゲート駆動の電流要件が含まれます。ターンオフエネルギーは、オフ状態におけるゲート抵抗とゲート~ソース間電圧の作用です。これを低減するには、より大きな電流をゲートから放電する必要があります。そのための方法の1つは、ターンオフ時にドライバでゲート電圧に負バイアスをかけることです。同様に、ターンオンエネルギーはゲート抵抗を下げることで低減できます。

- ミラー効果とその悪影響を最小限に抑えること。特定の条件やアプリケーション構成で、寄生静電容量により、意図しないターンオンが発生する可能性があります。このミラー効果が引き起こすターンオンにより、逆回復エネルギーが増加し、損失が増えます。解決策の1つは、ドライバにミラークランプ保護と呼ばれる機能を持たせ、電力段のスイッチング時に駆動電流を制御することです。

- 適切な電圧で、必要なシンク電流およびソース電流を提供すること。SiCデバイスは通常、損失を抑えるために、シリコンMOSFETよりも高い正バイアスのゲート駆動(20V以上)を必要とします。負のオフゲート電圧(-2~-6V)を必要とする場合もあります。必要なゲート電流は、ゲート電荷(Qg)、VDD、ドレイン電流ID、ゲート~ソース間電圧、ゲート抵抗に基づいた通常の計算で決定され、多くの場合は数アンペア程度です。この電流には、SiC FETのスイッチング速度に応じたスルーレートにおいて、適切なシンクおよびソース定格が必要です。

- ボードおよびデバイスの寄生(浮遊インダクタンスおよびキャパシタンスの両方)をモデル化および最小化すること。SiC FETデバイスの高速なスイッチングではこれが、振動、電圧および電流のオーバーシュート、誤トリガの原因になります。シリコンMOSFETにはわずかな「テール」電流があるのですが、これがダンパまたはスナバとして機能し、オーバーシュートとリンギングをある程度軽減します。SiC MOSFETにはこのテールがないため、ドレイン電圧のオーバーシュートとリンギングが大きくなる可能性があります。こうした寄生を軽減させるためには、導体の長さを最小限にする、ドライバをできるだけ電源デバイスの近くに配置するなど、レイアウトに関して慎重な配慮が必要です。SiC FETの高速なスイッチングでは、この浮遊インダクタンスおよびキャパシタンスが顕著になるため、わずか数センチでも、違いが出ることがあります。リンギングの軽減には、第2の利点もあります。デバイスの駆動側と負荷側の両方で、高速スイッチングに伴うEMIの発生を抑えられるからです。

このようにSiC MOSFETの駆動には新たな問題があるものの、この用途向けに設定された標準的なICが多くのベンダーから出ており、それらはSiCデバイス特有のニーズに合った属性を持っています。ただし設計においては多くの場合、ゲートドライバとSiC FETを低電圧回路からガルバーニ絶縁する必要があります。これは、光学的なパルストランスか、容量性絶縁技術により、標準的なコンポーネントを使用して実装できます。この絶縁は、第1に安全面で、回路の動作不良時に高電圧からユーザーを守るために必要です。そして第2に、多くの回路トポロジにおいて、たとえばブリッジ構成などでは、MOSFETはもともと接地されません。

新しいデバイスで性能を発揮

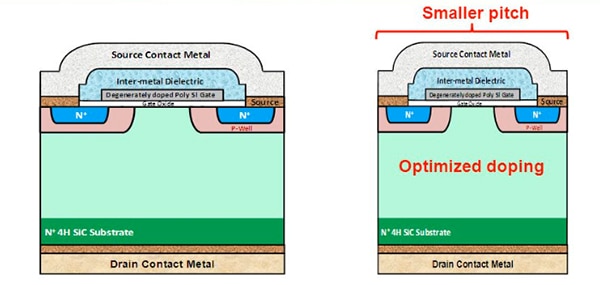

初めてのSiC MOSEFT市販パッケージであるCMF20120Dは、Wolfspeedから2011年1月に発売されました(WolfspeedはWolfspeed社の電源およびRF部門。この名称は2015年に発表)。ちなみに、SiCウェハが発売されたのは、その数年前になります。CMF20120Dは、定格1200V/98A、オン抵抗80mΩ(すべて25⁰C)で、TO-247パッケージに組み込まれていました。Wolfspeed社は間もなく第2世代プロセスをリリースしました。そして現在は、C3Mデバイス向けに設計された第3世代のSiC MOSEFTを提供しています(図2)。

図2:Wolfspeed’s Wolfspeed社の第2世代(左)と第3世代(右)のSiCプロセス構造を比較すると、多少の違いがあることが分かります。しかし、この断面図から、性能仕様における結果的な改善までは分かりません。 (画像提供:Wolfspeed)

図2:Wolfspeed’s Wolfspeed社の第2世代(左)と第3世代(右)のSiCプロセス構造を比較すると、多少の違いがあることが分かります。しかし、この断面図から、性能仕様における結果的な改善までは分かりません。 (画像提供:Wolfspeed)

たとえば、業界の草分け的な900VのSiC MOSFETプラットフォームの1つがC3M0280090Jです。再生可能エネルギーインバータ、電気自動車充電システム、産業用3相電源など、高周波パワーエレクトロニクスアプリケーション向けに最適化されています。

|

表1:Wolfspeed社のC3M0280090J SiC MOSFETの主な属から、再生可能エネルギーインバータ、電気自動車充電システム、産業用3相電源に最適であることが分かります。(表提供:Wolfspeed)

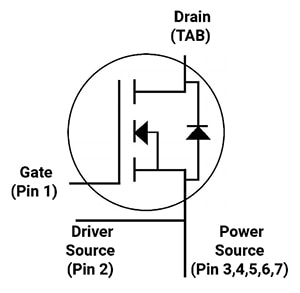

電圧および電流の仕様に加えて、このデバイスは低キャパシタンスの高速スイッチングに最適化されており、ドライバソースピン付きの低インピーダンスパッケージを採用し(図3)、逆回復率(Qrr)が低い高速真性ダイオードを搭載し、ドレイン~ソース間の距離を広く(~7mm)とっています。

図3:Wolfspeed C3M0280090Jは、ドライバソースピン付きの低インピーダンスパッケージを採用しています。(画像提供:Wolfspeed)

図3:Wolfspeed C3M0280090Jは、ドライバソースピン付きの低インピーダンスパッケージを採用しています。(画像提供:Wolfspeed)

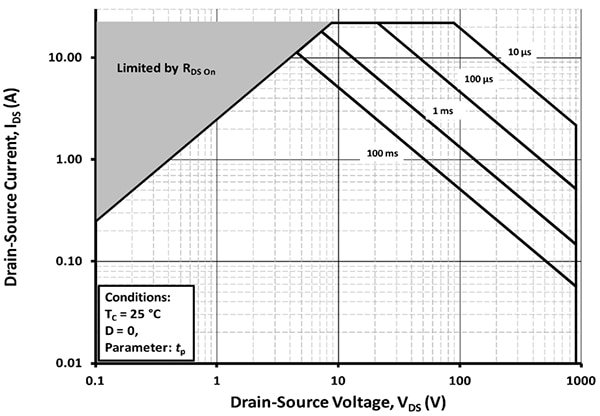

この900Vプラットフォームは、シリコンベースのソリューションと同等コストながら、仕様は向上しており、より小型かつより高効率の次世代パワー変換システムを実現します。安全動作域(SOA)グラフに、このSiC FETの性能をまとめました(図4)。ドレイン~ソース間電圧(VDS)が低いとき、最大電流はオン状態抵抗によって制限されます。また中程度のVDSにおいては、15Aを短時間維持できます。

図4:Wolfspeed C3M0280090JのSOAグラフに、IDSおよびVDS性能の相関を示します。(画像提供:Wolfspeed)

図4:Wolfspeed C3M0280090JのSOAグラフに、IDSおよびVDS性能の相関を示します。(画像提供:Wolfspeed)

パッケージングが性能に影響

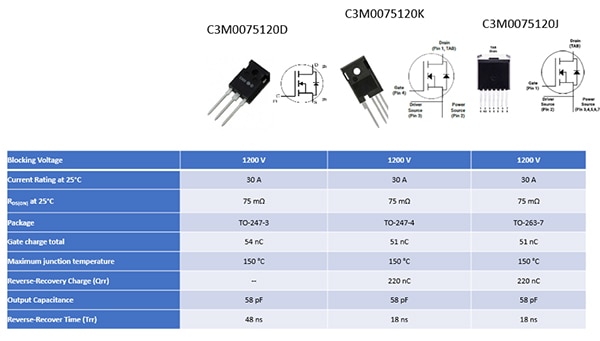

Wolfspeed社はこのほかに、C3M0075120D、C3M0075120K、C3M0075120Jという3種類のデバイスを提供しています。それぞれ似たような仕様ですが、パッケージに大きな違いがあります(図5)。

図5:Wolfspeed社は、3種類のパッケージで、いずれも1200VのSiC FETを提供しています。仕様はよく似ていますが、完全に同じではありません。(画像提供:Wolfspeed)

図5:Wolfspeed社は、3種類のパッケージで、いずれも1200VのSiC FETを提供しています。仕様はよく似ていますが、完全に同じではありません。(画像提供:Wolfspeed)

ほとんどのことが数字で分かりますが、それ以外に知っておくべきことがあります。末尾がDのデバイスは、端子が3つのパッケージ(TO-247-3)で提供されるのに対し、末尾がKのデバイスは端子が4つのパッケージ(TO-247-4)で提供されます。この2種類のデバイスと、端子が7つある末尾がJのデバイスには、ケルビンソースピンがあります。これは、ゲート回路においてL × di/dtで引き起こされる電圧急上昇の影響を軽減します。そうすることで、ゲートとソースにより大きな電圧をかけられるようになり、より高速でダイナミックなスイッチングが可能になります。その結果から、定格電流近くで測定した場合は、スイッチング損失を3.5分の1まで減らせる可能性があると分かります。

評価ボードとリファレンス設計で成功を加速

ギガヘルツ周波数のRF設計とは対極にあるものの、より高い電圧および電力範囲での動作のために高性能な回路を作成するには、やはり細部への注意が必要です。コンポーネントやレイアウトのあらゆる機微や特異性が増幅され、物理回路にはささいな問題や見落としも許されません。

C3M0075120DやC3M0075120KなどSiC FETの評価を支援するために、Wolfspeed社はこれらのデバイスの高速スイッチング性能を実際に試すためのバックブースト評価キットKIT-CRD-3DD12Pを提供しています。(図6)。端子が3つのパッケージC3M0075120Dと、端子が4つであること以外は同じパッケージC3M0075120Kの両方に対応するよう作られています。そのため、Wolfspeedの第3世代(C3M)MOSFETの性能を異なるパッケージでテストし、比較できます。

図6:評価キットKIT-CRD-3DD12Pにより、端子が3つのTO-247パッケージを使用したC3M0075120Dと、端子が4つのC3M0075120Kの両方の性能を評価しやすくなります。大きなヒートシンクとトロイダルインダクタによって、高い熱性能を発揮することに留意してください。(画像提供:Wolfspeed)

図6:評価キットKIT-CRD-3DD12Pにより、端子が3つのTO-247パッケージを使用したC3M0075120Dと、端子が4つのC3M0075120Kの両方の性能を評価しやすくなります。大きなヒートシンクとトロイダルインダクタによって、高い熱性能を発揮することに留意してください。(画像提供:Wolfspeed)

評価キットは、ハーフブリッジ構成で提供します。上側か下側にMOSFETまたはダイオードを追加できるため、同期降圧または同期昇圧など、一般的なパワー変換トポロジでボードを構成できます。また、最上部か最下部にダイオードを追加できるため、非同期降圧または非同期昇圧のコンバータトポロジを評価できます。

さらに、電力損失を減らすために、このキットには、「センダスト」でできた低損失インダクタが付属します。Kool Mµとも呼ばれる、この磁性金属粉は、鉄85%、シリコン9%、アルミ6%という構成であり、パーマロイに代わって使用されています。そのほうが、磁気および温度の主要パラメータの仕様が向上するからです。

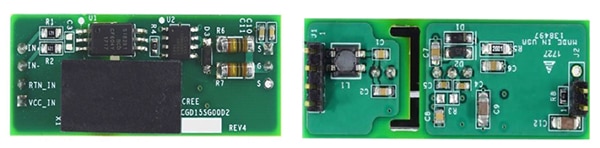

独自のゲートドライバ分岐回路を設計する必要があるお客様のために、Wolfspeedはこれら第3世代SiC FETのゲートドライバリファレンス設計としてCGD15SG00D2も用意しています(図7)。

図7:ゲートドライバリファレンス設計CGD15SG00D2の上面(左)と下面(右)。すべてのBOMを搭載した完全なボードです。また、SiC MOSFETダイが同じで、リードが3つと4つのTO-247パッケージにより、性能を比較評価できます。(画像提供:Wolfspeed)

図7:ゲートドライバリファレンス設計CGD15SG00D2の上面(左)と下面(右)。すべてのBOMを搭載した完全なボードです。また、SiC MOSFETダイが同じで、リードが3つと4つのTO-247パッケージにより、性能を比較評価できます。(画像提供:Wolfspeed)

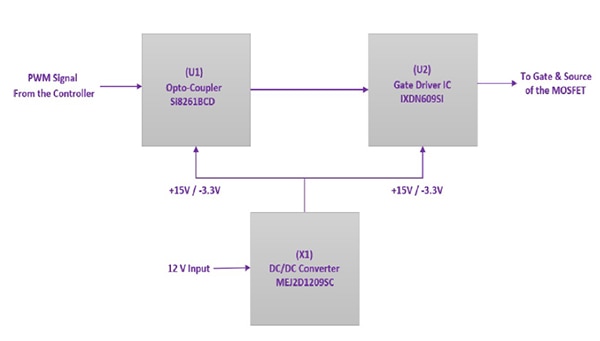

CGD15SG00D2のハイレベルのブロック図(図8)は、オプトカプラ(U1)、ゲートドライバ集積回路(U2)、絶縁電源(X1)など、このリファレンス設計の機能を示しています。オプトカプラ(5000VのAC絶縁)は、パルス幅変調(PWM)信号を受け取り、35/50kV/µs(最小/標準)のコモンモードイミュニティを提供します。そのほか、注目すべき特長は以下のとおりです。

- プリント基板のロジック側とパワー側の間に、必要な沿面仕様を拡張するための溝。また、ボードの1次回路と2次回路の間に9mmの沿面拡張スロット。

- 高周波数における大型MOSFETの動作に対応する2ワットの絶縁電源。

- 専用ダイオードを備えた別々のターンオン抵抗とターンオフ抵抗。ターンオン信号とターンオフ信号の両方をカスタマイズおよび最適化できます。

- EMIイミュニティを拡張するロジックパワー入力のコモンモードインダクタ。

図8:このゲートドライバリファレンス設計CGD15SG00D2のハイレベルのブロック図では、主要な機能ブロックであるオプトカプラU1、ゲートドライバIC U2、絶縁電源X1を示しています。(画像提供:Wolfspeed)

図8:このゲートドライバリファレンス設計CGD15SG00D2のハイレベルのブロック図では、主要な機能ブロックであるオプトカプラU1、ゲートドライバIC U2、絶縁電源X1を示しています。(画像提供:Wolfspeed)

まとめ

Wolfspeedの第3世代SiC MOSFETは、パワースイッチング用途において、従来のSi MOSFETと比べて、効率と熱性能に関する大きな利点を提供します。適切なドライバと組み合わせることで、新規用途と従来用途の両方において、信頼性の高い安定した性能を発揮します。

免責条項:このウェブサイト上で、さまざまな著者および/またはフォーラム参加者によって表明された意見、信念や視点は、DigiKeyの意見、信念および視点またはDigiKeyの公式な方針を必ずしも反映するものではありません。