マルチコアプロセッサを使用して低消費電力でメディアリッチなスマート製品を構築

DigiKeyの北米担当編集者の提供

2019-03-26

スマート製品は、従来のリアルタイム組み込み設計要件を満たすと共に、要求の厳しいアプリケーションレベルのソフトウェアを搭載する必要がますます高まっています。計算負荷の増大と共に、こうした製品はタッチスクリーン、高解像度3Dグラフィック、画像センサなどの高度なメディアサービスを介したユーザーインタラクションをサポートする必要があります。

要件が拡大しても、開発者は消費電力、コスト、システムのサイズを低減するというさらに大きな圧力に直面しており、従来の複数サブシステム設計に代わる、より効果的な設計を見いだすことを迫られています。

この記事では、設計要件の進化とそうした要件をプロセッサが現時点でいかに満たしているかについて説明します。その後、NXP Semiconductorsの新しいプロセッサの使い方を紹介します。これらは、リアルタイム要件とアプリケーションコンピューティング要件の両方に対処できる設計への増大する要求を満たすための、よりシンプルなソリューションを開発者に提供します。

コードへの投資を維持するプロセッサのスケーリング

特定アプリケーションの処理要件に合致する追加のコアを内蔵したマイクロプロセッサを使用することで設計のコンピューティングパワーをスケーリングすることは、開発者にとって一般的になっています。この方法を使うと、既存のコードベースとの互換性を保ち、そのデバイスファミリの経験を活かしながら、パフォーマンスを飛躍的に向上させることができます。

たとえば、NXP i.MX 6アプリケーションプロセッサシリーズの場合、設計者は、Arm® Cortex®-A9アプリケーションプロセッサコアを1つ備えたi.MX 6Soloマイクロプロセッサ、2つ備えたi.MX 6Dual、あるいは4つ備えたi.MX 6Quadを使用してパフォーマンスをスケーリングすると同時に、コードの互換性を維持できます。

スケーラブルなアプリケーション処理に対する同様の必要性が、従来は組み込みシステムと考えられた設計において急速に進展しつつあります。こうした設計の場合、製品製造者は家電製品、産業用制御装置、医療機器などにインテリジェンスを加えることを目指しています。半導体ベンダーは、アプリケーションプロセッサと組み込みプロセッサコアの両方を統合した異種マルチコア処理(HMP)デバイスでこれに応えました。たとえば、NXPのi.MX 8Mファミリでは、最大で4つのArm Cortex-A53アプリケーションプロセッサコアと1つのArm Cortex-M4組み込みプロセッサコアを組み合わせています。

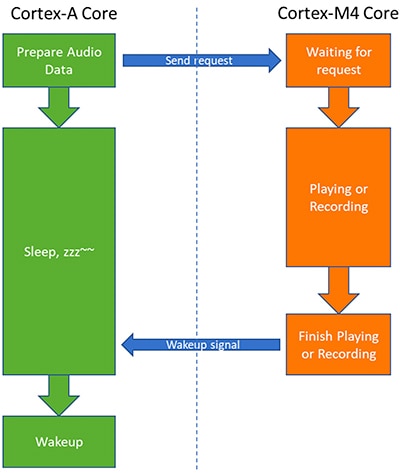

この1つのデバイスで、開発者はスマートオーディオ製品を構築することができます。それらの製品ではアプリケーションプロセッサを最大限に活用して、オーディオデータの強化やフィルタリングを行ったり、データを操作したりします。そしてオーディオシステムは組み込みプロセッサコアに依存して再生に必要なリアルタイム機能を実行します(図1)。組み込みプロセッサでリアルタイム処理が進行している間、アプリケーションプロセッサは全体の消費電力低減のため低消費電力モードにすることができます。リアルタイム処理が完了すると、組み込みプロセッサはアプリケーションプロセッサに復帰信号を送信します。

図1: 異種マルチコアプロセッサは、特にスマート製品の設計に効果的で、厳しいパワーバジェットを損なうことなく高性能計算とリアルタイム機能を提供します。(画像提供:NXP Semiconductors)

NXP i.MX 8Mファミリは、異種コアと共に、4Kビデオ処理ユニット(VPU)および高性能3Dグラフィックス処理ユニット(GPU)などの広範なマルチメディアリソースを統合しています。その結果、このファミリは、成長しつつあるビデオおよび3Dグラフィックス対応スマート製品クラス向けの効果的なソリューションを提供できます。

しかし、高性能なシステムを構築する開発者は、バッテリ駆動用と商用電源用のどちらのシステムでも低消費電力への要求の増大に直面しています。これに対処するため、NXP i.MX 8M Miniプロセッサファミリは高性能に伴う混合負荷処理と低消費電力という対立する両方の要件を満たす先進的な半導体プロセス技術によって製造されます。

高性能、低消費電力のコンピューティング

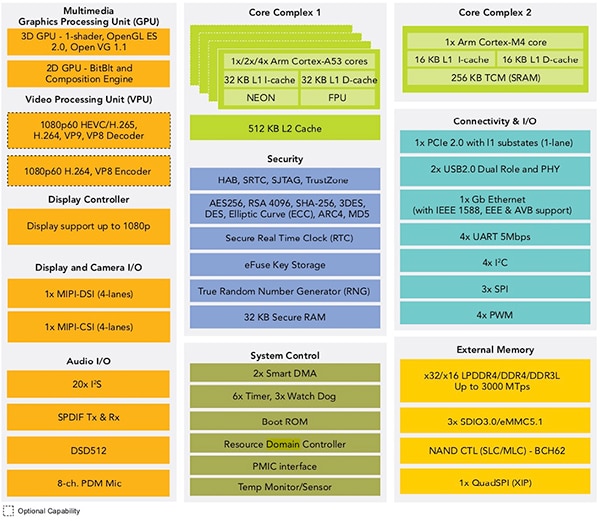

14ナノメートル(nm)FinFETプロセス技術で製造された最初のNXP HMPファミリ製品であるNXP i.MX 8M Miniプロセッサは、高性能、強力なセキュリティ、低消費電力という要件が混在する新たな産業用システムおよびモノのインターネットのシステム向けに設計されています。NXP i.MX 8Mファミリと同じく、NXP i.MX 8M Miniは、組み込み処理用の1つのArm Cortex-M4とアプリケーション処理用の最大4つのArm Cortex-A53コアを内蔵すると共に、包括的なセキュリティサブシステムと複数のコネクティビティおよびI/Oオプションを備えています(図2)。

図2: NXP i.MX 8M Miniプロセッサは、最大4つのArm Cortex-A53アプリケーションプロセッサコアとArm Cortex-M4組み込みコアに加えて、登場するスマート製品に必要なセキュリティ、マルチメディア、システム機能、I/Oインターフェースなどのすべてに対応する機能を備えています。(画像提供:NXP Semiconductors)

組み込み設計でのその役割を果たすため、i.MX 8M Miniは先行のNXP i.MX 8Mに比べ、一部のI/Oチャンネルの数が減らされ、マルチメディアサブシステムの高解像度機能が抑えられています。たとえば、商用のMIMX8MM6DVTLZAAおよび産業用のMIMX8MM6CVTKZAAAなどのi.MX 8M Miniファミリデバイスは、NXP i.MX 8Mが4つのシェーダGPUと4K VPUを内蔵しているのに対し、1つのシェーダGPUと1080p 60ヘルツ(Hz)VPUとなっています。i.MX 8M Miniファミリの商用のMIMX8MM5DVTLZAA、産業用のMIMX8MM5CVTKZAAなどの他の製品は完全にVPUを排除しています。先行のNXP i.MX 8Mと同様、MX 8M Miniを使用する開発者は、DDR3L(Double Data Rate 3 Low voltage)、DDR4、LPDDR4(Low Power DDR4)など複数メモリタイプのプロセッササポートを活用して、さらに性能とコストのバランスを取ることができます。

消費電力を低減

性能と消費電力をさらに調整するため、NXP i.MX 8M Miniでは、低消費電力動作モードへの切り換えを自動的またはプログラムにより行う機能を活用できます。アプリケーションコアは、一定の条件下で自動的にアイドルモードに切り換わることができ、大部分の内部ロジックに対してクロックゲーティングを行うと同時にL2データキャッシュへの電力供給を維持しつつ、GPU、VPU、アプリケーションコアをオフにすることができます。このモードで、Arm Cortex-M4コアは、センサデータ取得などのより多くの従来の組み込み処理タスク実行の動作を継続することもできます。

サスペンドモードは最も電力効率のよいモードであり、メモリインターフェースを管理するダブルデータレートコントローラ(DDRC)も無効にしてアイドル状態における消費電力低減を拡張します。最後に、セキュア不揮発記憶(SNVS)モードでは、SNVSロジックとリアルタイムクロックへの電力供給のみを維持します。

i.MX 8Mに使用されている14nm FinFETプロセス技術の消費電力低減特性は、サスペンドモードとSNVSモードで特に顕著になります。FinFETを使用したi.MX 8M Miniのサスペンドモードでの消費電力は約7.81ミリワット(mW)です。先行のMX 8Mの場合、機能的に類似したモード(ディープスリープモード)での消費電力は197mWです。同様の消費電力低減がSNVSモードにも当てはまり、i.MX 8M Miniの省電力は約0.11mW、先行のi.MX 8Mでは約17mWです。

i.MX 8M Miniのような複雑なデバイスでの全機能ブロックと微調整された動作モードの場合、エンジニアは多くの厳格な実装要件に直面します。このクラスの他のデバイスと同様、i.MX 8M Miniは電源の管理と効率を最適化するため複数の電源領域に依存します。これらのデバイスの起動および停止を行うには、電源投入および電源切断のための特定シーケンスに厳格に従う必要があります。

i.MX 8M Miniの電源投入は、SNVSバンクのGPIOプリドライバに通常は1.8ボルトの電圧印加を行うことから開始されます。2ミリ秒(ms)以内に(最長2.4ミリ秒)、SNVSコアロジックに(通常)0.8ボルトを印加する必要があります。このプロセスは、i.MX 8M Miniのピンに特定の信号または電力が印加される12のステップからなるシーケンスで続行され、各ステップは0.015ms~20ms以内の間隔で実行されます。

デバイスの電源切断は逆のシーケンスに従いますが、各段階間で一律に10msの遅延が必要です。どちらの場合も、こうしたガイドラインに従わないとデバイスのブートができず、電源投入時に過電流が発生したり、最悪の場合にはデバイスに不可逆的な損傷を与えたりすることがあります。

プロセッサ用プリント基板の物理設計にはそれ自体の厳格な要件があります。このプロセッサの486ボール14 x 14ミリメートル(mm)パッケージのレイアウト設計用に、NXPはIRドロップのガイドラインに従うため電源レール専用の十分なレイヤを備えた、最低8層のプリント基板スタックアップを採用することを推奨しています。同時に、レイアウトエンジニアは、1.5ギガヘルツ(GHz)および3,000MT/s(megatransfers per second)の速度で動作するサポート対象メモリデバイス用を含む、高速ラインでの最小限のクロストークを保証する必要があります。

開発期間の短縮

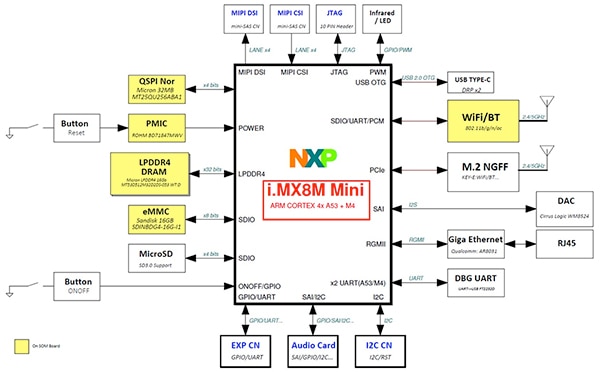

迅速にアプリケーション開発を開始するか、独自のハードウェア設計を高速開発できるように、NXPは、NXP i.MX 8M Mini EVK(評価キット)および関連リファレンス設計を提供しています(図3)。ベースボードおよびシステムオンモジュール(SOM)ボードとして提供されるこの評価キットは、外部LPDDR4メモリ、フラッシュ、さらにUSBなどの他のインターフェースを含む完全なシステムです。

図3: NXP i.MX 8M Mini EVKボードセットは、即座にi.MX 8M Miniプロセッサを評価し、異種マルチコアプロセッサアプリケーションを迅速に開発するための完全なシステムプラットフォームです。(画像提供:NXP Semiconductors)

このキットは、ギガビットEthernetと共にコネクティビティオプションとしてWi-Fi、Bluetoothを備えています。MINISASTOCSIカメラモジュール、MX8-DSI-OLED1有機発光ダイオード(OLED)タッチスクリーンなどのアドオンボードがあり、ビデオおよび表示アプリケーションの設計に利用できます。

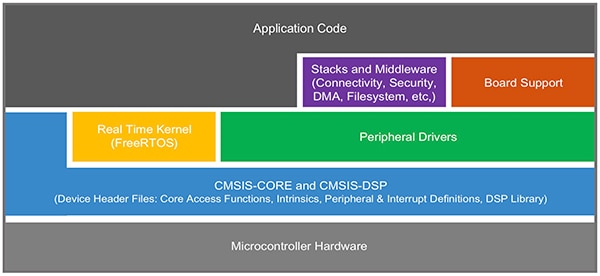

Embedded Linux®、Embedded Android®のオペレーティング環境向けのプリビルド済みイメージが用意されていて、開発者はこのキットを使って即座にi.MX 8M Miniプロセッサを評価しサンプルアプリケーションを実行できます。独自のソフトウェアアプリケーションを開発する開発者向けに、NXPは一般的な高性能組み込みアプリケーション(図4)を作成するためのソフトウェアコンポーネント一式を含む無償のMCUXpressoソフトウェア開発キット(SDK)を提供しています。

図4: MCUXpressoソフトウェア開発キット(SDK)のアーキテクチャは、ドライバ、ボードサポートパッケージ、大部分の組み込みアプリケーション開発に必要なオプションコンポーネントなどのソフトウェアレイヤ一式で構成されています。(画像提供:NXP Semiconductors)

NXPのオンラインMCUXpresso SDK Dashboardを使うと、GCC Arm EmbeddedツールチェーンまたはIAR Embedded Workbench for Arm用にSDK構成を設定できます。このダッシュボードでは、Arm Cortex Microcontroller Software Interface Standard(CMSIS)DSP library、Amazon FreeRTOSなど、オプションのミドルウェアコンポーネントを追加することもできます。構成されたSDK配布物には、Arm標準ライブラリ、ペリフェラルドライバ、FreeRTOS用ペリフェラルドライバラッパ、広範なソフトウェアサンプルの一式がすべて付属しています。SDK配布物のソフトウェアサンプルには、異種コンピューティングに欠かせない重要なメッセージ交換デザインパターンを示すアプリケーションのペアが含まれています。

どのようなマルチコアコンピューティング環境でも、個別のプロセッサにリクエストを渡し、データを共有するための効率の良い仕組みが必要です。NXPは、i.MX 8M Mini EVKのアプリケーション用にRPMsg(Remote Processor Messaging)プロトコルの軽量版であるRPMsg-Liteを使用しています。RPMsgプロトコルは、異種マルチコアシステム内の複数コア間通信のための標準インターフェースを提供するOpenAMP(Open Asymmetric Multi Processing)フレームワークプロジェクトの一部として作成されました。NXPのRPMsg-Liteは、より小さな組み込みシステムにおけるリソースの制約に対処するため、より小さなフットプリントを提供し、そうしたシステムと調和しない機能を削除しています。

このSDK配布物に含まれるサンプルアプリケーションであるrpmsg_lite_pingpong_rtosは、RPMsg-Liteを使って異なるプロセッサ間での単純なping-pongインタラクションを実装する、必要最小限の交換を示しています(リスト1)。もう1つの「リモート」プロセッサ用にRPMsgキュー(my_queue)とエンドポイント(my_ept)を生成した後、「ホスト」アプリケーションプロセッサがリモートコアに合図を送ります。リモートコアからハンドシェイク応答を受け取った後、ホストはブロッキングウェイトを使用したループを開始し、リモートコアからの「ping」メッセージを受け取った後、自身の「pong」レスポンスを送信します。

コピー

void app_task(void *param)

{

. . . my_rpmsg = rpmsg_lite_remote_init((void *)RPMSG_LITE_SHMEM_BASE, RPMSG_LITE_LINK_ID, RL_NO_FLAGS);

while (!rpmsg_lite_is_link_up(my_rpmsg))

;

PRINTF("Link is up!\r\n");

my_queue = rpmsg_queue_create(my_rpmsg);

my_ept = rpmsg_lite_create_ept(my_rpmsg, LOCAL_EPT_ADDR, rpmsg_queue_rx_cb, my_queue);

ns_handle = rpmsg_ns_bind(my_rpmsg, app_nameservice_isr_cb, NULL);

rpmsg_ns_announce(my_rpmsg, my_ept, RPMSG_LITE_NS_ANNOUNCE_STRING, RL_NS_CREATE);

PRINTF("Nameservice announce sent.\r\n");

/* Wait Hello handshake message from Remote Core.*/

rpmsg_queue_recv(my_rpmsg, my_queue, (unsigned long *)&remote_addr, helloMsg, sizeof(helloMsg), NULL, RL_BLOCK);

while (msg.DATA <= 100)

{

PRINTF("Waiting for ping...\r\n");

rpmsg_queue_recv(my_rpmsg, my_queue, (unsigned long *)&remote_addr, (char *)&msg, sizeof(THE_MESSAGE), NULL,

RL_BLOCK);

msg.DATA++;

PRINTF("Sending pong...\r\n");

rpmsg_lite_send(my_rpmsg, my_ept, remote_addr, (char *)&msg, sizeof(THE_MESSAGE), RL_BLOCK);

}

PRINTF("Ping pong done, deinitializing...\r\n");

rpmsg_lite_destroy_ept(my_rpmsg, my_ept);

my_ept = NULL;

rpmsg_queue_destroy(my_rpmsg, my_queue);

my_queue = NULL;

rpmsg_ns_unbind(my_rpmsg, ns_handle);

rpmsg_lite_deinit(my_rpmsg);

msg.DATA = 0;

. . .}

リスト1: MCUXpressoソフトウェア開発キットで提供されているサンプルコードに基づくこのスニペットは、異種マルチコアプロセッサ内にある異なるプロセッサ間のインタラクションを実行するための基本的なデザインパターンを示しています。(コード提供: NXP Semiconductors)

このシンプルなやりとりを基にして、複数のプロセッサ間にタスク実行を割り当てることを意図した完全な動作を簡単に構築できます。別のサンプルアプリケーションであるsai_low_power_audioは、本来、下位のデータリンク層であるRPMsg-Liteを上位のSRTM(Simplified Real Time Messaging)アプリケーションプロトコル用に使用します。このアプリケーションでは、Arm Cortex-A53プロセッサがこのSRTMプロトコルを使用して、Arm Cortex-M4プロセッサに共有メモリにあるオーディオファイルの再生を要求します。共有バッファを制御下に置いた後、M4はいくつかの処理を行い、SDMA(Smart Direct Memory Access)トランザクションを実行してデータを該当のコードに転送し、最後にオーディオ出力用のシリアルオーディオインターフェース(SAI)に送ります。この動作の間、A53コアは低消費電力モードにすることができます。ping-pongアプリケーションよりも設計は複雑ですが、このsai_low_power_audioは、異種マルチコアプロセッサをどのように使用すればスマート製品の消費電力を最小化しつつ性能を最大化できるかを示しています。

まとめ

スマート製品では従来のリアルタイム組み込み処理システムと重要なアプリケーション処理機能を組み合わせています。ただし、開発者はこれらの処理要件を満たしつつ、バッテリ駆動システムでも電源供給ラインによるシステムでも低消費電力製品への継続的な期待を満たす必要があります。

高度な半導体プロセスによって製造された、NXPのi.MX 8M Miniアプリケーションプロセッサは、必要とされる低消費電力と高性能な異種マルチコア処理の機能を兼ね備えています。NXP i.MX 8M Miniデバイスを使用すれば、ますます高度化するスマート製品に必要な組み込みシステム設計において新たに登場する高性能計算の要件により効果的に対応できます。

免責条項:このウェブサイト上で、さまざまな著者および/またはフォーラム参加者によって表明された意見、信念や視点は、DigiKeyの意見、信念および視点またはDigiKeyの公式な方針を必ずしも反映するものではありません。