AI/ML画像処理にEfinix FPGAを使用する理由と方法 - 第1部:導入

DigiKeyのヨーロッパ担当編集者の提供

2023-04-20

編集者注:FPGAアーキテクチャの新しいアプローチは、機械学習(ML)や人工知能(AI)のニーズに対応するため、よりきめ細かい制御と高い柔軟性をもたらします。2部で構成される本シリーズの第1部では、Efinixが提供するそのようなアーキテクチャの1つと、開発ボードを使用した開発の始め方を紹介します。第2部では、カメラなどの外部デバイスや周辺機器と開発ボードとのインターフェース接続について説明します。

FPGAは、産業制御、安全、ロボティクス、航空宇宙、自動車など、多くのアプリケーションで重要な役割を担っています。プログラマブル論理コアの柔軟な性質と幅広いインターフェース接続機能によって拡大しているFPGAのユースケースの1つに、ML推論を展開する際の画像処理があります。FPGAは、複数の高速カメラインターフェースを持つソリューションの実装に最適です。また、FPGAでは論理内に専用の処理パイプラインを実装できるため、CPUやGPUベースのソリューションで発生するボトルネックを解消することも可能です。

しかし、多くの開発者が取り組むアプリケーションでは、組み合わせ論理ブロック(CLB)を備えた従来のFPGAアーキテクチャが提供できる範囲を超えて、より多くのML/AI機能、より細かな制御やルーティング、ロジックが必要となります。FPGAアーキテクチャの新しいアプローチでは、これらの問題に対処しています。たとえば、EfinixのQuantumアーキテクチャでは、XLR(eXchangeable Logic and Routing)ブロックを採用しています。

この記事では、AI/ML機能に焦点を当て、また実際の実装例を紹介してEfinixのFPGAアーキテクチャの主な特長や属性を説明します。そして、開発者が次のAI/ML画像処理設計に素早く着手するために使用できる開発ボードと関連ツールについて説明します。

EfinixのFPGAデバイス

Efinixは現在、2種類のデバイスを提供しています。当初は、4000(4K)から120Kの論理素子(LE)という論理密度を提供し、SMIC 40LLプロセスで製造されるTrionファミリを導入しました。最新のデバイスラインであるTitaniumファミリは、35Kから100万(1M)の論理素子という論理密度を提供し、非常に人気のあるTSMC 16nmノードで製造されます。

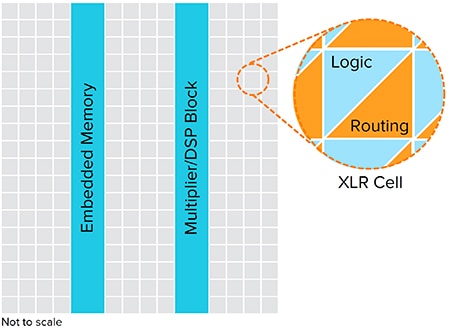

両製品とも、FPGAの世界で固有のQuantumアーキテクチャをベースにしています。標準的なFPGAのアーキテクチャは、最も単純なレベルでは、ルックアップテーブル(LUT)とフリップフロップを含むCLBをベースにしています。CLBは論理式を実装し、ルーティングで相互接続されます。EfinixのQuantumアーキテクチャは、XLRブロックによって論理ブロックとルーティングブロックの区別をなくしました。

XLRブロックに固有の点は、LUTを備えた論理セル、レジスタと加算器、またはルーティングマトリクスとして機能するように構成できることです。このアプローチは、ルーティングの柔軟性をもたらす、よりきめ細かいアーキテクチャを提供するため、論理重視の実装やルーティング重視の実装でも、望ましい性能を実現することができます。

図1:XLRブロック固有の特長は、LUTを備えた論理セル、レジスタと加算器、ルーティングマトリクスのいずれかとして機能するように構成できることです。(画像提供:Efinix)

図1:XLRブロック固有の特長は、LUTを備えた論理セル、レジスタと加算器、ルーティングマトリクスのいずれかとして機能するように構成できることです。(画像提供:Efinix)

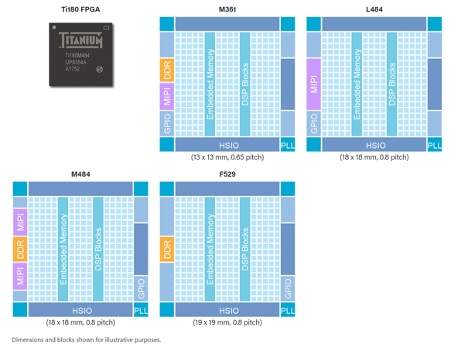

最新のファミリであるTitaniumデバイスは、開発者に対して最も高度な機能を提供します(図2)。XLRコアとともに、選択したデバイスに応じて16Gbpsまたは25.8Gbpsで動作するマルチギガビットのシリアルリンクを提供します。これらのマルチギガビットリンクは、チップ内外の高速データ転送を可能にするために極めて重要です。

図2:Titanium FPGA Ti180には、バス幅、I/O、メモリの要件に応じて、さまざまなオプションが用意されています。(画像提供:Efinix)

図2:Titanium FPGA Ti180には、バス幅、I/O、メモリの要件に応じて、さまざまなオプションが用意されています。(画像提供:Efinix)

Titaniumデバイスは、汎用I/O(GPIO)としてグループ化し、3.3ボルト、2.5ボルト、1.8ボルトの低電圧CMOS(LVCMOS)などのシングルエンドI/O規格をサポートできる幅広い入力/出力(I/O)インターフェース機能も提供します。

高速および差動インターフェースに対しては、1.2ボルト、1.5ボルトのLVCMOS、SSTLおよびHSTLなどのシングルエンドI/O規格をサポートする高速I/O(HSIO)を備えています。HSIOがサポートする差動I/O規格には、低電圧差動信号(LVDS)、差動SSTL、HSTLがあります。

また、最新のFPGAには密結合の高帯域幅メモリも必要で、画像処理アプリケーションの画像フレームや信号処理のサンプルデータを保存し、そしてもちろんFPGA内に実装されたプロセッサのオペレーティングシステムやソフトウェアを実行するために使用されます。Titaniumシリーズのデバイスは、ダイナミックデータレート4(DDR4)および低消費電力DDR4(x)(LPDDR4(x))とのインターフェース接続機能を提供します。選択したTitaniumデバイスに応じて、バス幅のサポートはx32(J)またはx16(M)であり、一部のデバイスはLPDDR4のサポートがありません(L)。

Titanium FPGAはSRAMベースで、構成メモリを必要とし、デバイスの構成はマスター/スレーブのシリアルペリフェラルインターコネクト(SPI)またはJTAGで実行されます。この構成方式の安全性を確保するため、Titanium FPGAではビットストリームの暗号化にAES GCMを使用し、さらにビットストリーム認証にAES GCMとRSA-4096を使用しています。FPGAは、悪意のある人物がアクセスし、その動作を操作する可能性のあるエッジに配置されるため、このような強力なセキュリティが必要となるのです。

開発ボードの紹介

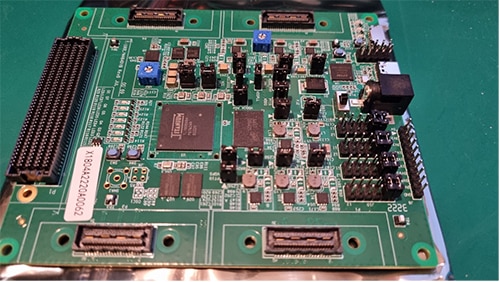

開発ボードは、FPGAの評価プロセスにおいて重要な要素であり、デバイスの機能を探索し、アプリケーションを試作するために使用することで、全体的なリスクを低減するのに役立ちます。Titanium FPGAを評価し、アプリケーションの試作を開始するために利用できる最初の開発ボードがTi180 M484です(図3)。このボードには、FPGAメザニンカード(FMC)コネクタと4つのSamtec QSEコネクタが搭載されています。

図3:Ti180 M484開発キットは、Titanium FPGAとともに、FMCコネクタと4つのSamtec QSEコネクタを備えています。(画像提供:アダム・テイラー氏)

図3:Ti180 M484開発キットは、Titanium FPGAとともに、FMCコネクタと4つのSamtec QSEコネクタを備えています。(画像提供:アダム・テイラー氏)

この開発ボードに搭載されたTi180 FPGAは、172KのXLRセル、32のグローバルクロック、640のデジタル信号処理(DSP)素子、13メガビット(Mbits)の組み込みRAMを備えています。DSP素子は、固定小数点18x19乗算と48ビット乗算を実装する機能を提供します。このDSPは、デュアルまたはクアッド構成で動作するシングルインストラクション・マルチプルデータ(SIMD)演算に最適化することも可能です。また、DSP素子は、浮動小数点演算を行うように構成できます。

多くの開発ボードと同様に、Ti180開発ボードはシンプルなLEDとボタンを備えています。しかし、その真価を発揮するのは、インターフェース接続の能力です。Ti180開発ボードでは、さまざまな周辺機器を接続できるように、ピン数の少ないFMCコネクタが用意されています。広く普及している規格であるため、高速なA/Dコンバータ(ADC)、D/Aコンバータ(DAC)、ネットワーク、メモリ/ストレージソリューションなどのインターフェース接続を実現するFMCカードが数多く存在します。

この開発ボードは、FMC接続に加え、Samtec QSEコネクタを4つ備えているため、拡張カードを追加することが可能です。これらのQSEコネクタは、MIPI入出力を提供するために使用され、各QSEコネクタは、MIPI入力または出力のいずれかを提供します。

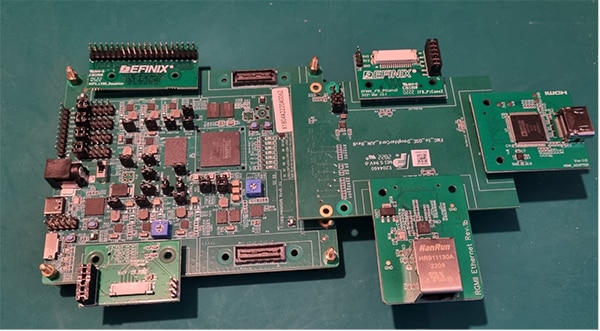

図4:Ti180 M484開発キットは、QSEコネクタとFMCコネクタをベースにした多彩な拡張オプションを備えていることがわかります。(画像提供:アダム・テイラー氏)

図4:Ti180 M484開発キットは、QSEコネクタとFMCコネクタをベースにした多彩な拡張オプションを備えていることがわかります。(画像提供:アダム・テイラー氏)

また、Ti180ボードは256MbitsのLPDDR4を搭載し、画像や信号処理のアプリケーションで必要とされる高性能なメモリをサポートします。さらに、この開発ボードには25、33.33、50、74.25MHzのクロックオプションが用意されており、デバイスのフェーズロックループ(PLL)と併用することで異なる内部周波数を生成できます。

開発中にボード上でライブのリプログラミングやデバッグを行えることが重要で、JTAG接続が必要ですが、これはUSB-Cインターフェースで提供されます。また、256MbitのNORフラッシュデバイスを2個搭載した不揮発性メモリも用意されており、構成ソリューションのデモに使用することができます。

ボードの電源は、同梱の12Vユニバーサル電源アダプタから供給されます。また、FMC-to-QSEブレークアウトと、HDMI、Ethernet、MIPI、LVDS用のQSEベースの拡張カードも付属しています。Ti180の画像処理能力を実証するために、デュアルRPIドーターカードと2枚のIMX477カメラカードも用意されています。

ソフトウェア環境

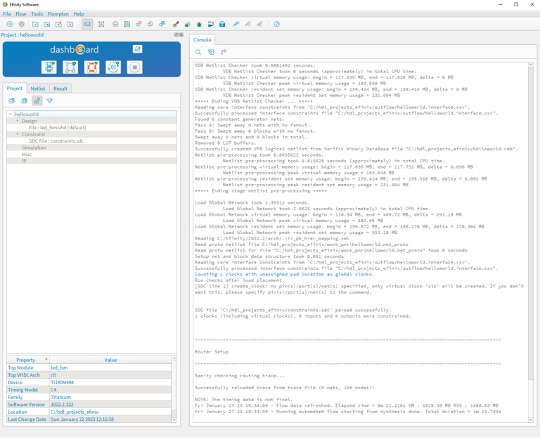

Ti180開発ボードをターゲットにした設計の実装では、Efinixのソフトウェア「Efinity」を使用します。これは、論理合成、配置、配線によるビットストリームの生成を可能にするソフトウェアです。また、知的財産(IP)ブロック、タイミング解析、オンチップデバッギングなどの機能も提供します。

なお、Efinityソフトウェアにアクセスするためには、開発ボードが必要です。しかし、このツールには他のベンダーのように、追加のライセンスが必要な別のバージョンは存在しません。

Efinityでは、選択したデバイスをターゲットにして新しいプロジェクトが作成されます。その後、RTLファイルをプロジェクトに追加し、タイミングやI/O設計のための制約を作成することができます。また、HSIO、GPIO、特殊I/Oを活用したI/O設計の実装もEfinityで実現可能です。

図5:Efinityでは、選択したデバイスをターゲットにした新規プロジェクトが作成されます。(画像提供:アダム・テイラー氏)

図5:Efinityでは、選択したデバイスをターゲットにした新規プロジェクトが作成されます。(画像提供:アダム・テイラー氏)

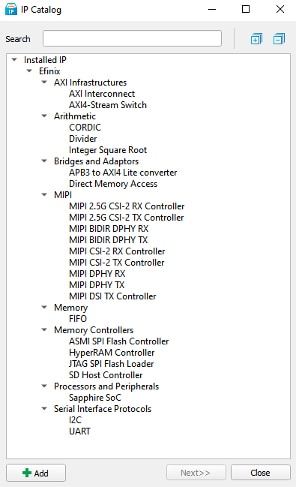

FPGA設計で重要なのはIPの活用であり、特に、AXIインターコネクト、メモリコントローラ、ソフトコアプロセッサなどの複雑なIPを活用することです。Efinityは、設計プロセスを加速させるために使用できるさまざまなIPブロックを提供しています。

図6:Efinityは、開発者が設計プロセスを加速させるために使用できるIPカタログを提供しています。(画像提供:アダム・テイラー氏)

図6:Efinityは、開発者が設計プロセスを加速させるために使用できるIPカタログを提供しています。(画像提供:アダム・テイラー氏)

FPGAは並列処理構造の実装に優れていますが、多くのFPGA設計にはソフトコアプロセッサが含まれています。これらは、ネットワーク通信などの逐次処理を実装する機能を提供します。Efinixデバイスへのソフトコアプロセッサの導入を可能にするため、EfinityはSapphire SoC(システムオンチップ)構成ツールを提供しています。Sapphireを使用すると、複数のプロセッサにまたがるキャッシュとキャッシュコヒーレンシの両方と共に、組み込みLinuxオペレーティングシステムを実行する機能を持つマルチプロセッサシステムを定義することができます。Sapphireの中では、1つから4つまでのソフトコアプロセッサを選択できます。

実装されているソフトコアプロセッサは、RISC-V命令セットアーキテクチャを採用したソフトCPU「VexRiscV」です。VexRiscVプロセッサは32ビット実装で、パイプラインのための拡張機能を持ち、構成可能な機能セットを提供するため、Efinixデバイスへの実装に最適です。オプションで、乗算器、アトミック命令、浮動小数点拡張命令、圧縮命令などが構成可能です。SoCシステムの構成に応じて、性能は0.86~1.05DMIPS/MHzの範囲になります。

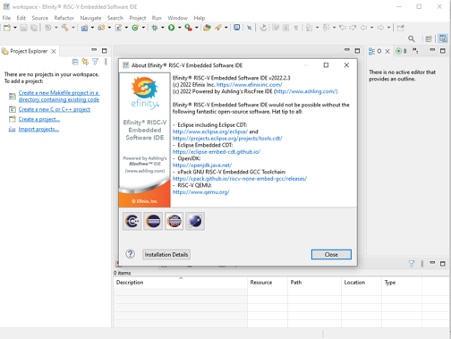

ハードウェア環境を設計し、Efinixデバイスに実装した後は、Ashling RiscFree IDEを使用してアプリケーションソフトウェアを開発することができます。Ashling RiscFreeは、EclipseベースのIDEで、アプリケーションソフトウェアの作成とコンパイルを可能にし、ターゲットのデバッグにより、デプロイ前のアプリケーションの微調整も可能になります。

図7:Ashling RiscFreeはEclipseベースのIDEで、ターゲットのデバッグとともに、アプリケーションソフトウェアの作成とコンパイルを可能にします。(画像提供:アダム・テイラー氏)

図7:Ashling RiscFreeはEclipseベースのIDEで、ターゲットのデバッグとともに、アプリケーションソフトウェアの作成とコンパイルを可能にします。(画像提供:アダム・テイラー氏)

組み込みLinuxソリューションを開発する場合、First Stage Boot Loader、OpenSBI、U-Boot、Buildrootを使用したLinuxなど、必要なすべてのブートアーティファクトが提供されます。また、リアルタイム性が求められる場合は、FreeRTOSを使用することも可能です。

AI実装

RISC-Vソフトコア演算をベースにしたのが、EfinixのAI実装です。これにより、RISC-Vプロセッサのカスタム命令機能を活用し、TensorFlow Liteソリューションの加速を実現します。また、RISC-Vプロセッサの使用により、AI推論の前処理や後処理の一部として使用できるカスタム命令を作成することが可能で、より応答性が高く決定論的なソリューションを実現できます。

AIの実装を始めるには、まず、そのエンドテクノロジーに最適化されたAI/MLモデルのライブラリであるEfinix Model Zooを探索する必要があります。Efinixデバイスで作業する開発者は、Model Zooにアクセスし、Jupyter NotebooksまたはGoogle Colabを使用してネットワークをトレーニングすることができます。ネットワークのトレーニングが完了したら、TensorFlow Liteのコンバータを使用して、浮動小数点モデルから量子化モデルに変換できます。

TensorFlow Lite形式になったら、EfinixのtinyMLアクセラレータを使用して、RISC-Vソリューション上でデプロイ可能なソリューションを作成することができます。開発者はtinyMLジェネレータにより、アクセラレータの実装をカスタマイズし、プロジェクトファイルを生成できます。この方法でデプロイした場合、選択したアーキテクチャとカスタマイズに応じて、4倍から200倍の加速が可能です。

まとめ

Efinixのデバイスは、固有のXLRアーキテクチャによって柔軟性を提供します。このツールチェーンは、RTL設計だけでなく、ソフトコアRISC-Vプロセッサを配備した複雑なSoCソリューションの実装にも対応できる能力を備えています。ソフトコアSoCの上に構築されるのは、ML推論のデプロイを可能にするAI/MLソリューションです。

免責条項:このウェブサイト上で、さまざまな著者および/またはフォーラム参加者によって表明された意見、信念や視点は、DigiKeyの意見、信念および視点またはDigiKeyの公式な方針を必ずしも反映するものではありません。