高アナログ電圧送電の課題をブートストラップ方式で解決する方法

DigiKeyの北米担当編集者の提供

2019-10-01

自動テスト装置や精密制御システムで必要になることが多い数百ボルトのアナログ電圧を生み出すことは、類を見ない難題です。従来のオペアンプは高出力の電圧振幅を扱うことはできず、一方で代替的なディスクリートアンプでは高度な調整が必要になり、より多くのプリント基板面積も占有します。

しかし、ここではもう1つのオプションをご紹介します。それは、高電圧レールツーレール出力オペアンプと、高降伏電圧に耐えられるFETペアの組み合わせのブートストラップを実行することです。

この記事では、高アナログ電圧にともなう問題とその一般的な解決策について説明します。さらに、Analog Devicesの高電圧高精度アンプとMicrochip TechnologyおよびInfineon Technologiesの高電圧MOSFETを使用した、ブートストラップのアプローチを使用する方法を紹介します。

これらのデバイスを使用して高精度で高性能なソリューションを作成することにより、アンプの公称信号範囲の2倍の範囲を実現し、基板の占有面積を最小限にしながらより高度な性能を維持できます。

高アナログ電圧の設計オプション

アプリケーションによっては、モノリシックオペアンプが生成できる標準的な高電圧よりも高い出力電圧振幅が必要になります。ディスクリートトランジスタを使用したアンプ設計は、幅広い電圧振幅を達成する1つの方法です。この設計アプローチには、特定用途向けにアンプをカスタマイズできる柔軟性があります。ただし、ディスクリートトランジスタの設計に使用する部品点数はより多くなり、設計にかかる時間と労力が増します。また、ディスクリート設計では、デバイスのマッチングと温度勾配のために精度を得ることが非常に難しくなります。

ディスクリート高電圧アンプに代わるのは、高電圧オペアンプモジュールです。このモジュールでは、設計作業が大幅に容易になります。多くの場合、高電圧モジュールは高電圧と高電力の動作の両方を可能にするハイブリッドモジュールです。これらのモジュールをディスクリートの設計と比較した場合の利点は、モジュールの性能が出荷時に仕様として指定されていることにあります。この仕様により設計段階で行う特性評価作業は減る反面、ハイブリッドモジュールは高価です。高電圧モノリシックオペアンプは多くの場合に、設計で要求される性能の大部分を満たすことができます。

しかしその要求を満たさない場合には、モノリシックオペアンプ電源のブートストラップを行うと、モノリシックアンプの電源がその仕様を超えて拡張することにより、使用可能なオペアンプのオプション数が数種のソリューションから数百にまで広がります。ブートストラップ方式にはより多くの労力が必要な一方、そのソリューションは高電圧モジュールに比べて大幅に低コストです。その主な理由は、出荷時に十分な性能仕様が指定されたさまざまなモノリシックオペアンプの存在があるためです。なお、ブートストラップはアンプのDC仕様、たとえば電圧オフセット、入力電圧振幅、出力電圧振幅などに影響を与えません。

電源ブートストラップ技術

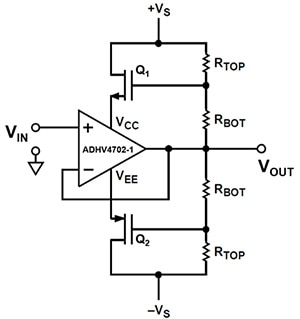

ブートストラップの設定により、デバイスの電源電圧を出力電圧との関係で制御します。ブートストラップ回路には、ディスクリートトランジスタ1ペアと抵抗バイアスネットワークがあります(図1)。

図1:高電圧フォロワブートストラップの簡略回路図。固定+VSおよび-VSシステム電源電圧をともないます。VCCおよびVEEのデバイス電源電圧は、出力電圧VOUTに比例して変化します。(画像提供:ボニー・ベイカー氏、Analog Devicesの資料提供)」

図1:高電圧フォロワブートストラップの簡略回路図。固定+VSおよび-VSシステム電源電圧をともないます。VCCおよびVEEのデバイス電源電圧は、出力電圧VOUTに比例して変化します。(画像提供:ボニー・ベイカー氏、Analog Devicesの資料提供)」

多くの高電圧アンプでは、ブートストラップ電源が必要なくなります。たとえば、図に示されるAnalog Devicesの10MHz ADHV4702-1BCPZは±110Vの電源で、大半の高電圧用途に十分です。ただし、システムがさらに高い電圧を必要とする場合、ブートストラップの手法でこの回路の動作範囲が容易に2倍になります。

ブートストラップを実行するために、Infineon TechnologiesのIRFP4868PBF NチャンネルMOSFETがQ1として使用されます。このデバイスの降伏電圧は300V、ID maxは70Aです。Q2は、Microchip TechnologyのTP2435N8-G PチャンネルMOSFETで、このデバイスの降伏電圧は350Vです。

図1では、ADHV4702-1高精度アンプの動作電源電圧範囲は±12~±110Vです。±110Vの電源電圧では、標準的な出力電圧範囲は±108.5Vです。±VSが±300Vに等しい場合、このブートストラップ回路は、出力振幅±120V以上を達成できるアンプの基礎となります。

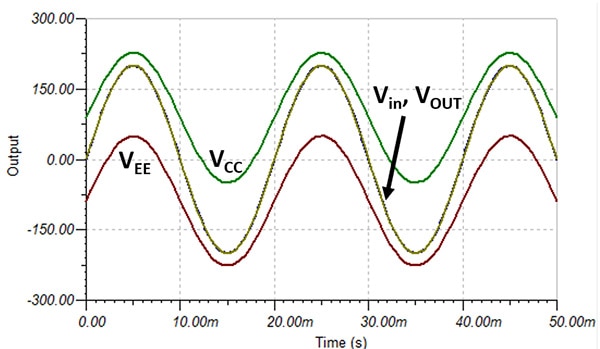

このブートストラップコンセプトはフライングレールとも呼ばれ、アンプの電源電圧を連続的に調整し、それがアンプの出力電圧VOUTを中心に対称になるようにします。これに応じて、出力は電源範囲内に留まります。フォロワブートストラップ回路では、抵抗分圧器(RBOTおよびRTOP)がVCCおよびVEEの差を±90Vで一定に保つとともに、アンプの出力範囲は±200Vになります。Spiceシミュレーションは、このフローティング電源の現象を示しています(図2)。

図2:Spiceシミュレーションはフローティング電源現象を示しており、アンプのデルタ電源(VCCおよびVEEの差)は約±90Vに留まるとともに、アンプの出力範囲は±200Vになります。(画像提供:ボニー・ベイカー氏)

図2:Spiceシミュレーションはフローティング電源現象を示しており、アンプのデルタ電源(VCCおよびVEEの差)は約±90Vに留まるとともに、アンプの出力範囲は±200Vになります。(画像提供:ボニー・ベイカー氏)

図2では、VOUTはVIN、RTOPは45キロオーム(kΩ)にそれぞれ等しく、RBOTは20kΩになります。RTOPは外部電源に最も近い抵抗(+VSおよび-VS)、RBOTはオペアンプの出力(VOUT)に最も近い抵抗です。なお図2では、VCCおよびVEEの電圧が+VS(300V)と-VS(-300V)に近づくことに注意してください。出力信号(VOUT)によってVCCおよびVEEのいずれかが強制的に+VSまたは-VS以上になると、回路の歪みが発生します。

ブートストラップは、あらゆるオペアンプに高い信号機能をもたらします。ただし、アンプのスルーレートは、この高電圧構成の動的性能に影響します。図1では、オペアンプのスルーレートにより、ダイナミック信号に対するVCCおよびVEEの応答機能が制限されています。ブートストラップアンプは、電源の移行が遅い低周波数およびDCアプリケーションに最適です。

ブートストラップ設計の実装

オペアンプ電源のブートストラップ設計では、3段階のプロセスを経ます。

- アンプとMOSFETの消費電力のトレードオフを評価する。

- アンプの最大出力振幅を決定し、アンプの電源電圧を割り当てる。

- 抵抗器の電力要件を考慮する。

図1では、消費電力がオペアンプとMOSFETのドレイン-ソースとの間で分かれます。アンプとFETには、指定された動作範囲内の電源電圧があります。アンプに低電圧で電力を供給しようとしても、これはMOSFETにストレスを与える場合があります。総消費電力は、アンプとMOSFETの間で割り当てられます。

最大オペアンプ出力振幅範囲(±VOUT-MAX)とオペアンプ電源(VEE、VCC)の関係に応じて、式1に従い、抵抗分圧器ネットワークが決まります。

![]() 式1a

式1a

オペアンプの公称電源電圧が±100Vに等しく、最大出力振幅範囲が±150Vに等しい場合、分周比は以下と等しくなります。

![]() 式1b

式1b

この計算からは、このアプリケーションの抵抗値を決定する便利な方法が分かります。ただし抵抗器を選択するときは、高電圧が関わっていること、場合によっては抵抗器がかなりの電力を消費する必要があることを考慮することが重要になります。それぞれの定格の範囲内で熱放散を制限するように、抵抗器の値を選びます。

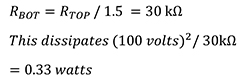

たとえば、RTOPは150V、RBOTは100Vに達します。½ワット定格の抵抗器を使用する場合、式2を使用して消費電力(V2/R)制限を計算します。

![]() 式2a

式2a

![]() 式2b

式2b

消費電力制限要因として45kΩ抵抗器を使用すると、RBOT値は静止消費電力制限をともなう2.5:1分周を生成し、次のように計算されます。

FETの選択

MOSFETを選ぶ主な基準は降伏電圧です。この電圧は、最悪のバイアス状態に耐える必要があります。降伏電圧は出力が飽和したときに生じますが、この飽和は、一方のMOSFETが最大VDSで、もう一方のMOSFETが最小VDSのときに発生します。たとえば、最大の絶対VDSは約300Vで、これはVOUT-MAX(500V)からアンプの合計電源電圧(VCC – VEE = 200V)を差し引いたものです。このため、MOSFETの耐電圧は300V以上でなければなりません。さらに、消費電力の計算はVDSと動作電流の両方の最悪ケースであることが必要です。設計者は、MOSFETがこの電力レベルで動作する仕様であることを確認する必要があります。

MOSFETのゲート静電容量は、バイアス抵抗とともにローパスフィルタを生成し、より高い降伏MOSFETはより高いゲート静電容量を持つ傾向があります。この回路では、バイアス抵抗が数十kΩから数百kΩになる傾向にあります。このような高い値では、回路の低速化にそれほど多くのゲート静電容量は要りません。

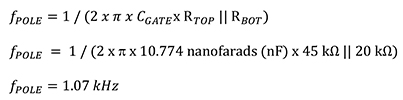

データシートにあるMOSFETゲート静電容量値(CGATE)およびRTOPとRBOTの並列の組み合わせにより、式3に従い、ローパスフィルタの極周波数が決まります。

式3

式3

注意事項

バイアスネットワークの周波数応答は、入出力の両信号よりも常に10倍速くなければなりません。バイアスネットワークにより回路が低速になると、アンプの出力供給が引き延ばされる原因になります。また、入力にはアンプの電源レールから外れたモーメンタリエクスカーションによる損傷のリスクがある一方、出力にはモーメンタリ飽和またはスルー制限による歪みのリスクがあります。これらの条件は、負帰還の損失、予測不能な過渡挙動、および位相反転によるラッチアップを引き起こす可能性があります。

性能

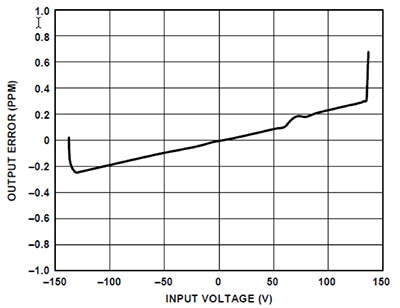

電源ブートストラップ回路にあるアンプは、より高い非反転ゲインに合わせて構成できます。このブートストラップオペアンプ構成は、他のオペアンプゲイン段の構成と同様に動作します。非反転構成を使用しなければなりません。DC直線性測定では、主にアンプの特性によって結果が決まります(図3)。アンプは±140Vの電源範囲でゲインが20になるように構成されています。

図3:グラフはゲイン誤差と入力電圧の関係で電源電圧範囲±140Vにおいてゲインが20になることを示しています。(画像提供:Analog Devices)

図3:グラフはゲイン誤差と入力電圧の関係で電源電圧範囲±140Vにおいてゲインが20になることを示しています。(画像提供:Analog Devices)

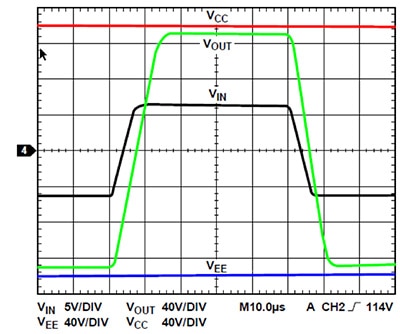

オペアンプの出力には有限スルーレートがあり、その電源はその出力に依存します。オペアンプの入力では、階段関数がオペアンプの電源範囲を超える場合があります(図4)。

図4:ゲイン20、電源範囲±140Vのスルーレート。オペアンプの入力では、階段関数がオペアンプの電源範囲を超える場合がありラッチ状態の原因になります。これは入力ノードにローパスフィルタを配置して回避できます。(画像提供:Analog Devices)

図4:ゲイン20、電源範囲±140Vのスルーレート。オペアンプの入力では、階段関数がオペアンプの電源範囲を超える場合がありラッチ状態の原因になります。これは入力ノードにローパスフィルタを配置して回避できます。(画像提供:Analog Devices)

図4では、ADHV4702-1の仕様のスルーレートは74V/ms(V/ミリ秒)です。ラッチ状態を回避するには、信号入力ノード(VIN)にローパスフィルタを使用する必要があります。このスルー制限回路は、式4による計算のように、過渡をオペアンプのスルーレート以下に低減します。

![]() 式4

式4

式では、VSTEPは信号源の最大ステップサイズで、SRはオペアンプのスルーレートです。

まとめ

高いアナログ電圧を低コストかつ最小限の基板面積で駆動する優れた方法として、高電圧レールツーレール出力オペアンプと高降伏電圧に耐えるトランジスタペアとの組み合わせをブートストラップする方法があります。Analog DevicesのADHV4702-1高電圧高精度アンプとInfineonおよびMicrochipの高電圧MOSFETを使用して高精度、高性能のソリューションを作成することにより、アンプの公称信号範囲の2倍の範囲を獲得し、非常に優れたパフォーマンスを継続的に得ることができます。

免責条項:このウェブサイト上で、さまざまな著者および/またはフォーラム参加者によって表明された意見、信念や視点は、DigiKeyの意見、信念および視点またはDigiKeyの公式な方針を必ずしも反映するものではありません。