統合型eGaNパワー段を使用した高エネルギー密度電源の作成

DigiKeyの北米担当編集者の提供

2019-04-16

高エネルギー密度のSMPS(スイッチモード電源)は、バッテリ充電を加速し、ソーラーマイクロインバータのサイズを小型化し、サーバファームの電力要件の需要を満たすことができ、いずれの場合も過度の熱を発生しません。しかし現在エンジニアは、従来のSMPSの主要なスイッチング素子を構成しているシリコンMOSFETとIGBTの性能限界に直面しています。そこで、eGaN(エンハンスメントモード窒化ガリウム)で構成されたトランジスタ(ワイドバンドギャップ半導体)を代わりに使用することで、シリコンデバイスのスイッチング速度と効率性の限界を打開できます。

以前は、eGaNトランジスタはそのコストと入手可能性により、最も特殊な電源アプリケーション以外での使用が妨げられていました。しかし商品化が広く浸透したことでその課題も解決されています。今ではeGaNトランジスタは幅広いアプリケーション用の選択肢の1つになっています。

この記事では、従来のシリコン(Si)MOSFETまたはIGBTに基づく電源と比較しながら、eGaNスイッチングコンポーネントに基づく高周波電源の利点について説明します。さらに、EPC、Texas Instruments、Navitas Semiconductorが提供するeGaNパワー段を使用した、バッテリ充電やサーバファームなどのアプリケーションに適したSMPSの設計方法に関するガイドラインについて述べます。

高周波の利点

従来のSMPSは通常、数十から数百キロヘルツ(kHz)の範囲のスイッチング周波数を使用します。電源の電圧出力は、基本周波数のパルス幅変調(PWM)のデューティサイクルにより決まります。

スイッチング周波数が高いことによる主な利点は、インダクタ、トランス、抵抗などの周辺部品のサイズが小さくなることです。これにより設計者は、縮小した設計で同じ出力電力を実現し、エネルギー密度を高めることができます。さらに、SMPS出力での電流と電圧のリップルが低減され、電磁妨害(EMI)のリスクやフィルタ回路のコストとサイズも節約、縮小できます。

一方で、従来のシリコンパワーMOSFETとIGBTのスイッチングは比較的低速で、デバイスのスイッチをオン/オフするたびに電力を著しく消費します。この損失は周波数が高くなるほど増大し、効率性の低下やチップ温度の上昇につながります。低速なスイッチングと高いスイッチング損失が重なることで、現在のSMPSの実用的なスイッチング周波数に上限が生じています。

設計者は、ワイドバンドギャップ半導体を活用することでこの上限を乗り越えられます。言うまでもなく、現在このアプリケーションで最も実績があり、利用しやすい技術はGaNです。そしてGaNをさらに向上させたのがeGaNです。

シリコンとGaNの比較

GaNには、シリコンよりも優れた利点があり、その一部はGaNの高い電子移動度と関係しています。電子移動度が高まると、半導体の降伏電圧が高まり(600V超)、より優れた「電流密度」(A/cm2)が得られます。 GaNのもう1つの利点は、この材料で作成されたトランジスタでは逆回復電荷が生じないことです。これは高スイッチ電流オーバーシュート(リンギング)の原因になる現象です。

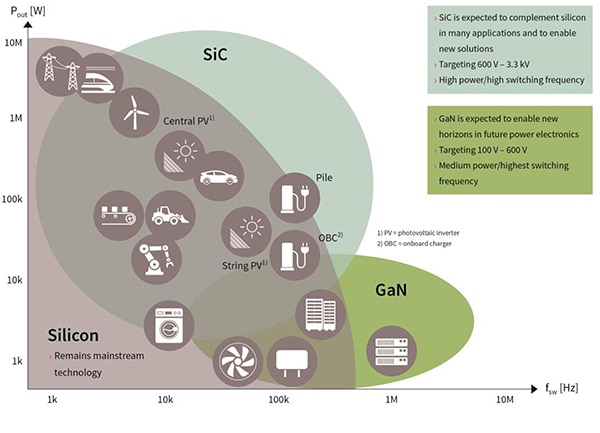

これらの特性は電源の設計者にとって重要ですが、実はより重要な点として考えられるのは、高い電子移動度によってGaNトランジスタのスイッチングがシリコンMOSFETの約1/4の時間に短縮することです。さらに、GaNデバイスのスイッチングのたびに、特定のスイッチング周波数と電流において、損失がシリコントランジスタの約10~30%になります。これにより、高電子移動度のGaNトランジスタ(HEMT)は、シリコンMOSFET、IGBT、またはシリコンカーバイド(SiC)デバイスに比べて大幅に高い周波数で駆動できます(図1)。

図1:GaN HEMTはシリコンまたはSiCデバイスよりも高い周波数のスイッチモード電源を可能にします。(画像提供:Infineon)

GaN HEMTは2つの主な理由で普及が遅れました。1つは、このデバイスは本質的にデプレッションモードの電界効果トランジスタ(FET)であるため、デフォルトのモードが「オン」であることです。対照的に、シリコンMOSFETはデフォルトで「オフ」モードのエンハンスメントモードのデバイスです。このため、GaN HEMTが適切に動作するには、慎重に調整したバイアスネットワークを追加する必要があります。もう1つは、トランジスタの製造プロセスはシリコンのような完成度の高い量産技法とは異なるため、トランジスタがより高価になることです。このような設計の複雑さと価格の高さにより、GaN HEMTのアプリケーションはハイエンドのSMPSに限られていました。

最近になって、eGaN HEMTの商用化が進みバイアスネットワークの必要性がなくなってきました。さらに、チップベンダがeGaN HEMTに基づく統合型パワーICドライバを採用し始め、設計が簡素化されています。また生産レベルの向上によって、eGaNデバイスの低価格化が実現されています。

統合型GaNソリューション

以前のeGaN HEMTを使用したハイエンドSMPSの設計では、設計者は価格の高さからこのデバイスの使用をパワートランジスタに限定し、ゲートドライバ用にはシリコンMOSFETの使用を強いられていました。「すべてシリコン」の設計と比べて性能はある程度向上しますが、複合的な設計に含まれるシリコン素子により、最大スイッチング周波数については妥協していました。また、GaNとシリコンは異なるプロセス技術を使用するため、ゲートドライバとパワートランジスタを別々のコンポーネントとして作製する必要があり、コストとプリント基板のフットプリントが増大しました。

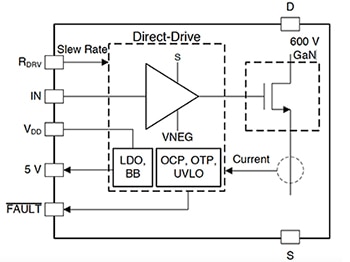

eGaNの低価格化によって、チップメーカーは両方の問題に対処できるようになったのです。たとえば、Texas Instrumentsはゲートドライバを統合したLMG3411R070 70mΩ(ミリオーム)、600VのeGaNパワー段を提供しています(図2)。

図2:Texas InstrumentsのLMG3411R070は、70mΩ、600V eGaNパワー段をそのドライバと統合しています。(画像提供:Texas Instruments)

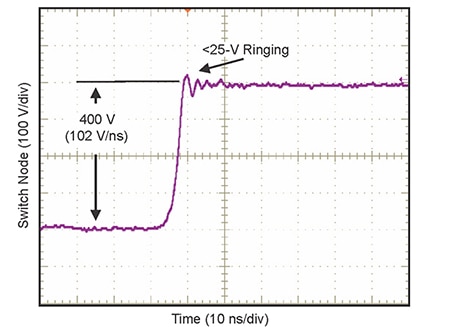

このチップは、ほぼゼロリンギングで100V/ナノ秒(ns)のスイッチングが可能です(図3)。これは、従来のシリコンパワーMOSFETの3~10V/nsの一般的なスルーレートに匹敵します。

図3:TIのLMG3411R070統合eGaNパワー段で示されるように、eGaNパワートランジスタは最小限のリンギングでMOSFETより大幅に高いスルーレートに対応します。(画像提供:Texas Instruments)

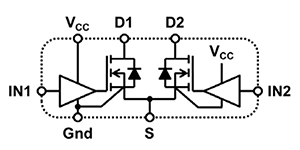

Navitas Semiconductorは同クラスの製品、NV6113を製造しています。この製品は、300mΩ、650VのeGaN HEMT、ゲートドライバ、そして関連するロジックを、5mm x 6mmのQFNパッケージに統合しています。NV6113は200V/nsのスルーレートに対応し、最大2メガヘルツ(MHz)で動作します。

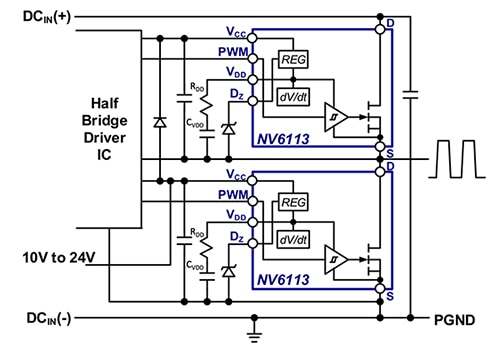

TIとNavitasのGaNパワー段などのデバイスは、よくあるハーフブリッジトポロジで使用する際に並列で展開できる一方(図4)、2つのパワートランジスタ(および関連するゲートドライバ)を同じチップに統合した他の製品が提供されています。

図4:NavitasのNV6113は図のようにハーフブリッジトポロジで並列して展開できます。(画像提供:Navitas Semiconductor)

たとえば、EPCは最近、統合型ドライバICのEPC2115を投入しました。この製品は2つのモノリシックク88mΩ、150V eGaNパワートランジスタを含んでおり、それぞれ最適化されたゲートドライバをともないます(図5)。EPC2115は低インダクタンス、2.9mm x 1.1mmのBGAパッケージで提供され、最大7MHzで動作します。

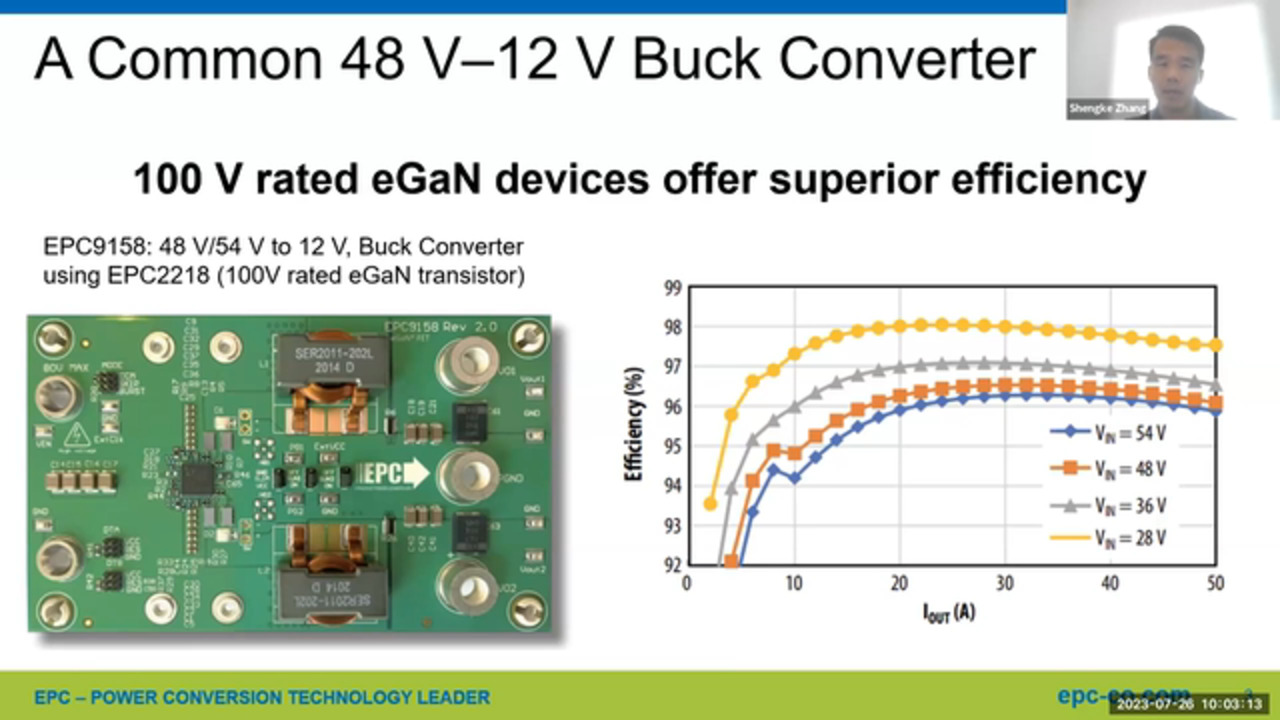

図5:EPCのeGaN統合型ドライバICには2つのパワートランジスタが含まれており、それぞれ最適化された専用のゲートドライバをともないます。(画像提供:EPC)

eGaN HEMTを使用する電源の設計は、通常、シリコンMOSFETを使用する設計と同じ原則に基づきますが、動作周波数がより高いことが周辺部品の選択に影響します。

周辺部品の選択

部品の選択に対する周波数の影響を説明するための、シンプルなDC/DC SMPS降圧(ステップダウン)トポロジの入力コンデンサについて検討します。

入力コンデンサは入力リップルの電圧振幅を減らし、過度な消費電力なしに比較的安価なバルクコンデンサで処理できるレベルにまで、リップル電流を減衰させます。ピーク-ピーク電圧リップル振幅を75ミリボルト(mV)未満に減らすことは、バルクコンデンサの電流を許容範囲内に維持するための確かな経験則です。入力コンデンサは一般にセラミックデバイスですが、これは電圧リップルの低減のために入力コンデンサの等価直列抵抗(ESR)をきわめて低くする必要があるからです。

ピーク-ピーク電圧リップル振幅を所定の大きさに低減するのに必要なセラミック入力コンデンサの値を求めるには、式1を使用できます。

![]()

式の要素の意味は次のとおりです。

- CMINは、最小限必要なセラミック入力静電容量(単位:μF)

- fSWはスイッチング周波数(単位:kHz)

- VP(max)許容される最大ピーク-ピークリップル電圧

- IOUTは定常状態の出力負荷電流

- dcはデューティサイクル(上記にて定義)

- (リファレンス1から)

ハイエンドのシリコンベースパワー段の一般的な動作値を使用した計算を行うと以下を得られます。

- VIN = 12V

- VOUT = 3.3V

- IOUT = 10A

- η = 93%

- fSW = 300kHz

- dc = 0.296

- VP(max) = 75mV

Calculated CMIN = 92µF

効率性が多少良い以外はほぼ同様の動作条件を備えたNavitasの2MHzで動作するデバイスのようなeGaNパワー段について同じ計算を繰り返すと、以下を得られます。

- VIN = 12V

- VOUT = 3.3V

- IOUT = 10A

- η = 95%

- fSW = 2000kHz

- dc = 0.289

- VP(max) = 75mV

Calculated CMIN = 13µF

CMINの低減によって、より小さなコンポーネントの使用が可能になります。

eGaN HEMTの高速スイッチングは基本的に利点になりますが、設計上の固有の問題も引き起こします。その主な課題は、非常に急峻なスルーレートに関連します。

スルーレートの制御

高スルーレート(dV/dt)は次のような問題を引き起こします。

- スイッチング損失の増加

- 放射性および伝導性EMI

- スイッチノードから結合される回路のどこかでの干渉

- 電力ループインダクタンスと他の寄生による、スイッチノードでの電圧オーバーシュートとリンギング

これらの問題は、起動時やハードスイッチングの状態で最も顕著に見られます。

Navitasの製品を使用する場合、簡単な解決策は、CVDDコンデンサとVDDピンとの間に抵抗器を加えることでターンオン時にスルーレートを制御することです(図4を再度参照)。この抵抗器(RDD)は統合型ゲートドライバのターンオン電流を設定し、パワーFETのドレインのターンオン(立ち下り)エッジスルーレートを決定します(図6)。

図6:RDD抵抗器はNV6113ターンオン電流を設定し、パワーFETのドレインのターンオン(立ち下り)エッジスルーレートを決定します。(画像提供:Navitas Semiconductor)

またLMG3411は、抵抗器(RDRV)をパワートランジスタソースに接続することで、スルーレート調整をサポートします(図2を再度参照)。抵抗器の選択により、ドレイン電圧のスルーレートが約25~100V/nsの間に設定されます。

スルーレートの選択は、最終的にトレードオフです。レートが高速なほど電力損失が減りますが、これはスイッチが高電流を同時に(そして非効率的に)伝導するときの時間の長さが短くなるからです。ただし他のパフォーマンス特性は低下します。経験則は、EMI、オーバーシュート、リンギングが仕様の範囲内に留まる最も高速なレートを目標にしています。

もう1つの設計の問題は、高周波数動作に関連する過電流のリスクです。

過電流保護の重要性

より高いスイッチング周波数を使用したSMPSの設計の主な利点は、受動部品のサイズが小型化され全体的な電力密度が高まることです。短所としては、電力密度の高まりによって、過電流が生じたときの潜在的なダメージが増大することがあります。過電流のイベントは、SMPSでは消えないリスクの1つです。さまざまな問題の中で、発生源となるプリント基板トレースからの外部寄生インダクタンスのために、過電流スパイクは誤トリガの原因になります。

高速な過電流保護(OCP)は従来のMOSFETを使用するSMPSにとって重要ですが、次の理由でeGaN HEMTにとってはさらに重要になります。

- 同じブロッキング電圧とオン状態抵抗の場合、eGaN HEMTの面積の方が大幅に小さく、過電流が生じたとき熱の蓄積を消散させるのが非常に難しくなります。

- eGaN HEMTが線形領域で動作しているときに過電流を検出する必要があり、それができないと、デバイスがすぐに飽和領域に達して、過剰な消費電力とダメージを生じる原因になります。

OCPを実現する従来の手法では、電流センストランス、シャント抵抗器、不飽和検出回路を使用します(表)。残念ながら、これらは電力ループにおける寄生インダクタンスと抵抗を増すことでシステム性能に負の影響を与える可能性があり、これによりスルーレートが低下し結果的に消費電力が高まることが余儀なくされます。さらに、センストランスやシャント抵抗器などのディスクリートデバイスがコスト増加につながり基板の面積も占有します。

OCPの別の手法は、電流センシング素子、コントローラに信号をレポートするレベルシフタ、検出回路を使用してGaN FETのドレイン-ソース電圧(VDS)をセンスすることです。この方法には、回路のパフォーマンスに影響する寄生インダクタンスや抵抗を生じないという利点がありますが、主にGaNの大きな温度係数によって精度に欠けます。

OCPを実現するもう1つの選択肢は、統合OCP機能を含む統合型eGaNパワー段を選ぶことです。この手法では、前述の2つの手法の短所が解消されます。TIのLMG3411は、この機能を含む製品の1例です。LMG3411の保護回路は、過電流が検出された場合に、eGaN HEMTSを100ns以内にオフにできます。次のサイクルでPWMがローに戻ると、出力フォールト信号はなくなります。これにより、次のサイクルでeGaN HEMTが正常にターンオンし、出力時の混乱を最小限にします。

|

表:GaN HEMTパワー段のOCPオプション概要統合OCPを含むパワー段の採用は、この技術の入門設計者にとって最もシンプルなソリューションです。(画像提供:Texas Instruments)

結論

ソーラーインバータ、サーバファームなどのアプリケーションでの高エネルギー密度SMPSに対する需要の増加や、デバイスあたりの価格低下を背景に、eGaN HEMTはこれまで以上に幅広い電源設計にとって魅力的な選択肢になりました。eGaN HEMTを使用した設計には難しい側面もありますが、ゲートドライバとパワートランジスタを統合したeGaN HEMTパワー段の登場により、SMPSの設計者は今後の高電力密度の設計にこの技術をこれまで以上に簡単に組み込めるようになりました。

リファレンス

- 『Input and Output Capacitor Selection(入出力コンデンサの選択)』、Jason Arrigo著、Texas Instruments、アプリケーションレポートSLTA055、2006年2月

免責条項:このウェブサイト上で、さまざまな著者および/またはフォーラム参加者によって表明された意見、信念や視点は、DigiKeyの意見、信念および視点またはDigiKeyの公式な方針を必ずしも反映するものではありません。