データセンターおよび産業用システム向けの高性能プログラム可能クロックジェネレータの実装

EthernetやPCIe(ペリフェラルコンポーネントインターコネクトエクスプレス)通信をサポートする正確なタイミングは重要であり、サーバ、ストレージシステム、ネットワーキングや組み込み産業用システムを設計する際には課題となる場合があります。単にEthernetやPCIeバスを追加すればいいというものではありません。一般的な設計では、複数のバスが存在し、そのすべてがジッタを最小限に抑えた正確なタイミングをサポートする必要があります。一般的なシステムでは、最大650MHzのさまざまな周波数で動作する通信バスを組み合わせて使用する必要があります。

プリント回路(pc)基板のスペースをできるだけ小さくするソリューションが必要です。また、EthernetとPCIeではタイミングのニーズが異なるため、設計の難易度が上がります。これらの要求に応えるため、EthernetおよびPCIeバス用に最大12個のリファレンスクロックを同時に供給できる小型のプログラム可能クロックジェネレータICを利用することができます。

このブログでは、EthernetおよびPCIeバスのタイミングニーズについて簡単に説明してから、複数のPCIeバスとEthernetバスのニーズを同時にサポートできるRenesasの小型プログラム可能クロックジェネレータソリューションを紹介します。また、サーバ、ストレージシステム、ネットワーキング、組み込み産業用システムなどのタイミング回路の開発を加速させる評価ボードも紹介します。

ジッタの制御と電磁干渉(EMI)の最小化

PCIeとEthernetは用途が異なります。PCIeアプリケーションには、プリント基板上のチップ間通信や拡張カードとの接続が含まれます。一方、Ethernetは、ローカルエリアネットワーク(LAN)やストレージエリアネットワーク(SAN) などのアプリケーションに使用されます。動作環境が異なれば、タイミング回路に求められるものも変わります。

ジッタの減衰は、Ethernetネットワークにおいて極めて重要です。たとえば、最大650MHzの高速Ethernetでは、信号の完全性、伝搬遅延の低減、予測可能な動作を確保するために、RMS(二乗平均平方根)位相ジッタを最大150フェムト秒(fs)に制限する必要があります。

PCIeバスでは、ジッタ制御に加え、スペクトラム拡散変調を採用することで、ジッタのエネルギーをより広い周波数範囲に拡散し、電磁干渉(EMI)を最小化することができます。EMIを制御することで、プリント基板上のシールドが不要になり、システムコストの削減やシステム統合のスピードアップにつながります。RenesasのVersaClockクロックジェネレータは、スペクトラム拡散変調の量を制御するため、特定のアプリケーションで求められるコストと性能のトレードオフを最適化することができます。

少ないスペースで多くのことを実現

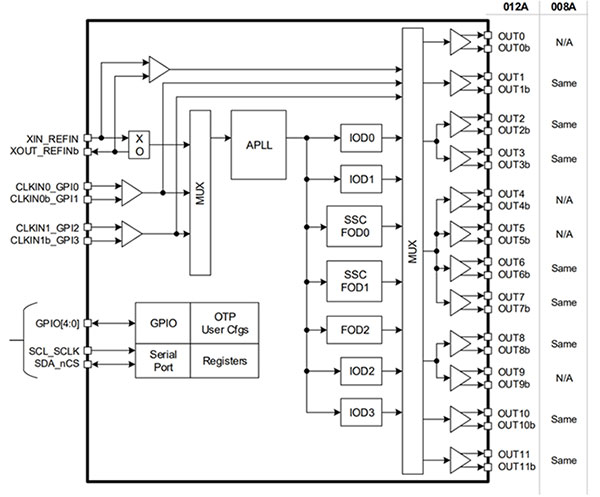

RenesasのVersaClockクロックジェネレータをベースにした統合タイミングソリューションにより、少ないプリント基板スペースでより多くのことを実現できます。これらは8個または12個の独立したクロックを搭載しており、以下のような特長があります(図1)。

- 169fs RMS(10kHz~20MHz、156.25MHz)の位相ジッタ

- PCIe Gen6共通クロック(CC) 27fs RMS

- PCIeのSRIS(Separate Reference Independent Spread)およびSRNS(Separate Reference No Spread)動作のサポート

- 1kHz~650MHzの低電圧差動シグナリング(LVDS)および低消費電力・高速電流ステアリングロジック(LP-HCSL)出力

図1:VersaClockプログラム可能クロックジェネレータは、最大8クロック(右列「008A」)または最大12クロック(列「012A」)をサポートしています。(画像提供:Renesas)

図1:VersaClockプログラム可能クロックジェネレータは、最大8クロック(右列「008A」)または最大12クロック(列「012A」)をサポートしています。(画像提供:Renesas)

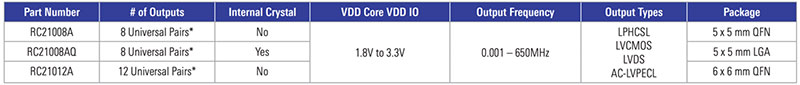

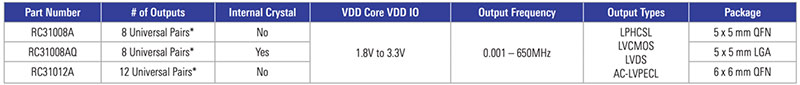

5つの独立したクロックを備えたタイミングソリューションを構築する従来の方法では、約3 x 3mmの基板スペースを占める共通の水晶発振回路と、それぞれ約5 x 3mmのスペースを占める4つのサブ発振器が必要でした。または、 RC21008A のように、5 x 5mmを占有するVersaClock ICを1つだけ使用することも可能です。また、同じICで最大8つのクロック出力に対応できるため、基板スペース、部品点数、コストをさらに削減することが可能です。RC21008Aの主な特長を、VersaClock 7ファミリの他の2つのICであるRC21008AQとRC21012Aとともに示します(表1)。

表1:VersaClock 7ファミリの3つのクロックジェネレータの主な特長を示します。「*」は、出力が差動またはLVCMOSに設定可能であることを示しています。(表提供:Renesas)

表1:VersaClock 7ファミリの3つのクロックジェネレータの主な特長を示します。「*」は、出力が差動またはLVCMOSに設定可能であることを示しています。(表提供:Renesas)

ジッタの減衰

RC31008A、RC31008AQ、RC31012Aのプログラマブルジッタアッテネータは、ACまたはDCカップリングのシングルエンドまたは差動出力でのコンバータ同期をサポートするJEDEC JESD204B/Cや、ネットワークベースの同期をサポートする同期式Ethernet(SyncE)などのネットワーク同期機能を備えています。VersaClockクロックジェネレータICと同様に、これらのジッタアッテネータは8または12出力で提供され、ソリューションのサイズとコストを低減します(表2)。

表2:VersaClock 7ファミリのジッタアッテネータ。「*」は、差動またはLVCMOSに設定可能な出力数を示しています。(表データ:Renesas)

表2:VersaClock 7ファミリのジッタアッテネータ。「*」は、差動またはLVCMOSに設定可能な出力数を示しています。(表データ:Renesas)

評価ボード

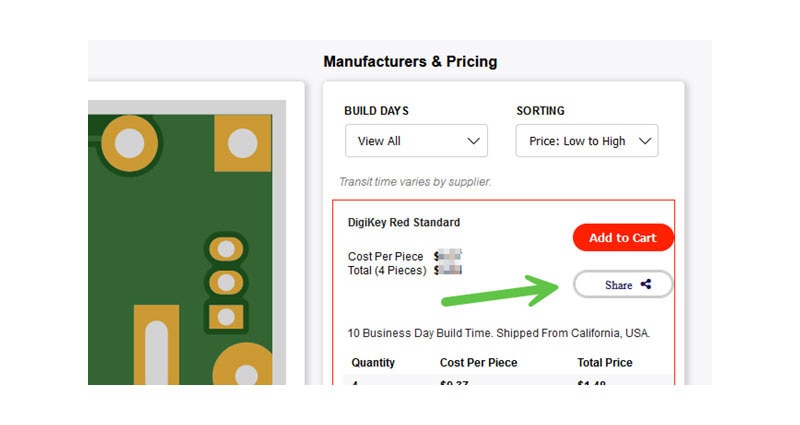

Renesasは、開発活動のスピードアップを図るため、8出力と12出力のクロックジェネレータ設計にそれぞれ対応したRC21008-EVB(図2)およびRC21012-EVB、8出力と12出力のジッタアッテネータにそれぞれ使用可能なRC31008-EVBおよびRC31012-EVBの評価ボードを提供しています。これらの評価ボードは、PCIeコンプライアンスとスペクトラム拡散性能のためにシンセサイザモードでのクロック生成をサポートし、ジッタ減衰モードもサポートすることが可能です。サポートするリファレンス入力の周波数範囲は、差動モードで1kHz~650MHz、シングルエンドモードで1kHz~200MHzです。標準消費電力は1W未満で、ジッタの仕様は以下の通りです。

- 150 fs RMS位相ジッタ(12kHz~20MHz、整数値)

- 200 fs RMS位相ジッタ(12kHz~20MHz、分数値)

図2:VersaClock 7シリーズ用のRC21008-EVBのような評価ボードは、8出力ソリューションの開発をサポートします。(画像提供:Renesas)

図2:VersaClock 7シリーズ用のRC21008-EVBのような評価ボードは、8出力ソリューションの開発をサポートします。(画像提供:Renesas)

まとめ

上述したように、RenesasのVersaClockクロックジェネレータとジッタアッテネータは、さまざまなデータ処理および産業用アプリケーションにおいて、PCIeおよびEthernetバス用の高性能、小型、低コストのタイミングソリューションの開発に使用できます。手始めとして、開発プロセスのスピードアップと市場投入期間の短縮を実現するために、評価ボードが入手可能です。

Have questions or comments? Continue the conversation on TechForum, Digi-Key's online community and technical resource.

Visit TechForum