ブリッジレストーテムポール力率補正の使用タイミングと使用方法

DigiKeyの北米担当編集者の提供

2022-09-28

サーバ、ネットワーク、5G通信、産業用システム、電気自動車など、さまざまなアプリケーションに使用されるAC/DC電源の重要要件は、高い力率(PF)と高い効率です。しかし、電源設計者にとっての課題は、IEC 61000-3-2などの規格におけるPFおよび電磁両立性(EMC)の要件、さらにはEnergyStarの最新の80 PLUS Titanium効率規格をすべて満たさなければならないことです。後者は、10%負荷で90%以上、全負荷で94%以上の効率を要件としています。従来の昇圧PF補正(Boost PF Correction:PFC)トポロジでは、高いPFと良好なEMCを実現することはできますが、比較的効率の悪いダイオードブリッジを含んでいるため、必要とされている効率規格を満たすことは困難です。

ダイオードブリッジをブリッジレストーテムポールPFCトポロジに置き換えることで、高いPFと高い効率を両立させることができます。しかし、このトポロジは、整流用のライン周波数で動作する低速ループと、昇圧部用の高周波ループという2つの制御ループが存在する、より複雑な構成となります。2つの制御ループをゼロから設計すると、時間がかかるため製品化が遅れるとともに、製品のコストやサイズが必要以上に大きくなってしまう可能性があります。

このような問題に対応するには、ブリッジレストーテムポールPFC用に最適化されたPFCコントローラICを2つの制御ループの代わりに利用することができます。これらのコントローラは、内部補正されるデジタルループを持ち、ホール効果センサを必要とせずにサイクル毎の電流制限を実装でき、シリコンMOSFETやSiC(シリコンカーバイド)や窒化ガリウムなどのワイドバンドギャップ(WBG)スイッチングデバイスとともに使用することが可能です。これらのコントローラによって行われるPFCは、AC90~265ボルトの入力により、最大99%の効率で動作することができます。

本稿では、AC/DC電源が満たすべき業界標準について簡単に説明し、さまざまなPFCトポロジの性能を比較して、ブリッジレストーテムポールPFCがどのような場合に最適かを明らかにします。次いで、onsemiのコントローラIC(ブリッジレストーテムポールPFC用に最適化済み)、サポート部品、評価ボード、設計提案(開発スピードアップ用)を紹介します。

複雑になりがちな効率の算出

電源の効率の算定は、AC部品とDC部品を両方とも考慮に入れなければならないため、想像されるのよりも複雑です。基本的な効率なら、入力電力と出力電力の比を算出すれば済みますが、一般的なAC/DC電源の入力電力は純粋な正弦波ではないため、AC電源から引き出される同相の電力と逆相の電力に差が生じます。この差がPFとして算出されるのです。AC/DC電源装置の効率に関する説明を尽くすには、DC効率とそのPFも説明する必要があります。ところが、この説明を難しくしているのは、効率曲線が平坦でなく、効率とPFが入力電圧や出力負荷などのパラメータによって変化することです。

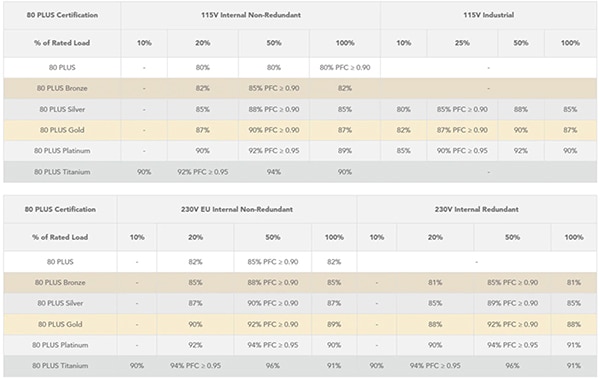

これらの変数も考慮するため、EnergyStarなどの効率規格では、PFの要件とともに、さまざまな入力電圧およびいろいろな負荷レベルでの効率を定義しています(表 1)。最高レベルの「80 PLUS Titanium」は、115ボルトAC入力に対し、最低の効率を、定格負荷の10%と100%の両方で90%、定格負荷の50%で94%として規定するとともに、PFを定格負荷の20%で95%以上と規定しています。230ボルトAC入力では、より高い効率が要求されます。また、電源には、電源ラインの高調波に制限を設けるIEC 61000-3-2に適合することが求められています。

表1:効率の要件だけでなくPFの要件も含んでいるEnergyStarをはじめとする性能規格(画像提供:onsemi)

表1:効率の要件だけでなくPFの要件も含んでいるEnergyStarをはじめとする性能規格(画像提供:onsemi)

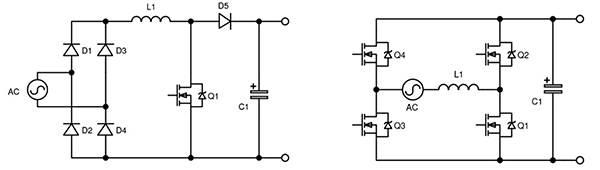

PFCで一般的な2つのアプローチは、ダイオード整流によるブーストコンバータと、より複雑で高効率な、アクティブ整流によるトーテムポールトポロジです(図1)。ブーストコンバータによるPFCは、PFおよび効率の基本的要件を満たすことはできますが、80 PLUS Titaniumのような厳しい要件には不十分です。たとえば、昇圧PFCでは、DC/DC段で2%の損失、ライン整流/PFC段で1%の損失(低ライン動作では約2%まで上昇することもあります)が発生します。低ライン時の損失が約4%あるため、「入力230ボルトACと、50%負荷で96%の効率」という80 PLUS Titaniumの要件を満たすのは困難なことです。最高レベルの効率が求められるアプリケーションでは、ダイオード整流器を同期整流に置き換えることで、PFC段の損失を低減することができます。

図1:2大PFCトポロジ:基本的なブーストコンバータPFCトポロジ(左)とトーテムポールPFCトポロジ(右)(画像提供:onsemi)

図1:2大PFCトポロジ:基本的なブーストコンバータPFCトポロジ(左)とトーテムポールPFCトポロジ(右)(画像提供:onsemi)

上記のトーテムポールPFCでは、Q3とQ4が、ライン周波数で同期整流を行うスローレッグとなり、Q1とQ2が、整流した電圧を380ボルトDCなどの高いレベルに昇圧するファーストレッグとなっています。Q1、Q2に低オン抵抗(RON)のMOSFETを使用したトーテムポールを実装することは可能ですが、MOSFETの逆回復による高周波のスイッチング損失により効率が低下します。そのため、トーテムポールPFCの設計では、Q1、Q2のシリコンMOSFETを、逆回復損失のほとんどないSiCまたはGaNパワースイッチに置き換えることが多くなっています。

制御の最適化

PFCを設計する際に必要なもう一つの決定事項は、制御手法の選択です。PFCは連続伝導モード(CCM)、不連続伝導モード(DCM)、臨界伝導モード(CrM)で動作することができます。これらのモードは、昇圧インダクタ(図1のL1)の動作特性によって異なります。CCMは、昇圧インダクタを有効に活用して伝導損失とコア損失を低く抑えることができますが、ハードスイッチングであり、動的損失が高くなります。DCMは低電力動作には効率的ですが、ピーク電流とrms電流が比較的大きく、昇圧インダクタの伝導損失とコア損失が大きくなるという課題を抱えています。

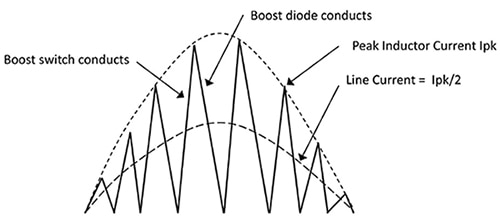

CrMは、数百ワットまでの設計にした方が、より高い効率を提供することができます。CrMでは、ライン電圧と負荷電流の変化を監視し、スイッチング周波数をCCMとDCMの間となるように調整します。CrMはターンオン損失が低く、ピーク電流を平均電流の2倍に制限するので、伝導損失とコア損失を適正なレベルに維持することができます(図2)。

図2:CrM PFC昇圧Ipk(インダクタのピーク電流)は入力ライン電流の2倍に制限されています。(画像提供:onsemi)

図2:CrM PFC昇圧Ipk(インダクタのピーク電流)は入力ライン電流の2倍に制限されています。(画像提供:onsemi)

しかし、CrMの利用にはいくつかの課題があります。

- CrMはハードスイッチング方式のトポロジであるため、昇圧デバイスの順回復により、損失が加わって出力電圧のオーバーシュートを引き起こす可能性があります。

- 軽負荷時には非常に高い周波数で動作するため、スイッチング損失が増加し、効率が低下します。

- 4つのアクティブデバイスを制御する必要があるとともに、PFCインダクタのゼロ電流を検出して出力電圧を調整する必要があります。

CrMを実装するには、回路内センサを使用するだけでなく、複雑な制御アルゴリズムを実行するマイクロコントローラ(MCU)も使用します。上記のような性能上の課題を考慮したアルゴリズムのコーディングは、リスクがあるほか、時間もかかるので、製品化が遅れる懸念があります。

ノーコードトーテムポール

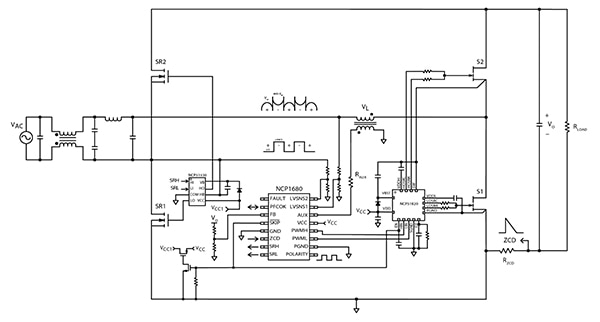

前述の懸念に対処するには、onsemiの混合信号コントローラNCP1680ABD1R2Gを利用することで、統合型でノーコードのCrMトーテムポールPFCソリューションを手に入れます。これは、SOIC-16パッケージのコントローラであり、車載アプリケーション向けのAEC-Q100認定を受けており、低損失で低コストの抵抗電流センシングを特長とし、ホール効果センサを必要としないサイクル毎の電流制限保護を実装しています(図3)。内部的に補償されるデジタル電圧制御ループにより、負荷範囲全体にわたって性能が最適化されるので、PFCの設計を簡素化することができます。

図3:NCP1680 CrMコントローラは、低コストで効率の良い抵抗電流センシング(回路図右下のZCD)を採用しています。(画像提供:onsemi)

図3:NCP1680 CrMコントローラは、低コストで効率の良い抵抗電流センシング(回路図右下のZCD)を採用しています。(画像提供:onsemi)

高速ゲートドライバ

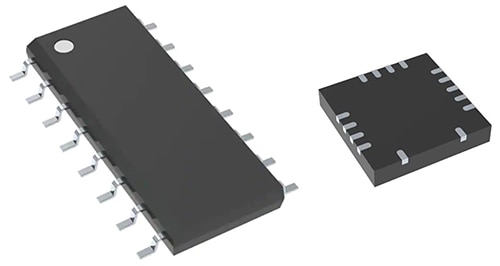

NCP1680コントローラは、onsemiの4 x 4ミリメートル(mm)15ピンQFNパッケージの高速ゲートドライバNCP51820と組み合わせることができます。ハーフブリッジトポロジにおけるGIT(ゲート注入トランジスタ)GaN(窒化ガリウム)HEMT(高電子移動度トランジスタ)とエンハンスメントモード(eモード)GaNパワースイッチとの使用向けに設計されています(図4)。

図4:NCP1680コントローラ(左)は、NCP51820高速ゲートドライバ(右)と組み合わせることで、トーテムポールPFCにおいてGaNパワーデバイスを駆動することができます。(画像提供:onsemi)

図4:NCP1680コントローラ(左)は、NCP51820高速ゲートドライバ(右)と組み合わせることで、トーテムポールPFCにおいてGaNパワーデバイスを駆動することができます。(画像提供:onsemi)

たとえば、NCP51820AMNTWGでは、伝搬遅延を短縮して一致させ、コモンモード電圧範囲がハイサイドドライブ向けに-3.5~+650ボルト(標準)となっていることが特長です。ドライバ段は、GaNデバイスのゲートを電圧ストレスから保護するために専用の電圧レギュレータを備えています。NCP51820ゲートドライバは、UVLO(独立の不足電圧ロックアウト)機能とサーマルシャットダウン保護機能を備えています。

製品化までの時間を短縮するには、評価ボード(EVB)NCP51820GAN1GEVBを使用できます。このEVBは、設計者がトーテムポール構成において2つのGaNパワースイッチを効率的に駆動できるようにNCP51820ドライバの性能を検討するのに役立ちます。NCP51820GAN1GEVBは、1310mil(1/1000インチ) x 1180milの4層プリント基板を使用して設計されています。NCP51820 GaNドライバと2つのeモードGaNパワースイッチをハーフブリッジ構成で搭載しています(図5)。

図5:EVB NCP51820GAN1GEVBは、NCP51820ドライバと2つのEモードGaNスイッチをハーフブリッジ構成で搭載しています。(画像提供:onsemi)

図5:EVB NCP51820GAN1GEVBは、NCP51820ドライバと2つのEモードGaNスイッチをハーフブリッジ構成で搭載しています。(画像提供:onsemi)

設計上のアドバイス

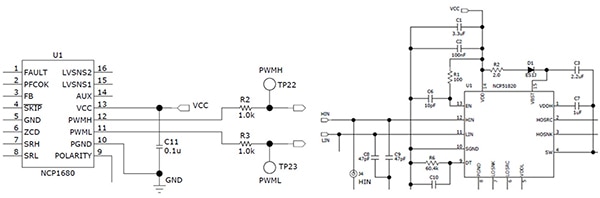

設計者がこれらのICを使用する際に、最高の性能を実現するために行うべき簡単な設計上のアドバイスがあります。たとえば、ノイズが信号経路に流れ込んで誤ってNCP51820ゲートドライバをトリガすることを防ぐために、onsemiはNCP1680からの制御信号(PWMHとPWML)をゲートドライバICの入力時に直接フィルタ除去することを推奨しています。1キロオーム(kΩ)の抵抗器と47または100ピコファラド(pF)のコンデンサをドライバのピンに直接配置することで、十分なフィルタ除去が可能です(図6)。

図6:NCP51820ゲートドライバICの入力時に直接、NCP1680からのPWMHとPWMLの制御信号をフィルタ除去することにより、NCP51820が誤ってトリガされるなどノイズの影響を防止することができます。フィルタ除去は上図では、1kΩの抵抗器(中央左)と47pFのコンデンサ(中央右)を使って実現されています。(画像提供:onsemi)

図6:NCP51820ゲートドライバICの入力時に直接、NCP1680からのPWMHとPWMLの制御信号をフィルタ除去することにより、NCP51820が誤ってトリガされるなどノイズの影響を防止することができます。フィルタ除去は上図では、1kΩの抵抗器(中央左)と47pFのコンデンサ(中央右)を使って実現されています。(画像提供:onsemi)

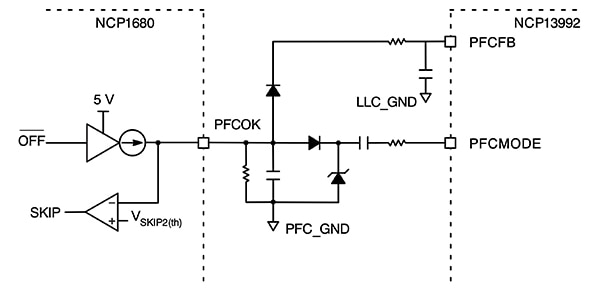

NCP1680のスキップ/スタンバイモードは、無負荷および軽負荷で非常に優れた性能を実現しますが、PFCOKピンにパルスを入力するか、SKIPピンを接地してNCP13992共振モードコントローラとインターフェース接続することにより、外部からトリガする必要があります(図7)。インターフェース回路の成分値は、NCP1680 EVBに記載されているものと同じである必要があります。通常動作時、NCP13992共振モードコントローラの PFCMODEピンは、同コントローラのVCCバイアス電圧と同じ電圧になります。コンバータがスキップモードになると、NCP1680はグランドにパルスを送ります。コンバータがスキップモードに入るには、PFCOKピンの電圧が50マイクロ秒(μs)を超えて400ミリボルト(mV)未満の状態であり続ける必要があります。

図7:NCP1680のスキップ/スタンバイモードを呼び出すために必要な外部トリガ回路の例。(画像提供:onsemi)

図7:NCP1680のスキップ/スタンバイモードを呼び出すために必要な外部トリガ回路の例。(画像提供:onsemi)

まとめ

80 PLUS Titaniumなど最新のEnergyStar規格の効率、EMC、PFの要件を同時に満たすことは、一般的なブーストコンバータのPFCトポロジでは困難な場合があります。そこで、代わりに、トーテムポールPFCトポロジを採用します。これまで見てきたように、設計者は、NCP1680混合信号コントローラのほか、NCP51820ゲートドライバ、評価ボード、および設計上のベストプラクティスを使用することで、CrMトーテムポールPFCソリューションを、要求される規格に適合しながら素早く実装することができます。

お勧めの記事

免責条項:このウェブサイト上で、さまざまな著者および/またはフォーラム参加者によって表明された意見、信念や視点は、DigiKeyの意見、信念および視点またはDigiKeyの公式な方針を必ずしも反映するものではありません。