統合型降圧DC/DCモジュールを使用して、高密度で効率的な電力変換と低EMIを実現

DigiKeyの北米担当編集者の提供

2020-11-24

電子機器の集積度が高まり、普及が進むにつれ、設計者はコスト、サイズ、電磁妨害(EMI)を低減しながら効率を向上させるという圧力を常に受けています。電源は電力密度と効率を向上させてきましたが、設計者は、ASIC、DSP、FPGA、マイクロコントローラなどを組み合わせた異種処理アーキテクチャ向けのマルチレール電源ソリューションを開発するという課題にも直面しています。

降圧DC/DCコンバータは従来、このようなアーキテクチャの給電に使用されてきましたが、電源レールの数が増加しているため、制御ICと内蔵または外付けパワーMOSFET、さらに外付けインダクタやコンデンサを備えた従来のディスクリート降圧DC/DCコンバータを使用することは、複雑で時間がかかる可能性があります。その代わりに、設計者は、EMIをより適切に制御し、発熱を抑え、フットプリントを小さくする、複数のレールとプログラム可能なシーケンスを備えた自己完結型の降圧DC/DCコンバータモジュールを使用できます。

この記事では、自己完結型の降圧DC/DCモジュールの概念を紹介する前に、組み込み設計の電源システムのニーズを考察し、さまざまなアプローチと設計者が考慮すべきことを取り上げます。次に、Monolithic Power Systemsのサンプルデバイスを使用して、これらのモジュールの性能上の利点を最大化するために設計者が留意すべき設計とレイアウトの考慮事項を手短に説明します。

組み込みシステムに多くの電源レールが必要な理由

5G基地局のような組み込み設計は、ホームオートメーションや産業用オートメーション、自律走行車、ヘルスケア、スマートウェアラブルなどのアプリケーションで、スマートフォンやスマート接続デバイスからの増大し続けるデータ量の要件をサポートすることを目的としています。このような基地局は通常、48ボルトの入力電源を使用します。この入力電源はDC/DCコンバータによって24ボルトまたは12ボルトに降圧され、3.3ボルトから1ボルト未満の多くのサブレールにさらに降圧されて、ベースバンド処理ステージのASIC、FPGA、DSP、およびその他のデバイスに給電します。多くの場合、電源レールは起動とシャットダウンのためにシーケンスを必要とするため、設計者にとって電力システムの複雑さがさらに増します。

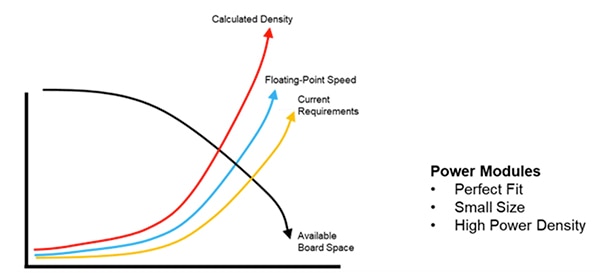

5G基地局の例では、従来のCPUだけでは処理要件を満たすことができなくなってきています。ただし、FPGAを搭載したアクセラレータカードを使用することで、システムの再構成可能性、柔軟性、短い開発サイクル、高度な並列計算、低レイテンシといったメリットがあります。しかし、FPGA電源に利用できるスペースが縮小しており、電源レール性能の要件が複雑になっています(図1)。

- 出力電圧オフセット:電圧レールの出力電圧偏差は±3%未満で、かつ設計に十分なマージンを残す必要があります。制御ループを最適化して帯域幅を拡大し、安定性を確保することで、デカップリングコンデンサを適用し、慎重に設計する必要があります。

- 単調な起動:すべての電圧レールの起動電圧は単調に上昇しなければならず、出力電圧が起動値に戻らないように設計する必要があります。

- 出力電圧リップル:定常状態操作の場合、アナログ電圧レールを除くすべての電圧レールの出力電圧リップルは、高くても10ミリボルト(mV)でなければなりません。

- タイミング:FPGAは、起動時およびシャットダウン時に特定のタイミング要件を満たす必要があります。

図1:コンピューティング要件の増加に伴い、アクセラレータカードのプロセッサのサイズが大きくなり、電源に利用可能なスペースが少なくなっています。(画像提供:Monolithic Power Systems)

図1:コンピューティング要件の増加に伴い、アクセラレータカードのプロセッサのサイズが大きくなり、電源に利用可能なスペースが少なくなっています。(画像提供:Monolithic Power Systems)

プロセッサは、データ処理帯域幅の要件が厳しくなるにつれて、より多くの電流と電力を必要とします。アクセラレータカードの計算密度と浮動小数点速度の要件も、業界で満たすのがますます困難になっています。アクセラレータカードのスロットは通常PCIe規格であるため、ボードのサイズは固定されています。コンピューティング要件の増加により、プロセッサのサイズが大きくなり、電源に利用可能なスペースが少なくなっています。

電源システム設計の選択肢

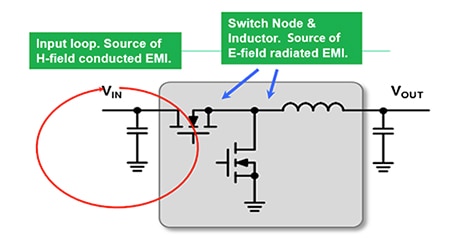

制御ICと内蔵または外付けパワーMOSFET、さらに外付けインダクタやコンデンサを備えた従来のディスクリート降圧DC/DCコンバータを使用することは、組み込みシステムへの給電の1つのアプローチです。上述したように、マルチレール電源ソリューションが必要な場合、設計者にとっては複雑で時間のかかるプロセスとなります。設計者は、効率の最大化とソリューションサイズの最小化を考慮するだけでなく、コンバータとインダクタ回路のスイッチング電流によって引き起こされる伝導EMIと放射EMIを最小限に抑えるために、フィルタコンポーネントのレイアウトと配置にも注意しなければなりません(図2)。

図2:ディスクリート降圧DC/DCコンバータには、設計者が管理しなければならない複数のEMI源があります。(画像提供:Monolithic Power Systems)

図2:ディスクリート降圧DC/DCコンバータには、設計者が管理しなければならない複数のEMI源があります。(画像提供:Monolithic Power Systems)

DC/DCコンバータは通常、グランド接続された出力パワーMOSFETスイッチングノードと、グランド接続された入力コンデンサとの間に形成される電流ループ経路から磁界を介して伝導EMIを発生させます。また、DC/DCコンバータは、MOSFETスイッチングノードからインダクタ接続部に流れる電流によって生じる電界を介して放射EMIを発生させ、この電界は、高入力電圧レベルからグランドに連続してスイッチングしているため、dV/dtが高くなります。そして最後に、DC/DCコンバータは、インダクタ内で発生する電磁界を介してEMIを発生させます。設計を正しく行わないと、多くの場合、EMIラボでの再テストに時間がかかり、何度も設計を繰り返すことになります。

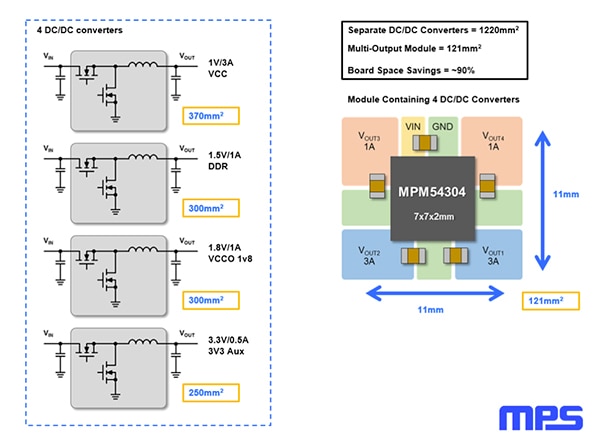

ディスクリート降圧DC/DCコンバータを使用してASICやFPGAに給電するための4レールのソリューションは、1220平方ミリメートル(mm2)を占有する可能性があります(図3)。これを電源管理IC(PMIC)ベースのソリューションを使用することで、約350mm2に削減することができます。別の方法として、設計者は自己完結型のクワッド出力DC/DCコンバータモジュールを使用することで、設計プロセスを簡素化して市場投入までの時間を短縮しながら、ソリューションサイズをわずか121mm2に縮小することができます。半導体プロセス技術とパッケージ構造の進歩により、最新世代のDC/DCモジュールは、小さなフォームファクタで非常に高い電力密度、高効率、良好なEMI性能を実現しています。

図3:統合型DC/DCモジュールソリューションを使用すると、ディスクリートソリューションと比較して基板スペースを最大90%削減できます。(画像提供:Monolithic Power Systems)

図3:統合型DC/DCモジュールソリューションを使用すると、ディスクリートソリューションと比較して基板スペースを最大90%削減できます。(画像提供:Monolithic Power Systems)

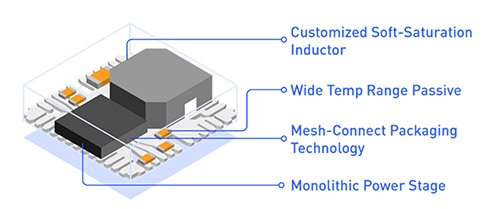

パッケージ内フリップチップや「メッシュコネクト」リードフレーム技術などの新しい構造技術は、ワイヤボンディングや追加の内部プリント基板を使用せずに、IC、インダクタ、受動部品をリードフレームに直接実装できることを意味しています(図4)。内部プリント基板やワイヤボンディングを使用する従来の構造と比較して、接続トレースの長さを最小限に抑えることができ、受動部品への直接接続によりインダクタンスを低く保ち、EMIを最小限に抑えます。

図4:相互接続にリードフレームを利用した新しい構造は、EMIの抑制、放熱性の向上、フットプリントの小型化などの多くの利点を持っています。(画像提供:Monolithic Power Systems)

図4:相互接続にリードフレームを利用した新しい構造は、EMIの抑制、放熱性の向上、フットプリントの小型化などの多くの利点を持っています。(画像提供:Monolithic Power Systems)

ターゲットプリント基板に直接面実装されるランドグリッドアレイ(LGA)パッケージフォーマットを使用することで、EMIを放射する可能性のあるリードを持つ代替シングルインライン(SIL)またはSILパッケージ(SIP)スタイルのコンバータよりも低いEMIプロファイルを提供します。

クワッド出力プログラム可能統合型DC/DCモジュール

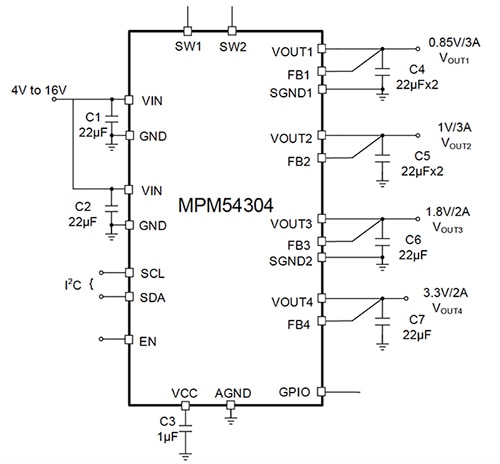

組み込みシステムのマルチレール、高電力密度のニーズを満たすために、設計者はMonolithic Power SystemsのMPM54304を利用することができます(図5)。MPM54304は、4つの高効率降圧DC/DCコンバータ、インダクタ、および柔軟な論理インターフェースを統合する完全な電源管理モジュールです。MPM54304は4ボルト~16ボルトの入力電圧範囲で動作し、0.55ボルト~7ボルトの出力電圧範囲をサポートできます。4つの出力レールは、最大3アンペア(A)、3A、2A、および2Aの電流をサポートできます。2つの3Aレールと2つの2Aレールを並列に接続して、それぞれ6Aと4Aを提供できます。設計者は、並列モードでの最大出力電流が総消費電力によって制限されることに注意する必要があります。これにより、次の複数の出力構成を生成する柔軟性が得られます(これらの出力構成は、総消費電力の制限の影響を受けます)。

- 3A、3A、2A、2A

- 3A、3A、4A

- 6A、2A、2A

- 6A、4A

図5:MPM54304は、クワッド出力を備えた完全な降圧電源管理モジュールです。このモジュールは4ボルト~16ボルトの入力電圧範囲で動作します。(画像提供:Monolithic Power Systems)

図5:MPM54304は、クワッド出力を備えた完全な降圧電源管理モジュールです。このモジュールは4ボルト~16ボルトの入力電圧範囲で動作します。(画像提供:Monolithic Power Systems)

MPM54304はまた、起動およびシャットダウンのための内部シーケンスを提供します。レール構成とシーケンスは、マルチタイムプログラマブル(MTP)電子ヒューズまたはI2Cバスを介して事前にプログラムすることができます。

この固定周波数コンスタントオンタイム(COT)制御のDC/DCコンバータは、高速な過渡応答を提供します。デフォルトの1.5メガヘルツ(MHz)スイッチング周波数は、外付けコンデンサのサイズを大幅に削減します。連続電流モード(CCM)動作中は、スイッチングクロックはロックされ、降圧1から降圧4に位相シフトされます。出力電圧はI2Cバスで調整可能であるか、MTP電子ヒューズによってプリセットされています。

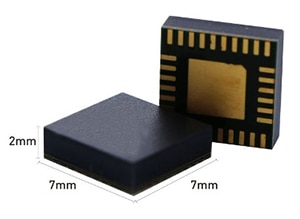

完全な保護機能には、不足電圧ロックアウト(UVLO)、過電流保護(OCP)、サーマルシャットダウンが含まれます。MPM54304は、必要な外付け部品の数が最小限で済み、省スペースのLGA(7mm x 7mm x 2mm)パッケージで提供されます(図6)。LGAの薄型化により、基板の裏側やヒートシンクの下に配置するのに適しています。

図6:MPM54304のLGAパッケージは、低EMIで小型かつ薄型のソリューションを提供します。(画像提供:Monolithic Power Systems)

図6:MPM54304のLGAパッケージは、低EMIで小型かつ薄型のソリューションを提供します。(画像提供:Monolithic Power Systems)

設計とレイアウトの考慮事項

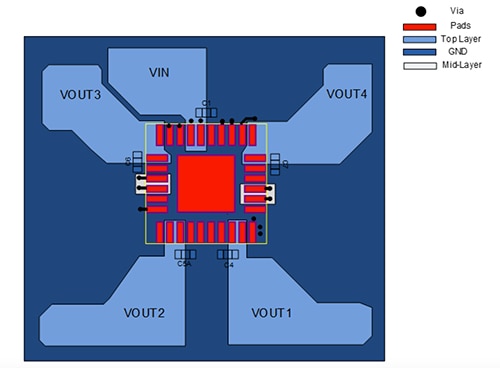

MPM54304はエッジに沿ったシンプルなピン配列で、レイアウトやプリント基板設計を容易にします。必要な外付け部品は5つだけで、トータルソリューションは小型でコンパクトです。LGAパッケージは、モジュールの下の領域のほとんどをカバーする強固なグランドプレーンを可能にし、渦電流ループを閉じ、EMIをさらに低減します。

この降圧コンバータは入力電流が不連続であり、DC入力電圧を維持しながらコンバータにAC電流を供給するためのコンデンサが必要です。設計者は、最高の性能を得るために、低等価直列抵抗(ESR)コンデンサを使用する必要があります。ESRが低く、温度係数が小さいため、X5RまたはX7R誘電体のセラミックコンデンサを推奨します。ほとんどのアプリケーションでは、22マイクロファラッド(μF)のコンデンサで十分です。

MPM54304を安定して動作させるためには、効率的なプリント基板レイアウトが重要です。熱性能を向上させるためには、4層プリント基板を推奨します(図7)。最良の結果を得るためには、次のガイドラインに従ってください。

- 電源ループをできるだけ小さくします

- PGNDに直接接続するには、大きなグランドプレーンを使用します。最下層がグランドプレーンの場合は、PGNDの近くにビアを追加します。

- GNDとVINの高電流経路には、短くて直接で幅の広いトレースがあることを確認します

- セラミック入力コンデンサをできるだけデバイスの近くに配置します

- 入力コンデンサとINはできるだけ短く、広くします

- VCCコンデンサをVCCおよびGNDピンにできるだけ近づけます

- VIN、VOUT、およびGNDを広い銅領域に接続して、熱性能と長期信頼性を向上させます

- 最上層で入力GND領域を他のGND領域と分離し、それらを内層と最下層で複数のビアを介して接続します

- 内層または最下層に統合されたGND領域があることを確認します

- 複数のビアを使用して電源プレーンを内層に接続します

図7:MPM54304クワッド出力電源モジュールを使用する場合は、4層のプリント基板レイアウトを推奨します。(画像提供:Monolithic Power Systems)

図7:MPM54304クワッド出力電源モジュールを使用する場合は、4層のプリント基板レイアウトを推奨します。(画像提供:Monolithic Power Systems)

結論

要求度の高いデータアプリケーションに対応するために処理アーキテクチャが進化するにつれ、設計者は、処理能力の向上と、同じサイズのフォームファクタや小型化するフォームファクタのエレクトロニクスをサポートできるマルチレール電源ソリューションを開発するという課題に直面しています。降圧DC/DCコンバータは、これらのシステムのための電源ソリューションを設計する上で重要なコンポーネントですが、実装が複雑になる可能性があります。

前述のように、設計者は、複数の電源レールとプログラム可能なシーケンスを備えた自己完結型の降圧DC/DCコンバータモジュールを使用することで、設計プロセスを簡素化し、市場投入までの時間を短縮することができます。また、これらの自己完結型モジュールを実現する新しい構造技術には、EMIの抑制、熱放散の改善、フットプリントサイズの縮小などの多くの性能上の利点があります。

お勧めの記事

免責条項:このウェブサイト上で、さまざまな著者および/またはフォーラム参加者によって表明された意見、信念や視点は、DigiKeyの意見、信念および視点またはDigiKeyの公式な方針を必ずしも反映するものではありません。