強誘電体メモリを使用した車載用アプリケーションの信頼性強化

DigiKeyの北米担当編集者の提供

2019-06-28

不揮発性メモリ(NVM)は、ほぼあらゆる組み込みシステム設計において重要な役割を果たしていますが、多くの設計では不揮発性メモリの要件がデータ書き込み/アクセス速度、データ保持、低電力の面でますます厳しくなりつつあります。この傾向は、設計者がミッションクリティカルな先進運転支援システム(ADAS)などきわめて高度な機能の組み込みを模索する、車載用アプリケーションで特に顕著に見られます。

これらのシステムの安全で信頼性の高い動作を保証するために、設計者は先進的な強誘電体ランダムアクセスメモリ(F-RAM)を詳細に検討する必要があるでしょう。F-RAMは、信頼性が高く低電力で現在のNVMソリューションよりも高速な、低電力車載グレードのNVMオプションとして活用できます。

この記事では、F-RAMテクノロジの主な特性について説明し、Cypress Semiconductorの2つのF-RAMソリューションを使用してADASの信頼性を高め、ADASでの利用を踏まえた他のミッションクリティカルなアプリケーションでのF-RAMの活用方法について説明します。

車載用NVMの要件

自動車の安全性を確保するアプリケーションは、高分解能で高速な更新レートを備えた高機能センサを組み込む産業界のトレンドを象徴する分野でもあります。ADAS、電子制御ユニット(ECU)、イベントデータレコーダ(EDR)などの車載用サブシステムは、さまざまなセンサで収集する各種の大量のデータに基づいて進化し続けています。データを喪失したり、ましてやデータへのアクセス速度が低下したりすれば、システムの安全性、車両、搭乗者を危険にさらす原因になります。

たとえばADASの設計では、電気的に消去可能な読み取り専用プログラム可能メモリ(EEPROM)への書き込みに時間がかかると、感知した危険を避けるよう設計された自動操縦に致命的な遅れが生じる可能性があります。またEDRの設計では、車の事故で電源が故障した場合、書き込みが遅いと重要なセンサデータを失う原因にもなり、事故の根本原因の究明に必要なデータそのものが消滅する可能性があります。

F-RAM NVMの特性

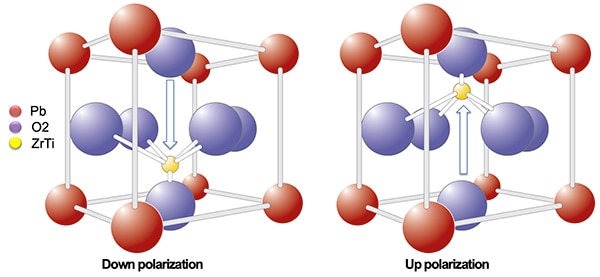

F-RAMテクノロジに基づくメモリデバイスは、有効なNVMソリューションとして、増大する需要と信頼性の高いデータストレージや高速アクセスなどの性能要件を満たします。このデバイスは、チタン酸ジルコン酸鉛(Pb[ZrxTi1−x]O3)、いわゆるPZTから製造されています。PZTには独特の特性があり、PZT結晶内に組み込まれている金属空格子点(陽イオン)が、電界印加の方向に沿って、上方または下方の2つの可能な極性化状態のいずれかに達します(図1)。

図1:F-RAMテクノロジは、電界を受けたときPZT素材に現れる2つの等しく安定したエネルギー状態を利用します。(画像提供:Cypress Semiconductor)

図1:F-RAMテクノロジは、電界を受けたときPZT素材に現れる2つの等しく安定したエネルギー状態を利用します。(画像提供:Cypress Semiconductor)

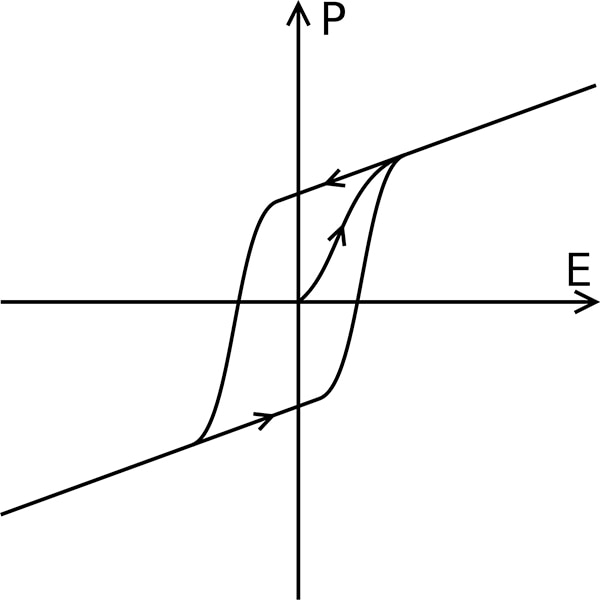

どちらも等しい低エネルギー状態なので、電界がなくなっても陽イオンは直近の極性化状態に固定された状態が続きます(図2)。正または負の電界を印加すると、陽イオンは再び、強磁性材料に見られるものと類似の特徴的なヒステリシスループに従って、該当する極性化状態にすばやく移行します。

図2:PZT材料は、印加電界に反応して2つの安定した極性化状態間で切り替わるとき、特徴的なヒステリシスループに従います。(画像提供:WikiMedia Commons/ CC-BY-SA-3.0)

図2:PZT材料は、印加電界に反応して2つの安定した極性化状態間で切り替わるとき、特徴的なヒステリシスループに従います。(画像提供:WikiMedia Commons/ CC-BY-SA-3.0)

F-RAMテクノロジの特性は、同テクノロジにより作成されるNVMデバイスの多くの利点に直結するものです。両方のPZTエネルギー状態は等しく安定しているので、陽イオンは数十年または場合により数世紀に及び最後の位置に留まり、かつてないデータ保持率をPZTベースのF-RAM NVMデバイスにもたらします。また、この技術は他のNVMテクノロジに見られる電荷蓄積メカニズムではなく陽イオン位置に基づくので、F-RAMデバイスは本質的に放射線耐性があり、電離放射線によるSEU(シングルイベントアップセット)に耐性があります。

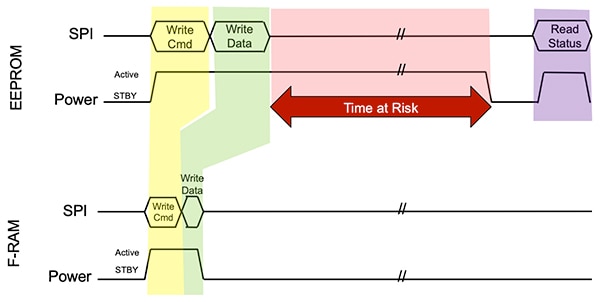

F-RAMテクノロジは、データの長期保持の長所を持つ以外にも、NVMデバイスの動的性能を向上させます。状態遷移がきわめて速く、エネルギーをほぼ必要とせず、ミッションクリティカルなアプリケーションでEEPROMまたはフラッシュメモリを使用する際の根本的な制約を克服します。EEPROMやフラッシュデバイスでは、その比較的遅い書き込みサイクル中に、データバッファリングに付随して大幅な「ソーク時間」が必要です。このような書き込みサイクルの余分な遅延は、最終的な読み取り状態チェックによって処理が完了する前に電源不具合が生じた場合、データがリスクにさらされ完全喪失の原因となる時間につながります(図3)。

図3:EEPROMまたはフラッシュ書き込み処理中のソーク時間(赤いハイライト)延長が必要になると、F-RAMデバイスに比べてデータがリスクにさらされ続ける時間が増えます。(画像提供:Cypress Semiconductor)

図3:EEPROMまたはフラッシュ書き込み処理中のソーク時間(赤いハイライト)延長が必要になると、F-RAMデバイスに比べてデータがリスクにさらされ続ける時間が増えます。(画像提供:Cypress Semiconductor)

EEPROMやフラッシュメモリの書き込みサイクルが遅いことを考慮して、電源障害の影響を軽減しようとする開発者は、適切な電圧レギュレータとともに大容量のコンデンサまたはバッテリを追加して、書き込み処理を完了できるだけの時間にわたってNVMの電源電圧を維持する必要がありました。対照的に、Cypress SemiconductorのExcelon-AutoデバイスのようなF-RAMでは、書き込み処理中にバス速度で動作するため、重要なデータの損失が大幅に減り、設計に補助電源を考慮する必要がなくなります。

車載グレードのF-RAMデバイス

シリアルEEPROMやシリアルフラッシュメモリと機能的に同じExcelon™-Auto F-RAMデバイスは、信頼性の高い高性能なNVMを要するミッションクリティカルなアプリケーションの要件を満たすように設計されています。車載用システムの設計者は、1.71~1.89V電源用のCY15V102QN、または1.8~3.6V電源用のCY15B102QNから選択して、これらのAEC-Q100認定デバイスを他のメモリタイプの代わりに使用することができます。いずれも2Mビット(メガビット)デバイスで、256Kビット x 8として論理的に構成されています。

-40°C~+125°Cの動作温度範囲におけるExcelon F-RAMのデータ保持率は、他のNVMテクノロジで可能なデータ保持率を大幅に超えています。たとえば、CY15x102QNは、85°Cの動作温度で推定121年間データを保持できます。データ保持は温度に反比例するので、一般的なエンジン温度の上限、たとえば95°Cで動作する場合、F-RAMのデータ保持率は推定で35年です。

信頼性に関しては、F-RAMは1013の読み取り/書き込みサイクル耐久性を有しており、これは標準的なEEPROMまたはフラッシュメモリよりも7桁ほど優れています。このため、F-RAMデバイスを使用する開発者は、他のNVMテクノロジに付随する書き込みサイクルの制約を考慮して書き込みを複数セクタに分散させるウェアレベリングなどの技術を実装する必要がありません。

F-RAMによる簡易な設計

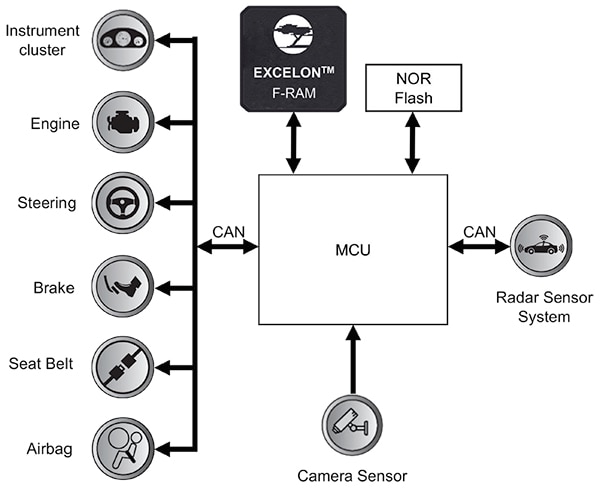

一般的な設計では、開発者はこれらのデバイスを使用して、NORフラッシュなど他のタイプのNVMデバイスを直接置き換えるか補完できます。たとえばADAS設計では、開発者はファームウェアの保存に使用されるNORフラッシュと、ADASアプリケーションへの入力を実現する多くの車載用サブシステムから複数のデータストリームを確実に処理できるExcelon F-RAMを組み合わせることができます(図4)。

図4:車載用ADASの開発者は、重要なデータを保存するExcelon F-RAMデバイスと、マイクロコントローラ(MCU)ベースの設計でファームウェアまたは設定データの保存によく使われるNORフラッシュデバイスを組み合わせることができます。(画像提供:Cypress Semiconductor)

図4:車載用ADASの開発者は、重要なデータを保存するExcelon F-RAMデバイスと、マイクロコントローラ(MCU)ベースの設計でファームウェアまたは設定データの保存によく使われるNORフラッシュデバイスを組み合わせることができます。(画像提供:Cypress Semiconductor)

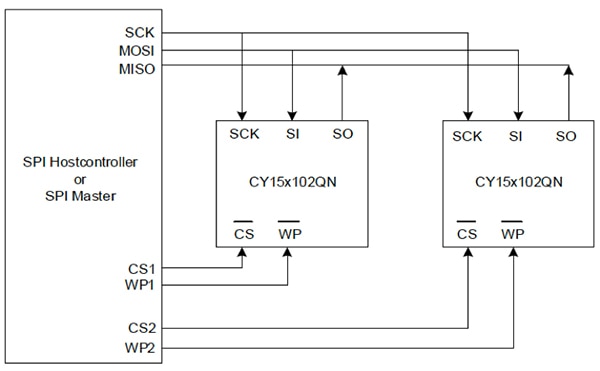

開発者は、Excelon F-RAMをホストプロセッサのシリアルペリフェラルインターフェース(SPI)バスに接続するだけで、同デバイスを簡単に設計に落とし込むことができます。SPIスレーブデバイスとして動作するように設計されたCY15x102QN F-RAMは、最大50MHz(メガヘルツ)までのSPIクロックレートをサポートできます。標準的なハードウェア構成では、F-RAMのシリアルイン(SI)とシリアルアウト(SO)をそれぞれSPIマスターのマスターアウトスレーブイン(MOSI)ラインとマスターインスレーブアウト(MISO)ラインに接続します。それぞれのシリアルクロック(SCK)ラインとチップセレクト(/CS)ラインへの接続によって、ハードウェアインターフェースが完成します。開発者は複数のデバイスを組み合わせてホストのSPIバスを共有できます(図5)。

図5:開発者は共有SPIバスを使用してホストプロセッサを1つ以上のCY15x102QN F-RAMに接続できます。(画像提供:Cypress Semiconductor)

図5:開発者は共有SPIバスを使用してホストプロセッサを1つ以上のCY15x102QN F-RAMに接続できます。(画像提供:Cypress Semiconductor)

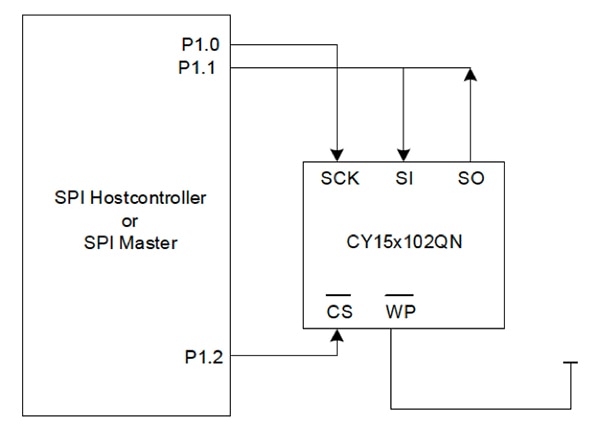

SPI機能を持たないMCUでは、CY15x102QNデバイスは、マイクロコントローラの汎用IO(GPIO)を使用してF-RAMに接続することでSPIハードウェアインターフェースをエミュレートするシンプルな方法をサポートします。開発者は、F-RAMのSIとSOのデータラインに同じピンを使用することで、3つのGPIOのみを使用してこのインターフェースを実装できます(図6)。

図6:ネイティブSPI機能なしのマイクロコントローラでは、開発者はマイクロコントローラの汎用IOを使用するだけで、SPIプロトコルをエミュレートしてCY15x102QNシリアルF-RAMにアクセスできます。(画像提供:Cypress Semiconductor)

図6:ネイティブSPI機能なしのマイクロコントローラでは、開発者はマイクロコントローラの汎用IOを使用するだけで、SPIプロトコルをエミュレートしてCY15x102QNシリアルF-RAMにアクセスできます。(画像提供:Cypress Semiconductor)

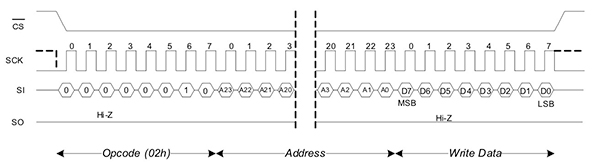

標準SPIプロトコルでは、マスターは/CSをローにすることでトランザクションを開始します。/CSがローになった後、F-RAMは次のバイトをオペコードとして解釈します。たとえば書き込み処理は、3バイトのアドレスとデータバイトによってSPI標準書き込みオペコード(02h)に続きます(図7)。

図7:CypressのCY15x102QN F-RAMデバイスが標準SPIオペコードとプロトコルをサポートすることで、開発者は書き込みオペコード(02h)、アドレス、データを順に送信して、ゼロ遅延書き込みを簡単に実行できます。(画像提供:Cypress Semiconductor)

図7:CypressのCY15x102QN F-RAMデバイスが標準SPIオペコードとプロトコルをサポートすることで、開発者は書き込みオペコード(02h)、アドレス、データを順に送信して、ゼロ遅延書き込みを簡単に実行できます。(画像提供:Cypress Semiconductor)

2MビットCY15x102QN F-RAMでは、アドレスは3バイトシーケンスで、上位6ビットは無視されます。将来、より大容量のF-RAMデバイスに容易に移行できるように、Cypressはこれら上位6ビットを0に設定することを推奨しています。

読み取り処理も同じプロトコルに従います。標準の読み取りオペコード(03h)とアドレスを受信すると、F-RAMデバイスはSO上でデータバイトを順次送信し、/CSがローのままでクロック信号が持続する間に、メモリアドレスを自動でインクリメントします。これにより開発者は、/CSをローに維持し必要数のデータバイトを読み取るまでSCKクロック信号を発し続けるだけで、一括読み取りを実行できます。

CY15x102QN F-RAMは、シリアルフラッシュメモリと互換性のある高速読み取り機能もサポートします。高速読み取りオペコード(0Bh)とアドレスに続き、SPIホストはダミーバイトを送信してフラッシュ読み出しレイテンシをエミュレートします。ダミーバイトを受信すると、F-RAMは要求されたデータを返します。高速読み取り処理では、標準読み取りと同じメカニズムを使用して一括読み取りも実行できます。

書き込み保護

SPIインターフェース制御ロジックとともに、CY15x102QN F-RAMはデバイスを識別しF-RAMアレイを書き込み保護するためのメカニズムも備えています。

開発者は、CY15x102QNデバイスの読み取り専用の一意のIDやデバイスIDにアクセスするためのSPIオペコードを発行できます。このオペコードには、メーカー、メモリ密度、パーツリビジョンなどの情報が含まれています。また、8バイトの読み書きシリアル番号レジスタを設定することで、F-RAMを特定のシステムまたは構成に関連付けることもできます。

F-RAM保護のために、デバイスにはソフトウェアとハードウェアの両メカニズムが含まれています。製造中のデータ保護のために、標準のリフローはんだ付け3サイクルまでデータ整合性を維持するように設計された、専用の256バイト特別セクタがあります。通常動作時の保護用には、デバイスはライトイネーブルラッチ(WEL)を使用してF-RAMアレイを意図しない書き込みから保護します。電源投入時にはWELはデフォルトでクリアされ、開発者は書き込み処理を実行する前にライトイネーブル(WREN)オペコード(06h)を発行する必要があります。

デバイスのステータスレジスタでは、ブロック保護(BP)ビット、BP0とBP1のペアを使用することで、開発者は全アドレス範囲(BP1=1、BP0=1)、メモリの上位半分(BP1=1、BP0=0)、またはメモリの上位4分の1のみ(BP1=0、BP0=1)を保護できます。

開発者は、ハードウェア書き込み保護ピン(/WP)を使用して、通常動作中にソフトウェアがBPビットを変更するのを防止できます。ここでは、ステータスレジスタでライトプロテクトイネーブル(WPEN)ビットを設定し、/WPピンをローにしてステータスレジスタをロックします。

電源管理

通常の動作では、F-RAMテクノロジ固有のエネルギー効率により、最大50MHzのクロックレートの動作では、CY15V102QN(VDD 1.71~1.89V)の標準的な消費電流はわずか5.0mA(ミリアンペア)です。クロック周波数を下げることでさらなる省電力が可能で、CY15V102QNでは1MHzであれば消費電流を約0.4mAにまで下げることができます。CY15B102QN(VDD 1.8~3.6V)の消費電流はわずかながら高く、50MHzで6.0mA、1MHzで0.5mAとなります。

非アクティビティの状態が長い場合は、SPIオペコードを使用してCY15x102QNデバイスを3つの低電力モードに設定することで、消費電力を大幅に削減できます。

- スタンバイモード。このモードでの標準的な消費電流はCY15V102QNが2.7μA(マイクロアンペア)、CY15B102QNが3.2μAとなります。

- ディープパワーダウンモード。このモードでの消費電流はCY15V102QNが1.1μA、CY15B102QNが1.3μAとなります。

- ハイバネートモード。2つのいずれのデバイスでも消費電流は0.1μAとなります。

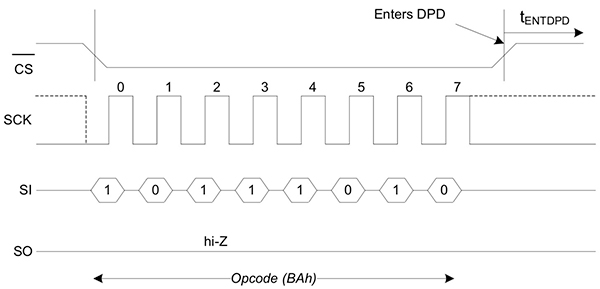

CY15x102QNデバイスは、SPIホストがオペコードシーケンスの最後に/CSをハイに設定するときは、常に自動でスタンバイモードに切り替わります。デバイスをディープパワーダウンまたはハイバネートモードに切り替えるために、SPIホストはSPIオペコードプロトコルを使用します。具体的には、SPIホストは最初に/CSをローに設定し、次にディープパワーダウン(BAh)またはハイバネートモード(B9h)用の特別なオペコードを送信し、最後に/CSをハイに設定することで、2つの最低電力モードのいずれかに切り替えます(図8)。

図8:CY15x102QN F-RAMデバイスはオペコードシーケンスの後に自動でスタンバイモードに入る一方、通常のSPIオペコード手順を使用することでデバイスをディープパワーダウン(DPD)モードなどのより低消費電力のモードにできます。(画像提供:Cypress Semiconductor)

図8:CY15x102QN F-RAMデバイスはオペコードシーケンスの後に自動でスタンバイモードに入る一方、通常のSPIオペコード手順を使用することでデバイスをディープパワーダウン(DPD)モードなどのより低消費電力のモードにできます。(画像提供:Cypress Semiconductor)

SPIホストが、適切な低電力オペコードの送信後に/CSをハイに設定すると、CY15x102QN F-RAMは約3μs以内に要求された低電力モードに入ります。

/CSがローになり次のオペコードシーケンスが開始されると、Cypress F-RAMはスタンバイモードから直ちにアクティブモードに復帰します。/CSがローになると、F-RAMはディープパワーダウンまたはハイバネートモードからでもアクティブモードに復帰しますが、ディープパワーダウンモードでは約10μs、ハイバネートモードからは450μsの短い遅延があります。

結論

信頼性が高く、高速、低電力、高性能なNVMの必要性は、多様化するセンサからのデータに依存する幅広いアプリケーションでますます重視されつつあります。車載用ADASアプリケーションなどのミッションクリティカルな領域では、データ喪失が、車両と搭乗者を保護するために設計された安全機構の大幅なレベル低下の原因になります。

Cypress SemiconductorのF-RAMデバイスを使用することで、開発者は、性能や低電力の要件を犠牲にせずに、重要なデータを何十年にもわたり確実に保存できるNVMを簡単に追加できます。

免責条項:このウェブサイト上で、さまざまな著者および/またはフォーラム参加者によって表明された意見、信念や視点は、DigiKeyの意見、信念および視点またはDigiKeyの公式な方針を必ずしも反映するものではありません。