ダイレクトデジタルシンセサイザ(DDS)の基礎とそれらの選定および使用方法

DigiKeyの北米担当編集者の提供

2019-03-20

ワイヤレスデバイスが増えるにつれて、設計者はデータ転送速度、干渉緩和、コスト、フットプリント、および低消費電力に関するアプリケーション要件を満たすために、ますます複雑で多様な波形を使うようになってきています。こうした波形には、オンデマンドでチューニングでき、周波数と位相どちらも可変である、安定したRF信号源が必要です。同時に、信号源から高度の信号純度が提供される必要もあります。このような要件の組み合わせを満たすソリューションが、ダイレクトデジタルシンセサイザ(DDS)です。

DDSは、デジタル方式でアナログ波形を生成することで、デジタルのプログラマビリティと高度な統合性および低いコストを活かすことができます。さらに、DDSは、周波数または位相をほぼ瞬時に変更できるため、周波数偏移変調(FSK)拡散スペクトラムなど、高度なデジタル変調テクニック向けの主要信号源として使用できます。また、周波数ホッピングなどの干渉緩和テクニックも使用できます。その結果、DDS ICは高度な安定性および信号純度を提供しながら、急速に従来の位相ロックループ(PLL)およびその他のアナログRF信号源の代替として、または補完的な使用が増加しつつあります。

この記事では、DDSテクノロジの基礎をさらい、どのようにDDS ICを指定するかについて解説します。さらに、適切なDDS ICソリューションをいくつか紹介し、それらを効果的に適用する方法を示します。

ダイレクトデジタルシンセサイザの仕組み

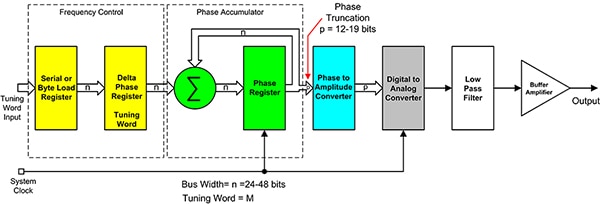

デジタル合成は、位相アキュムレータをベースにしており、位相アキュムレータで一連のデジタルステートが生成され、その値が線形に増加して数値ランプが形成されます。この信号は周期的に生成され、ゼロから2pラジアンまで、出力波形の瞬間的な位相を表します。これがルックアップテーブルにデジタル入力され、そこで数値ランプが正弦波に変換されます(図1)。最も一般的なDDS出力波形は正弦波ですが、ランプ、三角波、および矩形波も簡単に生成できます。

図1:ダイレクトデジタルシンセサイザは、波形の瞬間的な位相を生成する位相アキュムレータをベースとしています。ルックアップテーブルで位相から振幅への変換が行われ、それにデジタル/アナログコンバータが適用され、フィルタリングされた後、希望のアナログ出力が得られます。(画像提供:DigiKey)

位相/振幅ルックアップテーブルの出力がデジタル/アナログコンバータ(DAC)に送られ、アナログ波形に変換されます。通常、これは正弦波です。DACへの入力は一連のサンプリング値であるため、出力には量子化のステップが伴います。これらのステップにより、サンプルレートの倍数で周波数ドメインにスペクトル画像が発生します。これは望ましくありません。DACの後にあるローパスフィルタは、これらの不要なスペクトル応答を抑制します。

位相アキュムレータ

位相アキュムレータはモジュロNカウンタであり、2Nのデジタルステートがシステムクロック入力パルスの入力ごとにインクリメントしてきます。インクリメントのサイズは、アキュムレータの加算ステージに適用されるチューニングワードMの値に依存します。チューニングワードは、カウンターインクリメントのステップサイズを修正します。これにより、出力波形の周波数が決まります。

位相アキュムレータには一般に、24~48ビットがあります。24ビットでは、224、つまり16,777,216のステートがあります。この数字は、0~2pラジアンの間にある位相値の数、つまり獲得可能な位相インクリメントの数を表しています。24ビット位相アキュムレータの場合、位相分解能は3.74 E-7ラジアンです。大きな位相アキュムレータを使用するほど、位相インクリメントが細かくなります。

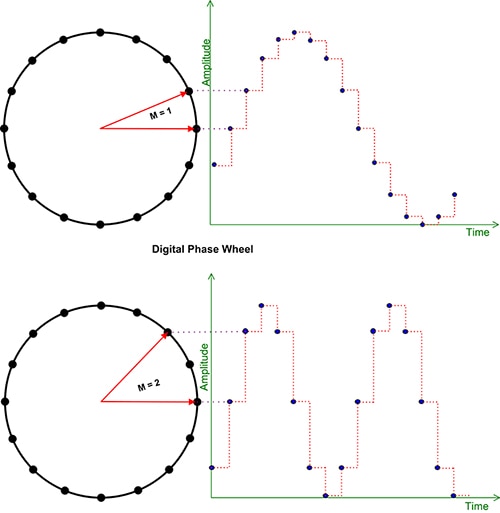

位相アキュムレータの動作を視覚化する方法の1つは、アキュムレータの動作を位相の輪として見ることです(図2)。

図2:位相の輪を使用してチューニングワードがDDSの出力周波数にどのように影響を及ぼすかを視覚化した、16ステート位相アキュムレータの簡略図。(画像提供:DigiKey)

アキュムレータのステートは周期的であり、円周上にあるものとして表現されています。円周上の点は、アキュムレータのすべての位相ステートを表しています。この例では、話を簡単にするために、アキュムレータには16ステートがあります。上段の図のように、チューニングワードが1と等しい場合には、各クロックのステップインクリメントは1で、周期を1周する間にすべてのステートが選択されます。

位相の輪の右側に描かれているのが、各ステートのアナログ出力です。これは量子化デバイスであるため、クロックによって位相の輪が次のステートにすすむまで、アナログ出力では現在のステートが保持されます。出力の波形は、16個の値を含む、量子化された正弦波の単一の周期で構成されます。

下段の図では、チューニングワードが2に設定されています。この設定では、位相の輪の1つおきのステートが選択されます。この場合、アナログ出力は、2つの周期で構成されます。それぞれのサイクルに8つの振幅があり、合計で16個のステートが提供されます。チューニングワードを2に設定することにより、出力周波数は前に取得された値の2倍になります。

DDSの出力周波数は、チューニングワードの値によって設定され、チューニングワードの値に比例して増加します。サンプルレートはシステムクロックレートで固定されたままであり、出力サンプル間の時間は一定です。出力周波数はチューニングワードのインクリメントに依存します。したがって、チューニングワードの値が大きくなると各出力周期のステップ数が減少し、これにより、周波数が高くなります。チューニングワードは、周期あたり2つのサンプルになるまで増やせます。この場合、DDS出力はナイキスト周波数、つまりシステムクロックレートの半分になります。一般に、DDSは、常にナイキスト周波数よりも低い出力周波数になるよう、設計で制限されています。

システムクロック周波数の他、DDSの出力周波数は、チューニングワードの値、およびアキュムレータの長さにも依存します。これは、式1で表現されます。

![]() 式1

式1

式の要素の意味は次のとおりです。

foutは、DDSの出力周波数

Mは、チューニングワードの値

fcは、システムクロック周波数

Nは、位相アキュムレータの長さ

位相アキュムレータの出力、つまり出力波形の瞬間的な位相を使用して、位相/振幅コンバータが駆動されます。位相/振幅コンバータによってデジタルワードが出力され、その値が、入力された位相の正弦波形の振幅となります。

位相/振幅コンバータの駆動に使用されるビット数は、位相アキュムレータに使用されるビット数よりも少ないことに注意してください。これは位相トランケーションと呼ばれ、位相アキュムレータ後のデジタルステージのダイエリアと消費電力を減らすために使用されます。これにより、トランケーションスプリアスと呼ばれるスプリアススペクトル成分が発生しますが、慎重に設計することで抑制できます。

出力ローパスフィルタを使用する理由

図2に示す波形は階段状であるため、高調波を多く含んでいます。その結果、ローパスフィルタを使用して、これらのスペクトル高調波、およびDDS内のその他の処理によって発生するその他のスプリアス周波数応答を除去する必要があります。

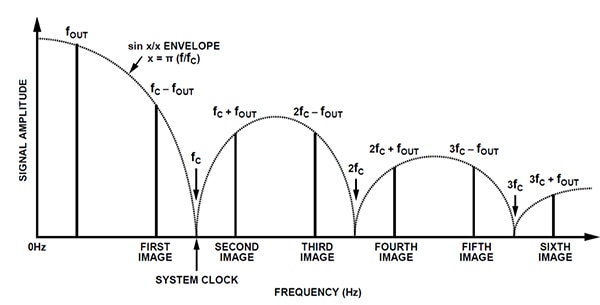

例として、fcでクロックされ、出力周波数がfc/2未満のデバイスのDDS出力スペクトルを図3に示します。この出力スペクトルは、出力スペクトルラインfoutを、クロック周波数の上下の画像周波数および3番目までとそれ以後のすべての高調波とともに示しています。

図3:クロックの第3高調波までの出力周波数成分を示す、システムクロック周波数fcと出力周波数foutを記載したDDSのスペクトルビュー。(画像提供:Analog Devices)

DDS出力周波数レンジは、0Hzからナイキスト周波数fc/2までです。sin(x)/xシェーピングは、図2に示すように、時間ドメインで量子化された信号によるものです。sin(x)/x関数のゼロは、クロック周波数およびすべての高調波で発生します。出力レンジにおいて振幅をさらにフラットにするために、振幅修正を適用してsin(x)/xシェーピングを打ち消すことができます。

DDSの周波数レンジを超えると正確に遮断するローパスフィルタが適用され、ナイキストを超えるスペクトル成分の振幅が大幅に削減されます。DDS周波数レンジがナイキスト周波数まで拡張された場合、このフィルタは、クロック周波数に関するより低い画像周波数を除外するために、無限の急峻カットオフスロープを必要とします。これは、ナイキスト周波数と重なります。これが、DDS周波数レンジがナイキスト周波数まで拡張されることはほとんどない理由の1つです。

市販のDDS ICを使用した設計

DDSを選定および使用するにあたって考慮すべきことはたくさんあります。まず、アプリケーションに必要な機能です。たとえば、必要な周波数レンジ、振幅およびオフセットレンジ、波形、分解能、および変調機能などです。信号純度は、一般に、信号源を選択する際のファクターです。スプリアスフリーダイナミックレンジ(SFDR)、全高調波歪み(THD)、および位相ノイズ、また、特にモバイルの用途では、消費電力も主な仕様です。

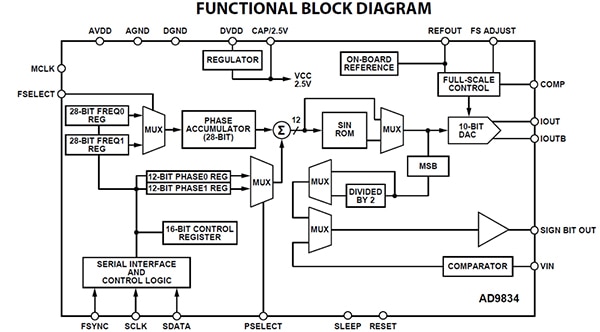

低消費電力DDSのよい例が、Analog DevicesのAD9834BRUZ-REEL7(図4)です。このデバイスは、3線式シリアルインターフェースによって制御され、消費電力は3Vの供給からわずか20ミリワット(mW)です。このデバイスは、正弦波、ランプ波、および矩形波関数を出力し、図ではデジタルクロック入力MCLKとして表示されている最大クロック周波数50メガヘルツ(MHz)を備えています。前出のナイキストの説明に基づいて、このクロック周波数で出力できる波形は最大25MHzです。

図4:Analog DevicesのAD9834低消費電力DDSの内部機能図。このデバイスの消費電力は、3Vの供給から20mWであり、最大25MHzの正弦波、ランプ波、および矩形波関数を提供できます。(画像提供:Analog Devices)

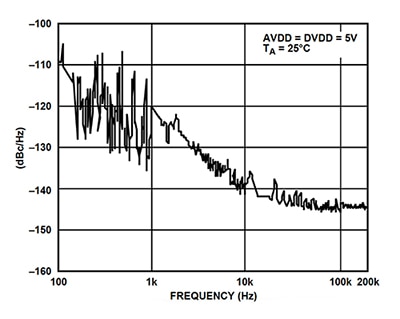

この位相アキュムレータは28ビット長であり、クロック周波数50MHzで周波数分解能0.186Hzを実現します。また、位相ノイズは、MCLK入力の質にも依存し、キャリヤからのオフセットの関数として示されます(図5)。AD9834の例では、FOUTが2MHzおよびMCLKが50MHzで、キャリヤからのオフセットが1kHzの時に、位相ノイズは-120dBc/Hzになります。

図5:位相ノイズはMCLKの質に依存し、FOUTが2MHzおよびMCLKが50MHzで、キャリヤからのオフセットが1kHzの時に-120dBc/Hzになります。(画像提供:Analog Devices)

内蔵DACの分解能は10ビットであり、ナローバンドSFDRは概して-78dBを上回っています。

AD9834は、2つの周波数および位相レジスタを内蔵しており、周波数および位相どちらの変調にも対応しているという特長があります。また、位相アキュムレータ出力を使用して正弦ROM(読み出し専用メモリ)をバイパスしてDACを駆動すれば、ランプ関数を生成することもできます。クロック生成のための矩形波を供給するために、出力ピンで符号ビットが利用できます。

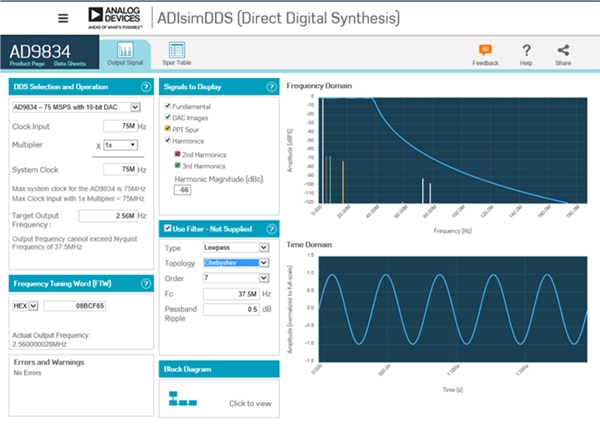

設計プロセスを支援するため、多くの場合、ベンダーはタスクを簡略化するための優れたツールを提供しています。AD9834 DDSは、Analog DevicesのADIsimDDSに対応しており、設計者はこのオンライン対話型設計ツールを使用して、出力周波数、チューニングワード、および参照クロックなど、さまざまな構成を評価できます(図6)。

図6:Analog DevicesのADIsimDDS対話型設計ツールを使用することで、設計者は、さまざまなDD構成およびフィルタオプションを試すことができます。(画像提供:Analog Devices)

ADIsimDDSプログラムでは、まず、特定のDDS製品を選択します(この例では、AD9834)。ユーザーがシステムクロック周波数と希望の出力周波数を入力すると、位相アキュムレータ用のチューニングワードがプログラムによって計算されます。周波数ドメインの表示には、出力信号、高調波、DAC画像、クロック高調波、およびクロック画像など、DDS出力のスペクトルが表示されます。フィルタシミュレータをDDS出力に適用すれば、さまざまなフィルタが出力スペクトルに及ぼす効果を確認できます。

より高度な性能および周波数を必要とする設計の場合、Analog DevicesのAD9952YSVZ-REEL7は最大クロック周波数400MHzを有し、最大200MHzの正弦波を生成できます。また、位相ノイズは低く、SFDRは160MHz(±100キロヘルツ(kHz)オフセット)AOUTで80dBを上回ります。AD9834と直接比較すると、そのナローバンドSFDRは概して20MHzで-70dBです。ただし、これはもちろん周波数に依存します。

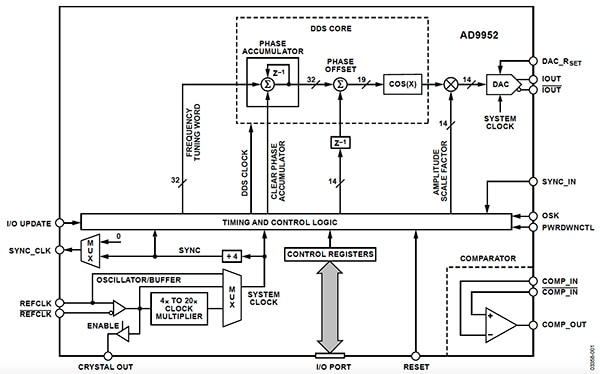

AD9952では、MCLK入力を使用しません。代わりに、PLL乗算器を備えたクロック発振器が内蔵されています。PLL乗算器では、単一の外部水晶振動子を使用して4~20倍の係数でクロックを乗算できます(図7)。独自のシステムクロック(最大400MSPS)を内蔵していることで、このDDSは、1kHzオフセットで-120dBc/Hz以下の低位相ノイズを実現できます。

図7:AD9952では、外部水晶振動子の入力を使用して、独自の内部システムクロックを生成することで、位相ノイズの低下など、性能アップに必要な状況をより適切に制御できます。(画像提供:Analog Devices)

また、AD9952は、32ビットの位相アキュムレータ精度および14ビットDACを特長としています。このDDSは、シリアルインターフェース経由で制御されます。

より広い周波数レンジが必要な場合には、Analog DevicesのAD9957BSVZ-REELを使用できます。これは、最大1ギガヘルツ(GHz)のクロックレートおよび出力周波数400MHzに対応しており、高度な通信アプリケーションに適しています。32ビットの位相アキュムレータおよび14ビットの高速DACを使用することで、このデバイスは、直角位相変調器の役割を果たし、8つの位相/周波数レジスタによって制御される同相(I)および直角位相(Q)成分を生成します。これらは、出力で直角相違変調データストリームを生成するために使用されます。前述のsin(x)/xシェーピングを補完するために、オプションの逆SINC(sin(x)/x)フィルタを使用できます。

これらは、シンプルな信号生成タスクから複雑な信号生成タスクまでを扱う、市販されているDDS集積回路の3つの例です。

まとめ

ワイヤレスシステムの性能、サイズ、コスト、および消費電力を向上させようと常に努める設計者にとって、DDSは優れたオプションです。DDSは、デジタルの安定性、可変能力、および反復性を備えた信号生成を可能にし、複数の出力波形および高度な変調機能(周波数および位相ホッピングなど)を提供します。DDSが設計者によって使用される機会が増えたことから、ベンダーも、設計プロセスを短縮する高度なツールの使用によって、それらを簡単に選択および統合できるようにしようと努めています。

免責条項:このウェブサイト上で、さまざまな著者および/またはフォーラム参加者によって表明された意見、信念や視点は、DigiKeyの意見、信念および視点またはDigiKeyの公式な方針を必ずしも反映するものではありません。