I3Cを活用して、より速く、よりシンプルで、より柔軟なIC間通信を実現

DigiKeyの北米担当編集者の提供

2024-12-17

集積回路(IC)間通信用のオンボードシリアルインターフェースは、1980年代から利用されているInter-Integrated Circuit(I²C)とシリアルペリフェラルインターフェース(SPI)が主流です。これらのインターフェースは、低速センサやICをマイクロコントローラユニット(MCU)に接続し、基板内での短距離通信を行うために広く使用されています。しかし、デジタルシステムが高速化するにつれて、I²Cでは1メガビット/秒(Mbit/秒)、SPIでは10Mbit/秒という各インターフェースの標準的なデータレート制限がボトルネックとなっています。他にも、専用の割り込み線やチップイネーブル線などの追加の信号接続が必要となるため、それによって配線数が増えてバス接続が複雑になります。

Improved Inter-Integrated circuit(I3C)バスは、IC間通信のアップグレードを目的としています。高速なデータレート、優れた柔軟性、そして外部割り込みの代わりにインバンド割り込み(IBI)を備えた真の2線式インターフェースを提供します。

この記事では、I3Cインターフェースの特性と、I²CやSPIシリアルインターフェースのアップグレード版としてI3Cが優れている理由について説明します。また、典型的なMCU、ICスイッチ、センサデバイスを用いて、その応用例を紹介します。

組み込み通信バス

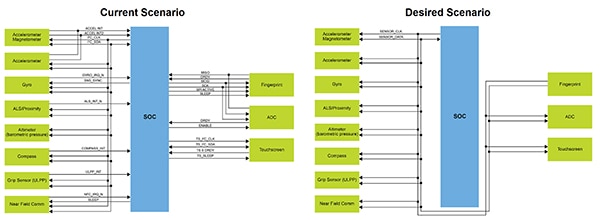

I²CやSPIなどの組み込みシリアル通信式相互接続は、基板内通信に長年採用されてきました。これらは主に、センサやユーザーインターフェースデバイスと、それらを制御するプロセッサ間の通信バスとして使用されます。一般的なシステムに搭載されるセンサの数は、携帯電話では10〜20個、自動車ではそれ以上に増えています。同時に、高速化、低消費電力化、配線数の削減という要求が高まるにつれ、設計者にとって通信要件はより困難なものとなっています。設計者は、割り込み線やイネーブル線によるプロセッサ制御を維持しながら、これらの要求を満たさなければなりません(図1)。

図1:組み込み通信は、高速化、低消費電力化、配線数の最小化に対応する必要があります。(画像提供:NXP Semiconductors)

図1:組み込み通信は、高速化、低消費電力化、配線数の最小化に対応する必要があります。(画像提供:NXP Semiconductors)

現在の技術では、センサやユーザー制御デバイスのインターフェースとして、2線式のI²Cまたは4線式のSPIインターフェースが使用されています。割り込み線、イネーブル線、その他の制御線は、クロック線やデータ線とは別であるため、インターフェースあたりの配線数が多くなります。

設計者は、これらの余分な配線を相互接続から排除し、クロック線やデータ線のみを使用して割り込みやイネーブルなどの操作をインバンドで処理する、より将来を見据えたインターフェースのアプローチを必要としています。さらに、このバスはより高速に動作し、電力損失を低減できなければなりません。

I3Cインターフェース

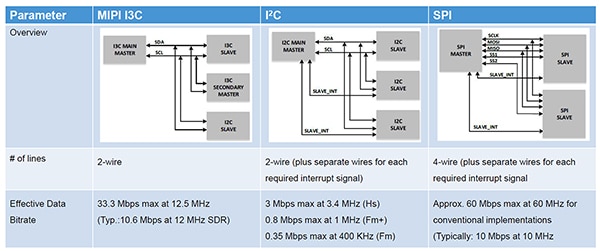

I3Cは、前述の要件に対応するため、Mobile Industry Processor Interface(MIPI)アライアンスによって開発されました。このインターフェースは、MIPI会員にはMIPI I3Cとして、非会員には機能を絞ったMIPI I3C Basicとして提供されます。従来のI²CやSPIインターフェースと同様に、I3Cもシリアル通信方式で、ピン数やコンポーネント間の信号経路数を最小限にするために、2本の配線を使用して実装されています。I3Cはシングルデータレート(SDR)モードで12.5MHzのクロックを使用し、最大12.5Mbit/秒のデータレートを実現します。より低い電力レベルで動作し、シンプルかつ柔軟な設計アーキテクチャを採用しています。

特筆すべき点として、I3C規格はI²Cシステムとの限定的な下位互換性を保持しており、既存のI²CデバイスをI3Cバスに接続することができます。一方で、I3C準拠デバイス間の通信では、バスを高速データレートに切り替えることも可能です。システム構成の比較を図2に示します。

図2:I3C、I²C、SPIインターフェースの基本構成を比較すると、I3Cの方が速度が向上し、配線がシンプルであることがわかります。(画像提供:NXP Semiconductors)

図2:I3C、I²C、SPIインターフェースの基本構成を比較すると、I3Cの方が速度が向上し、配線がシンプルであることがわかります。(画像提供:NXP Semiconductors)

4線式のSPIインターフェースはより高速な動作を可能にし、全二重通信をサポートします。一方、I²Cはクロック(SCL)線とデータ(SDA)線からなる2線式バスを使用し、半二重通信を行います。どちらも、割り込みやチップセレクトなどの制御機能をサポートするために追加の配線を必要とします。I3Cでは、I²CやSPIで使用される個別の割り込み線、イネーブル線、チップセレクト線を排除し、インターフェースに使用される配線数を2本に減らしています。この配線数の削減は、プロセッサに接続された10〜20個のセンサがそれぞれに数本の2次配線を必要とするシステムでは、大きな利点となります。割り込みやその他の制御線はIBIに置き換えられます。この方法では、ターゲットとなるセンサやデバイスは、そのアドレスをI3Cバスのアドレスヘッダにインプットすることで、プロセッサに割り込みを通知します。

I²CとI3Cのクロックレートの差は顕著です。I²Cは通常100キロヘルツ(kHz)、400kHz、または1メガヘルツ(MHz)で動作しますが、I3Cは12.5MHzで動作します。以前は、1MHzを超えるクロックレートではSPIが使用されていました。設計時には、クロックレートと配線数のどちらを優先すべきか選択を迫られていました。I3Cは、真の2線式トポロジを使用しながら、より高速なクロックレートとデータレートを提供することで、この状況を変えました。

オープンドレインやコレクタドライバよりも高速に切り替え可能なプッシュプル出力は、I3Cのクロックレート向上に大きく貢献しています。I²Cデバイスとの互換性を維持するため、I3Cはバスの状態に応じてオープンドレインとプッシュプルドライバを切り替えることができます。オープンドレインまたはコレクタ設計は、最初のアドレッシングまたは調停時に使用されます。このとき、I²CとI3Cの両デバイスが同時に線に接続されている可能性があります。通信が一方向で、I²Cデバイスが同時に通信する可能性のない場合に、I3Cはプッシュプルを使用します。

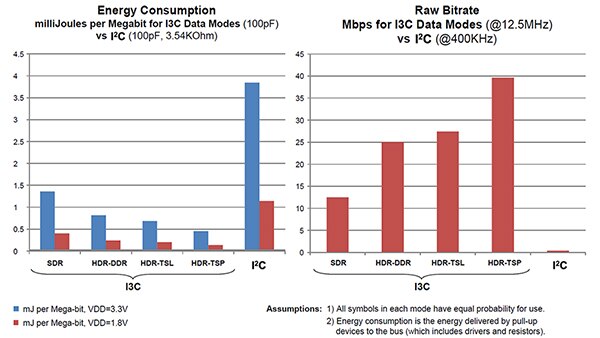

標準的なSDRに加えて、I3Cはいくつかのオプションのハイデータレート(HDR)モードをサポートしています。それらのHDRモードは同じクロックレートで動作しますが、より高いデータ密度で伝送されます。最初のHDRモードはHDRダブルデータレート(HDR-DDR)で、クロック信号の両エッジでデータをクロックし、約2倍のデータレートを提供します。クロックが12.5MHzの場合、DDRモードは20Mbit/秒の実効データレートを達成します。

HDRターナリーシンボルには2つのバージョンがあります。I3Cデバイス専用のHDRターナリーシンボル(HDR-TSP)と、I²CとI3Cの両デバイスを含むバス用のHDRターナリーシンボル(HDR-TSL)です。ターナリーシンボルモードは、SCLおよびSDA線にエンコードされた3ビット(ターナリー)シンボルを使用して、1クロックあたり3データビットを実現します。

HDRバルクトランスポート(HDR-BT)モードは、クワッド、デュアル、またはシングルのSDAデータ線を使用した通信をサポートすることで、最も高いデータ性能を提供します。この結果、同じクロックレートで、シングルデータレートのパフォーマンスが8倍、4倍、2倍になります。

このようなデータ転送速度の向上により、デバイスを短時間オンにすることが可能になり、バスの電力デューティサイクルが低下します。これにより、I²Cに比べて消費電力が削減されます(図3)。プルアップ抵抗は動作時に大きな電力を必要とするため、外部プルアップ抵抗を使用するオープンコレクタドライバからプッシュプルドライバに変更すると、消費電力をさらに削減できます。

図3:I3CはI²Cに比べてデータレートと消費電力が改善しています。(画像提供:NXP Semiconductors)

図3:I3CはI²Cに比べてデータレートと消費電力が改善しています。(画像提供:NXP Semiconductors)

アドレッシング

I²Cは、各バスデバイスに対して7ビットまたは10ビット長のスタティックアドレスを使用します。これに対して、I3Cでは7ビットのダイナミックアドレッシングに変更され、バスマスターがダイナミックアドレス割り当て(DAA)の際にデバイスアドレスを設定し、それをデバイスレジスタに格納します。I²C周辺機器の場合のようなスタティックアドレッシングは、I3Cでも使用できます。

ダイナミックアドレッシングにより、デバイスアドレスは後で変更することが可能です。これはホットジョインに対応しており、バスが動作している間でも新しいデバイスをバスに追加できます。I3Cバスに接続された新しいデバイスは、ホットジョイン要求を送信することによって、その存在をI3Cマスターに知らせます。マスターコントローラは要求を承認し、デバイスをバスに追加するためのアドレスを割り当てます。

IBI

I3Cは、I²Cのような専用割り込み線ではなく、IBIを使用する真の2線式バスです。IBIでは、ターゲットデバイスがSDA線をプルダウンすることによって、使用可能であることをマスターに知らせます。その後、マスターはSCL線のクロックをスタートさせ、ターゲットデバイスはそのアドレスをI3Cバスに送信し、コントローラに割り込みを通知します。

共通コマンドコード

共通コマンドコード(CCC)は標準化されたコマンドで、コントローラはすべてのI3Cデバイスに対して同時に送信(一般的なブロードキャスト)するか、特定のターゲットデバイスに対して送信できます。このコマンドはバス管理に関するものです。CCCプロトコルのフォーマットは、バス上のすべてのI3Cデバイスによって認識されるI3Cブロードキャストアドレスから始まります。バス上のI²Cデバイスは、この要求をアクノリッジしません。なぜなら、それはI²Cで予約されたアドレスであるためです。

各コマンドは8ビットの記述子IDフィールドを含み、その後にコマンドペイロードが続くこともあります。特定のデバイスに送信されるコマンドは、ペイロードの最初のバイトにデバイスアドレスを渡します。CCCには以下を含む40以上のコマンドがあります。

- 動的アドレス割り当ての入力(ENTDAA)

- 新しい動的アドレス割り当ての設定(SETNEWDA)

- イベントのイネーブル(ENEC)/イベントのディスエーブル(DISEC)

- 動的アドレス割り当てのリセット(RSTDAA)

- ハイデータレートモードの開始(ENTHDRx)

- デバイス特性レジスタの取得(GETDCR)

ベンダーには、独自のコマンドを実装するための専用のCCC IDの範囲が認められています。

エラーの検出と回復

I²Cとは異なり、I3Cにはエラー検出と回復のための仕組みが備わっています。ターゲットデバイスに対する6つのエラーおよび回復方法が義務付けられており、さらに1つの方法がオプションとして用意されています。マスター側のエラーに特化した追加のエラーおよび回復方法も用意されています。

I3C対応コンポーネント

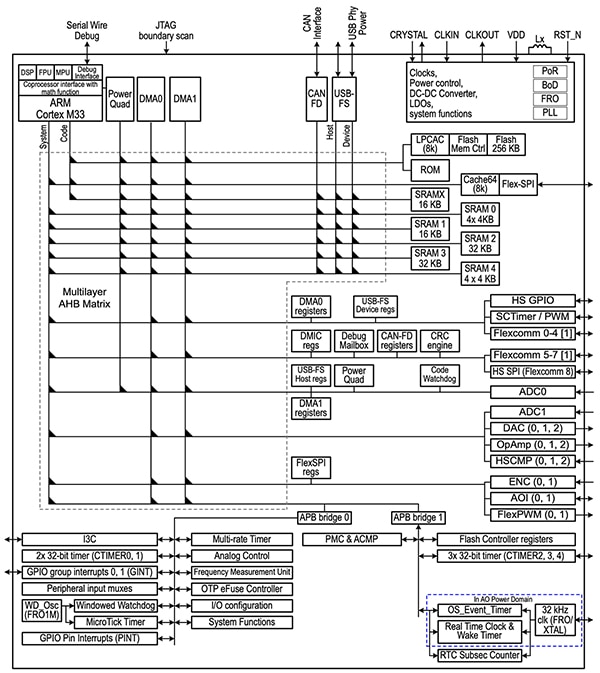

図2(左)が示すように、基本的なI3Cネットワークは、少なくとも1つのマスターコントローラと1つ以上のI3Cターゲットまたはスレーブで構成されます。メインマスターには、NXP SemiconductorsのLPC5534JHI48-00MPなどのMCUを使用できます(図4)。これは、32ビットのArm® Cortex®-M33 MCUで、128キロバイト(Kbyte)のSRAMと256Kbyteのフラッシュを備えています。Flexcommインターフェースにより、I3Cを含む8種類のシリアルインターフェースをサポートしています。

図4:LPC5534JHI48/00MP MCUは、I3Cインターフェースと7つのシリアルインターフェースを備えています。(画像提供:NXP Semiconductors)

図4:LPC5534JHI48/00MP MCUは、I3Cインターフェースと7つのシリアルインターフェースを備えています。(画像提供:NXP Semiconductors)

I3Cバスでは、スレーブとしてバスに導入されたセカンダリマスターを追加できます。I3Cは複数のマスターを持つことができますが、コントローラとして機能できるのは1つのみです。セカンダリマスターが登録されると、現在のマスターにステータスを要求することができ、現在のマスターが承認すれば、その制御は要求しているセカンダリマスターに引き渡されます。

NXPのP3T2030CUKAZは典型的なI3Cセンサです。この温度センサは、-40°C~+125°Cの温度を±2°Cの精度で12ビットのデジタル値に変換します。I²CとI3C SDRモードの両方のシリアルインターフェースを備えています。

より高度なセンサとしては、TDK InvenSenseのICM-42605 3軸微小電気機械システム(MEMS)ジャイロスコープおよび加速度計があります。レートジャイロとして、毎秒±15.2度~±2000度(°/秒)のスピンレートを測定します。加速度計としてのカバー範囲は±2~±15gです。動き、傾き、タップ、歩数(歩数計)を検出します。I3Cセンサとして、SDRモードでは12.5MHz、DDRモードでは25MHzで動作します。

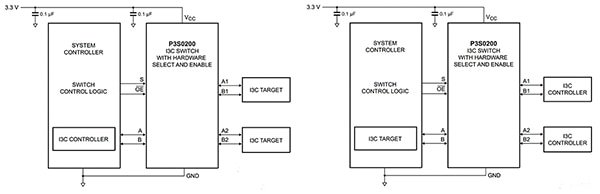

NXPのP3S0200GMX I3CスイッチなどのICは、I3Cコントローラと複数のターゲットデバイスセット間、または単一のターゲットと外部MCUが決定する複数のI3Cコントローラ間でI3Cバス信号をルーティングすることにより、I3Cバスを再構成できます(図5)。

図5:P3S0200GMX I3Cスイッチを使用すると、I3Cコントローラと複数のターゲットデバイスセット間、または単一のターゲットと複数のI3Cコントローラ間でI3Cバス信号をルーティングすることにより、I3Cバスを再構成できます。(画像提供:NXP Semiconductors)

図5:P3S0200GMX I3Cスイッチを使用すると、I3Cコントローラと複数のターゲットデバイスセット間、または単一のターゲットと複数のI3Cコントローラ間でI3Cバス信号をルーティングすることにより、I3Cバスを再構成できます。(画像提供:NXP Semiconductors)

2つのターゲットが同じアドレスを持ち、同じバス上に存在できない場合、2つのターゲットの切り替えが必要になることがあります。あるいは、1つのターゲットを2つのプロセスで共有する必要がある場合にも、2つのI3Cコントローラの切り替えが必要になることがあります。

まとめ

I3Cは、I²Cバスのデータレートを向上させ、配線数を減らし、バス制御に柔軟性を加えることでI²Cバスを拡張するシリアルインターフェースです。これは、従来のI²CおよびSPIインターフェースの有用性をさらに拡張した強化版です。

免責条項:このウェブサイト上で、さまざまな著者および/またはフォーラム参加者によって表明された意見、信念や視点は、DigiKeyの意見、信念および視点またはDigiKeyの公式な方針を必ずしも反映するものではありません。