セキュアかつコネクテッドのハードリアルタイムシステム向けのFPGA SoCの活用方法

DigiKeyの北米担当編集者の提供

2023-02-16

フィールドプログラマブルゲートアレイ(FPGA)、Linux対応RISC-Vマイクロコントローラユニット(MCU)サブシステム、先進のメモリアーキテクチャ、高性能通信インターフェースは、設計者にとって重要なツールです。特に、セキュアなコネクテッドシステム、セーフティクリティカルなシステム、人工知能(AI)や機械学習(ML)などの幅広いハードリアルタイム決定論的システムの設計者にとって重要です。

しかし、これらの多様な要素をセキュア、コネクテッド、および決定論的なシステムに統合することは、さまざまなシステム要素のための高速相互接続を展開することと同様に、困難で時間のかかる作業となります。設計者は、メモリ管理ユニット、メモリ保護ユニット、セキュアブート機能および、高速接続のためのギガビットクラスのトランシーバを含める必要があります。設計には、アクティブおよびスタティックな電源管理および突入電流の制御が必要になります。一部の設計では、0℃から+100℃の接合部温度(TJ)という拡張された商用温度範囲での動作が必要となり、産業環境でのシステムでは、-40℃から+100℃のTJで動作する必要があります。

設計者はこれらの課題に対処するため、スマート、コネクテッド、および決定論的なシステム向けに、低消費電力、熱効率、および防衛グレードのセキュリティを兼ね備えたFPGAシステムオンチップ(SoC)デバイスを利用することができます。

この記事では、そのようなFPGA SoCのアーキテクチャを確認し、コネクテッドおよび決定論的なシステムの効率的な設計をどのようにサポートするかを説明します。そして、EEMBC CoreMark-Pro処理能力対消費電力ベンチマークを、代表的なFPGA SoCのベンチマークパフォーマンスの見方とともに簡単に紹介します。また、セキュリティがFPGA SoCにどのように組み込まれているのかと、Microchip TechnologyのFPGA SoCおよび、設計プロセスを加速する開発プラットフォームについて詳しく解説します。最後に、さまざまな通信インターフェースや全地球航法衛星システム(GNSS)の測位機能を実装できるMikroElektronikaの拡張ボードを簡単に紹介します。

FPGAファブリックで構築されたSoC

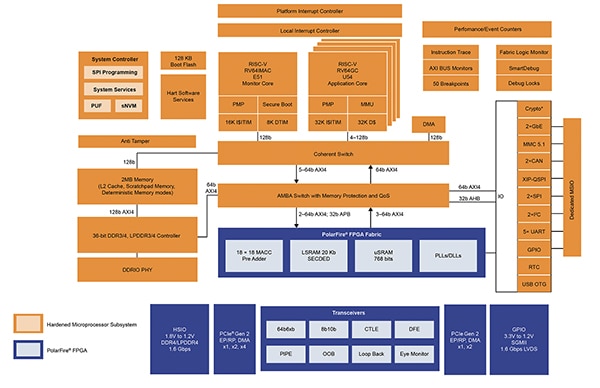

このSoCの「チップ」は、FPGAから、ハード化されたFPGAロジックで構築されたRISC-V MCUサブシステムまでのシステム要素を含むFPGAファブリックです。MCUサブシステムには、クアッドコアRISC-V MCUクラスタ、RISC-Vモニタコア、システムコントローラ、決定論的レベル2(L2)メモリサブシステムが含まれます。これらのSoCのFPGAには、最大460Kの論理素子、最大12.7Gbpsのトランシーバおよび、汎用I/O(GPIO)やペリフェラルコンポーネントインターコネクトエクスプレス(PCIe)2などの入出力(I/O)ブロックが搭載されています。全体的なアーキテクチャは、信頼性を重視して設計されています。また、全メモリのシングルエラー訂正/ダブルエラー検出(SECDED)、差動電力解析(DPA)、物理メモリ保護、128Kbitのフラッシュブートメモリを搭載しています(図1)。

図1:RISC-Vサブシステムを含むこのFPGA SoCの全要素は、FPGAファブリック上に実装されています。(画像提供:Microchip Technology)

図1:RISC-Vサブシステムを含むこのFPGA SoCの全要素は、FPGAファブリック上に実装されています。(画像提供:Microchip Technology)

Microchipは、RISC-Vシステムの実装をサポートするサードパーティ製ツールと設計リソースのMi-V(「マイファイブ」と発音)エコシステムを提供しています。これは、ハード化されたRISC-VコアやRISC-VソフトコアのRISC-V命令セットアーキテクチャ(ISA)の採用を加速するために構築されたものです。Mi-Vエコシステムの要素には、以下に対するアクセスが含まれます。

- 知的財産権(IP)ライセンス

- ハードウェア

- オペレーティングシステムとミドルウェア

- デバッガ、コンパイラ、設計サービス

FPGA SoCに搭載されたハード化されたRISC-V MCUには、パッシブなランタイム設定可能AXI(Advanced Extensible Interface)や命令トレースなど、複数のデバッグ機能が搭載されています。AXIにより、さまざまなメモリに書き込まれるデータ、あるいはメモリから読み出されるデータを監視し、書き込みや読み出しのタイミングを把握することができます。

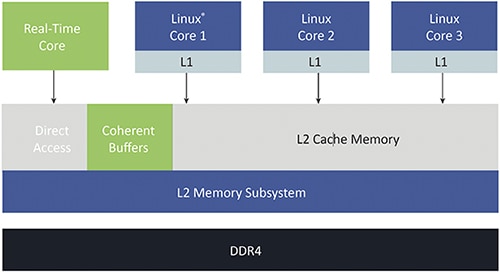

RISC-V MCUサブシステムは、5段のシングルイシューインオーダーパイプラインを採用しています。アウトオブオーダーアーキテクチャで問題となるSpectreやMeltdownのエクスプロイトに対する脆弱性はありません。5つのMCUはすべてメモリサブシステムと一貫性があり、決定論的非対称マルチプロセッシング(AMP)モードのリアルタイムシステムとLinuxの組み合わせをサポートしています。RISC-Vサブシステムの機能は、以下の通りです(図2)。

- Linuxとハードリアルタイム動作の実行

- L1とL2を決定論的メモリとして構成

- DDR4メモリサブシステム

- 分岐予測機能の無効化または有効化

- インオーダーパイプライン動作

図2:RISC-Vサブシステムには、複数のプロセッサとメモリ素子が含まれます。(画像提供:Microchip Technology)

図2:RISC-Vサブシステムには、複数のプロセッサとメモリ素子が含まれます。(画像提供:Microchip Technology)

より少ないエネルギーでより多くの処理

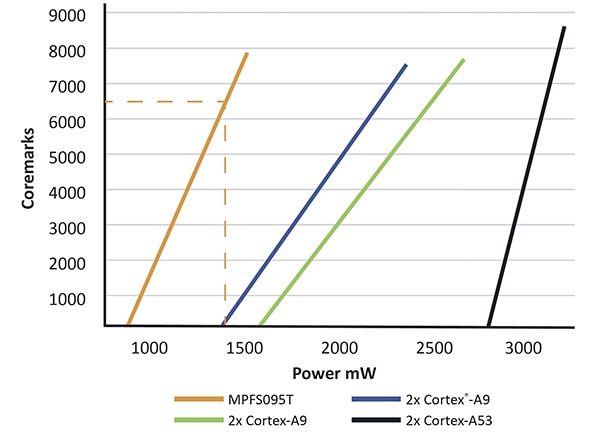

これらのFPGA SoCは、ハードでリアルタイムの処理に対応するといったシステム運用上の利点に加え、高いエネルギー効率を備えています。EEMBC CoreMark-PROベンチマークは、組み込みシステムにおけるMCUの効率と性能を比較するための業界標準です。これはハードウェアの性能をベンチマークするために特別に設計され、Dhrystoneベンチマークの代わりとなります。

CoreMark-PROのワークロードには、4つの浮動小数点ワークロードと5つの一般的な整数ワークロードに基づく多様なパフォーマンス特性、命令レベルの並列処理、メモリ使用率が含まれます。浮動小数点ワークロードには、LINPACKから派生した線形代数ルーチン、高速フーリエ変換、パターン評価用のニューラルネットアルゴリズム、改良されたリバモアループベンチマークなどがあります。JPEG圧縮、XMLパーサ、ZIP圧縮、256ビットセキュアハッシュアルゴリズム(SHA-256)が、整数ワークロードの基礎となっています。

これらのSoC FPGAのMPFSO95Tモデルは、MPFS095TL-FCSG536Eと同様に、1.3ワットで最大6500 Coremarkを実現します(図3参照)。

図3:MPFS095T FPGA SoC(オレンジ線)は、1.3ワットで6500 Coremarkを実現しました。(画像提供:Microchip Technology)

図3:MPFS095T FPGA SoC(オレンジ線)は、1.3ワットで6500 Coremarkを実現しました。(画像提供:Microchip Technology)

セキュリティへの配慮

これらのFPGA SoCのセーフティクリティカルおよびハードリアルタイムアプリケーションでは、高いエネルギー効率と強力な処理能力に加えて、強力なセキュリティが要求されます。これらのFPGA SoCの基本的なセキュリティ機能は、耐DPA(差動電力解析)ビットストリームプログラミング、真性乱数発生器(TRNG)、物理複製困難関数(PUF)です。また、標準およびユーザー定義のセキュアブート、マシン、スーパーバイザ、ユーザーモードなどマシンの権限状態に関連したメモリアクセス制限を提供する物理メモリ保護、 、MeltdownおよびSpectre攻撃への耐性も備えています。

セキュリティは、ウェハーテストやパッケージングにおけるハードウェアセキュリティモジュール(HSM)の使用など、セキュアなサプライチェーン管理から始まります。すべてのFPGA SoCに組み込まれた768バイトのデジタル署名付きx.509 FPGA証明書を使用することで、サプライチェーンの保証を高めています。

これらのFPGA SoCには、多数のオンチップ改ざん検知が搭載されており、安全で信頼性の高い動作を保証します。改ざんが検知された場合は、改ざんフラグを発行し、必要な対応をとることができます。利用可能な改ざん検知には、以下のようなものがあります。

- 電圧モニタ

- 温度センサ

- クロックグリッチおよびクロック周波数検知

- JTAGアクティブ検知

- メッシュアクティブ検知

さらに、256ビット先進暗号化標準(AES-256)対称ブロック暗号相関電力解析攻撃(CPA)対策、データの完全性を保証する暗号ダイジェスト機能、鍵ストレージ用PUF、FPGAファブリックと全オンチップメモリのゼロ化機能によってセキュリティを確保しています。

FPGA SoCの例

Microchip TechnologyのPolarFire FPGA SoCは、これらの機能と技術を統合し、複数のスピードグレード、温度定格、さまざまなパッケージサイズにより、25K~460Kの論理素子を持つ幅広いソリューションに対する設計者のニーズをサポートします。0℃~+100℃の拡張商用範囲、-40℃~+100℃の工業用範囲、-40℃~+125℃の車載用範囲、-55℃~+125℃の軍事用範囲という4つの温度グレード(いずれもTJ定格)が用意されています。

設計者は、標準的なスピードグレードのデバイスと、15%高速化した-1スピードグレードのデバイスから選択できます。これらのFPGA SoCは、低消費電力用に1.0ボルトで動作させることも、高性能用に1.05ボルトで動作させることも可能です。パッケージサイズは、11 x 11mm、16 x 16mm、19 x 19mmなど、さまざまなサイズがあります。

19 x 19 mmパッケージで、拡張商用温度動作、標準スピードグレード、254K論理素子を必要とするアプリケーションには、MPFS250T-FCVG484EESを利用できます。また、23Kの論理素子を必要とするシンプルなソリューションには、MPFS025T-FCVG484Eをお勧めします。こちらも19 x 19mmパッケージで、拡張商用温度動作と標準スピードグレードに対応しています。254Kの論理素子を持つMPFS250T-1FCSG536T2は、高性能車載用システム向けに設計されており、動作温度範囲は-40~125℃、クロックが15%速い-1スピードグレードで、16 x 16mmの小型パッケージに0.5mmピッチで536個のボールが搭載されています(図4参照)。

図4:車載用温度範囲向けのMPFS250T-1FCSG536T2は、16 x 16mmパッケージ、ボール数536、0.5mmピッチで提供されます。(画像提供:Microchip Technology)

図4:車載用温度範囲向けのMPFS250T-1FCSG536T2は、16 x 16mmパッケージ、ボール数536、0.5mmピッチで提供されます。(画像提供:Microchip Technology)

FPGA SoC開発プラットフォーム

PolarFire FPGA SoCを使用したシステムの設計を迅速に行うため、MicrochipはMPFS-ICICLE-KIT-ES PolarFire SoC Icicleキットを提供し、低消費電力でリアルタイム実行可能な5コアLinux対応RISC-Vマイクロプロセッササブシステムの調査を可能にしています。このキットには、設計の評価に必要なLibero Silverライセンスが無償で含まれています。また、プログラミングとデバッグの機能を1つの言語でサポートします。

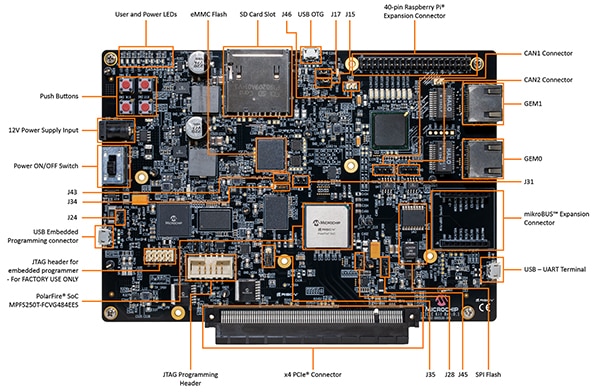

これらのFPGA SoCは、低消費電力で小型フォームファクタのAI/MLアプリケーションを可能にするVectorBloxアクセラレータソフトウェア開発キット(SDK)に対応しています。設計者にFPGAの設計経験がなくても設計できるように、設計プロセスの簡略化に重点を置いています。VectorBloxアクセラレータSDKにより、開発者はC/C++を使用して電力効率の良いニューラルネットワークをプログラムできるようになります。Icicleキットは、さまざまなパワードメインを監視するマルチレールパワーセンサシステム、PCIeルートポートおよび、LinuxやRaspberry Piが動作するLPDDR4、QSPI、eMMC Flashなどの搭載メモリ、有線・無線接続オプションに対応したmikroBUS拡張ポート、GNSS位置情報機能を含む機能拡張など、包括的な開発環境を提供する多数の機能を備えています(図5参照)。

図5:Raspberry Pi(右上)とmikroBUS(右下)の拡張ボード用コネクタを備えた、包括的なFPGA SoC開発環境です。(画像提供:Microchip Technology)

図5:Raspberry Pi(右上)とmikroBUS(右下)の拡張ボード用コネクタを備えた、包括的なFPGA SoC開発環境です。(画像提供:Microchip Technology)

拡張ボード

mikroBUSの拡張ボードの例としては、以下のようなものがあります。

シリアルペリフェラルインターフェース(SPI)を用いてCANバス接続を追加するMIKROE-986。

MCUとRS-232バス間のインターフェース接続用のMIKROE-1582。

RS422/485通信バスと接続するためのMIKROE-989。

LTE Cat M1およびNB1技術に対応し、3GPP IoTデバイスとの接続を確実かつシンプルに実現するMIKROE-3144。

GPSとGalileoに加え、BeiDouまたはGLONASSの同時受信が可能なGNSS機能を持ち、電波の弱い状況やビルの谷間などでも高い位置精度を実現するMIKROE-2670。

まとめ

設計者は、コネクテッド、セーフティクリティカル、ハードリアルタイムな決定論的システムを開発する際に、FPGA SoCを利用することができます。FPGA SoCは、FPGAファブリック、高性能メモリを搭載したRISC-V MCUサブシステム、高速通信インターフェース、多数のセキュリティ機能など、幅広いシステム要素を備えています。また、設計を始めるにあたり、さまざまな通信機能や位置情報機能を実装するための拡張ボードなど、必要な要素をすべて含んだ開発ボードや開発環境が用意されています。

お勧めの記事

免責条項:このウェブサイト上で、さまざまな著者および/またはフォーラム参加者によって表明された意見、信念や視点は、DigiKeyの意見、信念および視点またはDigiKeyの公式な方針を必ずしも反映するものではありません。