デジタル制御ループのアナログ部品をカスタマイズする方法

DigiKeyの北米担当編集者の提供

2022-12-28

モバイル、自動車、モノのインターネット(IoT)などの電気・電子システムの展開が加速し、市場投入までの時間が短縮されていることから、それらを支えるICのテストをより迅速に、より低コストで行う必要性が生じてきています。

この目標を達成するためには、より柔軟でモジュール化された自動ICテストプラットフォームおよび、コストとスペースの両方を低減するための部品点数の削減が必要になります。

これらの要求に応えるため、設計者は従来のアナログコントローラから、ループの安定性を実現するために容易にプログラム可能なデジタル制御ループへと移行しています。デジタルコントローラでは、抵抗、コンデンサ、スイッチが不要になりますが、A/Dコンバータ(ADC)とD/Aコンバータ(DAC)の分解能と精度がデジタル制御ループアーキテクチャの全体精度に大きく影響します。

この記事では、デジタル制御ループの利点について簡単に説明します。その後、タイミングやコンバータノイズのエラーソースなどの実装上の課題についてと、ADCのスループットレートと信号対雑音比(SNR)、DACのセトリング時間とノイズスペクトル密度の仕様に注意して管理することを説明します。

そして、Analog Devicesの24ビット逐次比較型(SAR)ADC「AD4630-24」および、Analog Devicesの電圧出力DAC「AD5791」を紹介します。この2つのデバイスを組み合わせることで、精密計測用の高精度かつ柔軟なデジタルコントローラの基盤を形成することができます。

デジタル制御ループ

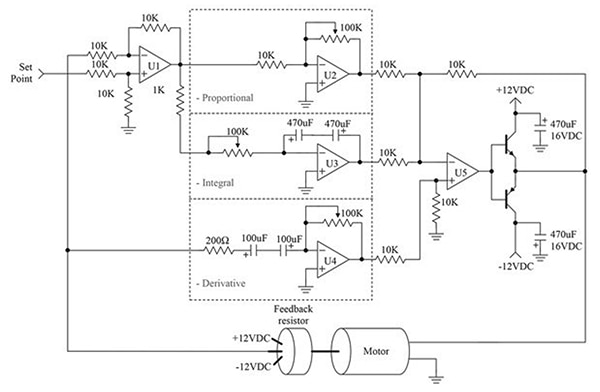

工学システムにおいて、コントローラは過渡状態と定常状態の挙動を満足させるものです。アナログコントローラの実装では、連続した時間間隔に沿って信号が存在し、連続した振幅範囲の値を持つアナログ入力と出力があります。センサは制御される変数を測定し、その挙動を基準信号と比較します。テスト制御動作では、基準値と実測値の差である誤差信号を使用します(図1)。

図1:アナログシステムモータコントローラには、各種アンプ(U1~U5)と、あらかじめ決められた抵抗値やコンデンサ値の集合体が使用されています。(画像提供:Quora)

図1:アナログシステムモータコントローラには、各種アンプ(U1~U5)と、あらかじめ決められた抵抗値やコンデンサ値の集合体が使用されています。(画像提供:Quora)

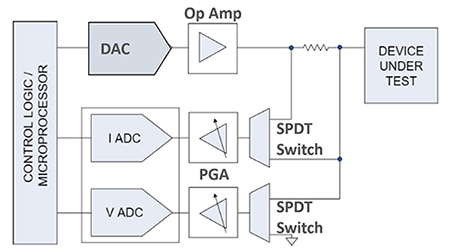

直感的には、出力値をサンプリングするデジタルコントローラよりも、システムのアナログ出力が連続するコントローラの方が優れているように思えます(図2)。

図2:DAC、2つのADC、アナログアンプ、スイッチを使用したデジタルコントローラ構成による計測システム。(画像提供:ボニー・ベイカー氏)

図2:DAC、2つのADC、アナログアンプ、スイッチを使用したデジタルコントローラ構成による計測システム。(画像提供:ボニー・ベイカー氏)

論理的には、デジタル構造で周期的に変化する測定値よりも、連続的に変化するアナログコントローラの制御変数や出力の方が、より良い制御を実現できると考えられます。

この推論は妥当なものです。デジタル制御とアナログ制御のその他すべての要素が同じであると仮定すると、アナログ制御はデジタル制御よりも優れています。では、なぜ従来のコントローラをアナログからデジタルに変えるのでしょうか。その理由は、正確さ、実装の誤差、柔軟性、スピード、コストの5つです。

正確さ:アナログ信号のデジタル表現は0と1で、1つのアナログ値を表現するために最大32ビットが使用されるのが一般的です(図2)。これらの変換により、デジタルの量子化誤差がわずかに発生するため、その対策が必要です。一方、アナログ信号には、電源ドリフトや外来ノイズによる劣化があります。このような温度や時間によるアナログ的なドリフトは制御が難しく、コストもかかりますが、デジタルコントローラでは、経年変化や温度の影響は無視できるほど小さいものです。

実装の誤差:デジタルコントローラでは、実装上の誤差は無視できます。なぜなら、制御信号のデジタル処理では、温度ドリフト誤差を持つアナログ部品や精度の信頼性が低い抵抗、コンデンサ、インダクタではなく、記憶された数値を加算、乗算の関数で使用するからです。また、デジタルコントローラの時定数はソフトウェアで簡単に変更できるのに対し、アナログコントローラの時定数は固定されています。デジタルコントローラの変更はオンザフライで行えるため、さまざまな負荷条件に適応し、テスト全体の効率を向上させることができます。

柔軟性:アナログコントローラは、柔軟性に難があります。ハードウェアの設計が完了した後にプリント基板を修正するのは、時間とコストがかかります。デジタルコントローラの場合、コードの総入れ替えまで簡単に行えます。また、デジタルコントローラの形態や構造に制約がなく、演算オプションを追加した複雑なコントローラ構造も容易に実現可能です。

スピード:コンピューティングの性能は、指数関数的に向上し続けています。この向上により、信号の非常に高速なサンプリングと管理が可能になり、サンプリングの間隔もどんどん狭くなっています。最新のデジタルコントローラの性能は、連続的なアナログ監視システムに匹敵するものです。

コスト:半導体製造技術の進歩によってICのコストが下がり続けているため、小規模で低コストのアプリケーションであっても、デジタルコントローラがより経済的なものとなっています。

デジタルコントローラにおけるアナログ実装の課題

ADCとDACは、アナログ領域とデジタル領域の境界にあり、どちらもさまざまな電気的特性を持っています。2つのデバイスが同じシステムの中で共存できるように、互いの仕様を補完するものを見つけることが秘訣です。システムのスループットの観点からは、転送全体のスピードとノイズの特性を見極めることが重要です。

ADCとDACのタイミング推定値

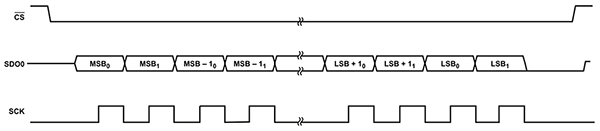

通常、ADCのスループットレートには、メガサンプル/秒(MSPS)またはキロサンプル/秒(kSPS)という明確な定義が存在します。スループット時間(ヘルツ単位の周波数)は、スループットレート(秒)の逆数です。スループット時間とは、コンバータがサンプリング、取り込み、デジタル化を行い、その後の変換の準備をするのに必要な時間のことです。この時間は、連続変換アプリケーションにおける最小変換時間でもあります。仕様の単位は、完全な出力ワードの変換速度を定義します。たとえば、ADCがデジタルシリアル出力ピンを持ち、コンバータが24ビットである場合、アナログ入力の24ビット変換全体が、別の変換の開始前に伝送されます(図3)。

図3:ADCのタイミング図は、コンバータが受け入れるデジタルコードの数を示しています。(画像提供:Analog Devices)

図3:ADCのタイミング図は、コンバータが受け入れるデジタルコードの数を示しています。(画像提供:Analog Devices)

2MSPS仕様のADCは、500ナノ秒(ns)ごとに完全なワードを出力します。残念ながら、この1つの変換サンプルでは、アナログ入力信号の全体像を描き出すことはできません。ナイキスト定理によると、ADCはアナログ入力信号の生成を可能にするために、最低2つのサンプルを生成する必要があります。ナイキスト定理を満たすためには、最低でも500nsの2倍、つまり1マイクロ秒(μs)の時間が必要になります。これは、アナログ信号の骨格を作るための最小限のサンプル数です。アナログ信号をデジタルで再現するには、4~8サンプルが望ましいです。

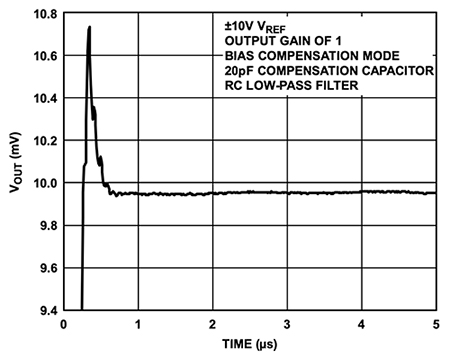

DACの仕様に話を移すと、DACの出力電圧セトリング時間とは、一定の電圧変化に対して、出力電圧が一定のレベルに整定するまでの時間です(図4)。

図4:DACには、最終的な値に到達するために必要な時間を表すセトリング時間誤差が存在します。最悪のセトリング時間誤差は一般的に、出力が100...000と011...111の入力コードの間で推移するときに発生します。(画像提供:Analog Devices)

図4:DACには、最終的な値に到達するために必要な時間を表すセトリング時間誤差が存在します。最悪のセトリング時間誤差は一般的に、出力が100...000と011...111の入力コードの間で推移するときに発生します。(画像提供:Analog Devices)

図4をDACの例とすると、最悪のセトリング時間は1µs以下です。この値の数学的逆数が1MHzに相当し、1MSPSにも相当します。ナイキスト基準に適合させるためには、DACは1μsの2倍の時間、つまり2μsを必要とする2つの出力サンプルを生成しなければならず、ADCと同様、サンプル数は多いほど良いです。

さて、ナイキスト定理についての最後の話です。この定理によれば、信号の再生成には最低でも2つのサンプルが必要です。このシナリオでは、定理は信号の周波数のみを特定します。ここで、この定理に常識を適用する必要があります。サンプル数が多いほど収集に時間がかかりますが、より信頼性の高い信号再構成が可能になるのです。

ADCとDACの周波数ノイズ推定値

ノイズの定義では、コンバータの実際の分解能と二乗平均平方根(rms)ノイズを理解する必要があります。24ビット、20ビット、1ppmなどのコンバータ分解能は、ADCやDACの出力または入力の数を説明しています。たとえば、24ビットADCは1回の変換で24個の出力コードを生成し、20ビットDACは1回の変換で20個のデジタル入力値を収集します。しかし、これらの値には、コンバータの周波数精度の定義がありません。

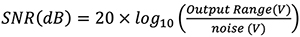

コンバータの精度の定義は、SNRやrmsノイズなどのノイズ仕様に依存します。ADCの出力周波数範囲におけるノイズの仕様は、標準的なデシベル(dB)のSNR値です。SNRは、式1を使用して計算します。

式1

式1

ADCまたはDACのデータシートは、デバイスの出力範囲を定義しています。ノイズは、コンバータの周波数帯域における二乗和平方根(RSS)の累積値です。

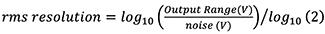

rms分解能は、次の式2を用いて算出します。

式2

式2

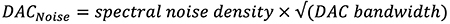

SNRが105.7dBのADCの場合、rms分解能は17.6ビットであり、コンバータがこのレベルまで確実に精度を扱えることを意味します。DACのノイズ仕様は通常、スペクトルノイズ密度の値であるため、DACの実際のrms分解能を素早く換算することが容易になります。DACの出力ノイズは、次の式3によって算出されます。

式3

式3

たとえば、20ビットDACのスペクトルノイズ密度が7.5ナノボルト/√Hz(nV/√Hz)、帯域幅が500kHzの場合、DACNoiseは5.3μV(rms)に相当します。この値から、5V出力時のDACのrmsは19.8ビットに相当します。

デジタルコントローラと精密計測器

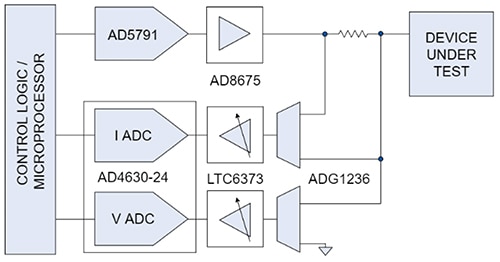

モバイル、自動車、IoTのテスト回路に対応したデジタルコントローラデバイステストシステムの例では、9つのデバイスと1つのディスクリート抵抗が搭載されています(図5)。この回路のデバイスは、マイクロプロセッサ、ADC、DAC、ドライバアンプ、ゲイン調整可能な計装アンプ、Analog Devicesの「ADG1236」SPDTスイッチです。マイクロプロセッサは、Analog DevicesのAD4630-24やAD5791のようなADCとDACの間のデジタルインターフェースとデータを管理します。

図5:デジタルコントローラは、マイクロプロセッサを使用してADCとDACのデータを管理します。DACにはゲイン出力ドライバアンプが必要で、ADCには信号を減衰させるアンプシステムが必要です。(画像提供:Analog Devices)

図5:デジタルコントローラは、マイクロプロセッサを使用してADCとDACのデータを管理します。DACにはゲイン出力ドライバアンプが必要で、ADCには信号を減衰させるアンプシステムが必要です。(画像提供:Analog Devices)

AD4630-24は、2MSPS、24ビット、±0.9ppmの積分非直線性(INL)を備えたADCで、SNRは105.7dB、17.6ビット(rms)が生じます。2MSPSの変換速度を持つこのADCは、アナログ信号を生成するために最低4つの出力サンプルを必要とします。INLは、コンバータのDC精度を表します。

AD5791は、20ビット、±1LSB INL、1µsのセトリング時間、7.5nV/√Hzスペクトル密度のDACで、最終的に19.8ビット(rms)が生じます。このDACは、1MSPSの速度で、アナログ信号を正確に生成するために4μsが必要です。

また、このシステムのコンバータは、出力駆動とアナログゲインを管理するためにオペアンプインターフェースを必要とします。図5では、Analog DevicesのAD8675が、10MHz、2.8nV/√Hzのレールツーレール出力オペアンプです。このアンプのノイズにより、DACシステムのビットは19.1(rms)にまで低下します。しかし、10MHzのアンプ帯域はDACの帯域幅を上回っています。

Analog DevicesのLTC6373完全差動プログラマブルゲイン計装アンプは、ゲインとある程度の絶縁を提供します。DACステージが4ボルト/ボルト(V/V)のゲインを実装している場合、LTC6373のゲインオプションの1つは0.25V/Vで、信号を元の値に戻します。LTC6373のデジタルゲインレベルの柔軟性は、デジタルコントローラのオンザフライ特性に貢献します。

まとめ

モバイル、自動車、IoTなどの電子テストシステムにおいて、市場投入までの時間に対する圧力と、急速に進化する設計要件をサポートするためのコストにより、従来のアナログコントローラからデジタル制御ループへの移行が進んでいます。デジタル制御ループは、より高い精度と柔軟性、そして低コストを実現しますが、ADCとDACの選択には十分な注意が必要です。

上述したように、Analog Devicesの24ビットSAR ADC「AD4630-24」と20ビット電圧出力DAC「AD5791」を組み合わせることで、精密計測用の高精度かつ柔軟なデジタルコントローラを実現できるのです。

免責条項:このウェブサイト上で、さまざまな著者および/またはフォーラム参加者によって表明された意見、信念や視点は、DigiKeyの意見、信念および視点またはDigiKeyの公式な方針を必ずしも反映するものではありません。