FPGAに取り組むArduino製品: 構成済みおよびカスタム双方のIPにAloriumのSnōモジュールを使用

DigiKeyの北米担当編集者の提供

2019-05-01

フィールドプログラマブルゲートアレイ(FPGA)は、マイクロコントローラまたはマイクロプロセッサ上で実行するファームウェアの処理が遅すぎる場合に、リアルタイム組み込み設計の問題をハードウェアで解決する方法をもたらします。さらにFPGAはペリフェラルにも柔軟性をもたらします。ただしFPGAを使用する場合には、新しいプログラミング言語(通常はVerilogまたはVHDL)や、FPGAビットストリームを生成するまったく新しい開発フローの学習が必要となり、さらにFPGA開発ボードに多額の資金がかかることもあります。

これらが障害となり、FPGAは設計ツールボックスの中でも非常に有用なツールであるにもかかわらず、多くの設計エンジニアがFPGAを使うことに後ろ向きです。この敬遠されがちな状況を解消するために、FPGAを短期間で習得できる環境づくりに努力しているベンダーもあります。たとえばArduinoからは、Arduino ABX00022 MKR Vidor 4000 FPGA開発ボードが登場しました(「Arduino MKR Vidor 4000によるFPGAのすばやく簡単な応用」を参照)。Arduino MKR Vidor 4000は、非常に人気の高いArduino統合開発環境(IDE)とシームレスに統合するFPGAのプログラミング手法を加えることで、特別なArduinoライブラリ拡張を使用してFPGAレベルのパフォーマンスを獲得しています。

そして現在、これまでの製品に代わる、Arduino MKR Vidor 4000ボードを含む新たな製品が出現しています。Alorium Technologyは、Arduino組み込み開発の分野にFPGAの性能をもたらす、独特な手法を開発しました。Aloriumのアプローチは、I/O加速のための構成済みのIPブロックと、カスタム設計によるIPブロックの両方を扱います。

この記事では、これまでのFPGAの使用方法について簡単に説明します。次に、AloriumのArduino互換XLR8R22M08V5U0DIおよびSnō SNOR20M16V3 FPGAモジュールについて詳しく検討します。またAloriumが、Arduino技術の延長線上で構成済みIPの使用とカスタムIP作成の両方に対応するために、FPGAを使用する独自のアプローチをどのように加えたか、さらに設計者がFPGAモジュールを応用しながらどのように設計を始められるかについて説明します。

Arduinoをスピードアップする方法

世界中の何十万人もの設計者、エンジニア、開発者、DIY愛好家、そしてメーカーが、さまざまなバージョンのArduino開発ボードシリーズを使用して、多様なアプリケーションの組み込みシステムを開発しています。ArduinoボードとArduino IDEは使用方法やプログラミングが非常に簡単なので、幅広い分野で利用されています。

Arduinoユーザーは、オリジナルのArduinoアーキテクチャをより複雑なアプリケーションに応用し続ける中で、性能の問題に直面しました。性能問題の1つには、オリジナルのArduinoマイクロコントローラのシンプルな8ビットアーキテクチャがあります。また別の問題は、Arduinoの組み込みマイクロコントローラに同等のハードウェアブロックがない場合に、Arduinoソフトウェアシステムが多くのリアルタイムペリフェラルをソフトウェアによって実装している手法にもあります。

この性能問題に対処する1つの方法は、より高機能なマイクロコントローラを使用することですが、ソフトウェアがリアルタイム環境でできることはやはり限られます。一部の高速なリアルタイムペリフェラルは、ハードウェアで実装する必要があります。より多くのハードウェアペリフェラルを含むマイクロコントローラを指定することも可能ですが、ペリフェラルの正しい組み合わせはプロジェクトごとに異なります。

マイクロコントローラのメーカー各社は、マイクロプロセッサファミリの数十、場合により数百ものバリエーションを提供することで、異なるペリフェラルの組み合わせのニーズに対応してきました。しかし、Arduinoのようなボードレベルの製品にとっては実際的な手法ではありません。なぜなら、あらゆるニーズに対応するために十分なI/Oピンを備えたオンボードコネクタが必要だからです。現在Arduinoボードには多くの派生モデルがありますが、あらゆる組み込みプロジェクトのニーズを満たすにはまだ不十分です。

さまざまなペリフェラルの組み合わせのニーズに応えるFPGA

組み込み設計者向けにプログラム可能なハードウェアを利用できるようにすることで、FPGAはプロジェクトごとに異なるペリフェラル組み合わせのニーズに対応できます。FPGA機能を組み込みマイクロコントローラボードに加える1つの方法は、FPGAを単に既存の設計に追加することです。ArduinoはArduino MKR Vidor 4000ボードの設計に、その手法を採用しました。このボードには、Microchip Technologyの32ビットArm® Cortex®-M0+ベースのATSAMD21G18A-AUT SAMD21低電力マイクロコントローラとIntelの10CL016YU484C6G Cyclone 10 FPGAの組み合わせが搭載されています。

Arduinoは、特にMKR Vidor 4000ボードに合わせて、Arduino IDEにいくつかのハードウェアIPブロックを追加しました。これらのペリフェラルは、 VidorPeripheralsとVidorGraphicsの2つのメインのライブラリにより利用できます。これらのハードウェアIPブロックは、該当するペリフェラルライブラリがArduinoスケッチ(Arduinoがプログラムまたはコードの単位に使用している名前)に含まれる場合に、Arduino MKR Vidor 4000上のIntel Cyclone 10 FPGAに自動的に構成されます。現行のペリフェラルIPブロックには、次があります。

- I2Cポート

- SPIポート

- UART

- 高周波PWMコントローラ

- 高速タイマ

- 高速直交デコーダ

- Adafruit IndustriesのNeopixelアドレス指定可能RGBスマートLEDコントローラ

I2CやSPIなど、これらのペリフェラルのいくつかは、以前のArduinoボードでソフトウェアIPブロックとしてすでに提供されていました。これらの以前のソフトウェア実装と、Arduino MKR Vidor 4000ボードのFPGAに実装されている同等のIPブロックとの違いは、FPGAバージョンのペリフェラルが格段に優れた性能を発揮することにあります。たとえば、I2CとSPIのそれぞれのインスタンス化は、ボードのFPGA内部にある別個のプログラム可能なハードウェアブロックで実装されています。これにより、このようなシリアルポートをいくつかインスタンス化してもパフォーマンスの低下はありません。

FPGAハードウェアとしてペリフェラルブロックを実装し、Arduinoスケッチライターに馴染みのある同じライブラリメカニズムによりそれらを使用可能にすることで、Arduino MKR Vidor 4000ボードではFPGAを簡単に使えるようになっています。VHDLやVerilogなどの新しいハードウェア記述言語(HDL)を学習する必要はありません。実際にFPGAベースのペリフェラルは、プログラマの視点では他のC++オブジェクトと同様に見えます。Arduinoは、このようなハードウェアIPブロックペリフェラルを今後さらに追加する予定です。

Arduino MKR Vidor 4000ボードは、HDLコードを使用してオンボードCyclone 10 FPGAを直接プログラミングする機能はサポートしないため、まだ汎用FPGA開発ボードではありません。Arduinoは、上級のユーザーがArduino MKR Vidor 4000ボードのFPGAからIntelのArduino製FPGA向けQuartus HDL開発ツールを使用して、より多くのユーティリティを実現できるようにすることを計画しています。

次のステップを踏み出すAlorium

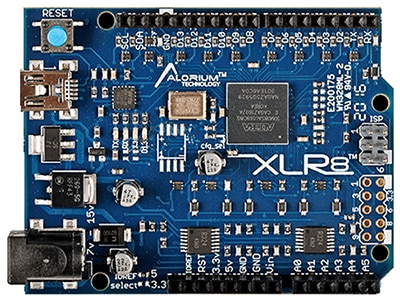

Aloriumは、Arduino互換のXLR8R22M08V5U0DIおよびSNOR20M16V3 Snō FPGA開発ボード用のOpenXLR8メソドロジーおよびXcelerator Block(XB)により、次の段階に踏み出しました(それぞれ図1および図2)。両ボードとも、内蔵フラッシュ構成用メモリを搭載したIntelのMAX 10 FPGAファミリの異なるバージョンをベースにしています。XLR8は、Intelの10M08SAU169C8G MAX 10と8ビットATmega328命令セット互換マイクロコントローラを組み合わせています。オリジナルのArduino Uno開発ボードと同じフォームファクタを使用しているので、Arduinoのシールド、アクセサリの多くと互換性があります。

図1: Alorium TechnologyのXLR8R22M08V5U0DI開発ボードはIntelのMAX 10 FPGAと8ビットATmega328命令セット互換のマイクロコントローラをArduino Unoフォームファクタに組み合わせています。(画像提供: Alorium Technology)

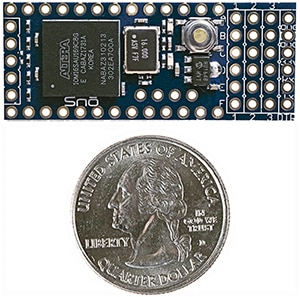

AloriumのSnō FPGAモジュールは、0.7 x 1.7インチの非常に小さな開発ボードです(図2)。Snō FPGA開発ボードは物理的に小型ですが、IntelのMAX 10 FPGAの大型バージョン、10M16SAU169C8G MAX 10 FPGAを統合しています。このロジックエレメントは16Kで、XLR8ボード上の10M08デバイスの8Kと比較して2倍です。また、I/Oピン数は2倍以上で32本備えています(XLR8ボードでは14本)。

図2: XLR8開発ボードのように、Alorium TechnologyのSnō FPGA開発ボードは8ビットATmega328命令セット互換マイクロコントローラとIntel MAX 10(この場合10M16SAU169C8G FPGA)とを組み合わせています。にもかかわらずSnō FPGA開発ボードはより小型です。(画像提供: Alorium Technology)

AloriumはSNOMAKRR10ブレイクアウトボードも提供しています。このボードはSnō FPGAモジュールを受けて、それをUSBポートとFPGAからの追加のI/Oブレイクアウトピンにより多少大きめのArduinoフォームファクタボードに変換します。Snō FPGAモジュールのピンには、SnōMAKRブレイクアウトボードのArduino互換シールドヘッダに通じるピンと、USBコネクタの反対側にあるボードの縁沿いに追加のヘッダに通じるピンがあります(図3)。

図3: AloriumのSNOMAKRR10ブレイクアウトボードは同社のSnō FPGA開発ボードを、USBポートとオンボードのレギュレータによりArduino互換フォームファクタに変換し、USBケーブルは開発ボードに直接給電できます。(画像提供: Alorium Technology)

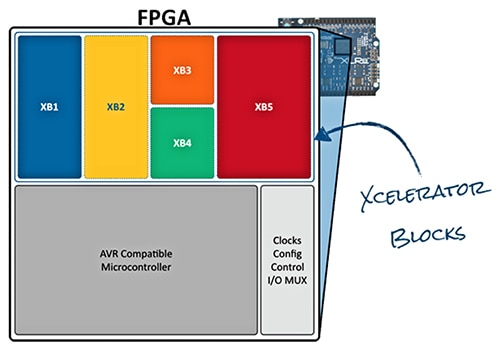

XLR8とSnō FPGA開発ボードはどちらも8ビットマイクロコントローラとそのハードウェアペリフェラルを1チップ(IntelのMAX 10 FPGA)に実装しています。図4は、その仕組みを示しています。

図4: XLR8とSnō FPGA開発ボードはいずれもAtmelのAVR互換マイクロコントローラをソフトコアとしてMAX 10 FPGA内部に実装しています。(画像提供: Alorium Technology)

AVR互換のマイクロコントローラコア(図4の左下)は、オリジナルのArduino開発ボードに使用されたのと同じAtmelのATmega328 8ビットAVRマイクロコントローラです。しかし、AloriumバージョンのAVRマイクロコントローラは、別個のチップに搭載されているのではなく、FPGA内部にソフトコアとして実装されています。

図4には、マイクロコントローラコアの上に5つのAlorium XB(XB1からXB5)が示されています。XBは、FPGAのオンチップリソースを使用して実装されたIPブロックです。AVRマイクロコントローラは、アドレス指定可能なレジスタインターフェースを介してオンチップXBと通信します。XLR8とSnō開発ボードには、Arduino開発者に必要なペリフェラルに該当する次のようなXBがプリインストールで同梱されています(GitHubでも入手可能)。

なお、上記の最後のXBは、実際にはI/Oペリフェラルブロックではなく浮動小数点演算アクセラレータです。XBにはあらゆるタイプのハードウェアアクセラレータが該当します。I/Oに限定されません。

任意のブロックをピックアップ

XLR8とSnō FPGA開発ボードをフィールドで更新するには、異なるXB(または同じXBの複数のコピー)を選択し、AloriumのOpenXLR8開発フローを使用してそれをFPGA内でインスタンス化します。開発者は、AloriumのOpenXLR8フローを使用してカスタムのXcelerator Blockを作成することもできます(図5)。

図5: AloriumのOpenXLR8開発フローにより、設計者はIntelのQuartus Prime設計ツールを使用して新しいハードウェアブロックを作成し、それをArduino IDEに加えることができます。(画像提供: Alorium Technology)

現時点でカスタムXBを作成するには、VerilogまたはVHDLハードウェア記述言語の実務知識と、IntelのQuartus FPGAツールスイート、具体的にはQuartus Prime Lite Editionのバージョン17.1、およびMentor GraphicsのModelSimシミュレーションツールに関する知識が必要になります。HDLはFPGA開発に必要です。なぜなら、これらにより設計者は複数タスクの並列実行を標準的な明確に規定された方法で表現できるからです。CやC++などの高水準言語(HLL)は、本質的に順序言語です。

HLLコンパイラはHLLソースコードを受け取り、それを機械命令の長いシーケンスに変換し、通常そのシーケンスは一度に1つずつ実行されます。このため、FPGAはプロセッサよりも大幅に高速になり、十分な大きさのFPGAであれば何千ものタスクを同時に実行できます。CまたはC++で記述されたコードをHDLに変換するHLLコンパイラがあり、変換されたHDLはさらに従来のFPGAツールで処理されますが、このHLLコンパイラは現時点ではAloriumのOpenXLR8設計フローには含まれていません。

ただし、HDLとFPGA開発ツールを使用してXBを設計しデバッグを終えれば、他のArduinoライブラリブロックと同様にArduino IDEでそれを使用できます。Aloriumは現在、Arduino IDEライブラリ用に他のXBも開発しています。

結論

ArduinoとAlorium Technologyの両社とも、各自のFPGA開発ボードを作成する中で、これらの手ごろな価格の開発ボードを使用してより高い組み込み性能を得ようとする設計者のニーズが広がっていると認識しています。これら2社はある意味で別々の道を辿りながらも、最終的には、FPGAをより多くの組み込み開発者に利用してもらえるようにする方法を見つけるという、同じ目標を目指しています。端的に言えばArduinoとAloriumのどちらのアプローチも、ブロックをピックアップしてスクリプトを実行するような、シンプルなハードウェア設計を目指しています。

現時点では、設計フロー全体はまだ可能な限りシンプルではありません。Arduinoは同社の完全なFPGA開発フローをまだHDL開発者に披露していません。Aloriumの設計フローはHDL設計に対応しますが、VerilogまたはVHSL FPGA設計言語やツールに関する知識が必要です。

しかしこれらの製品によって扉は開かれたので、CやC++ハードウェアコンパイラなど、他のFPGA開発の進歩に期待することは少なくとも理論的には可能です。それまで、Alorium TechnologyとArduinoがこれらの機能をArduino IDEに追加するために開発したシンプルなメソッドを使用することで、FPGAのパフォーマンスをある程度引き出すことができるでしょう。

免責条項:このウェブサイト上で、さまざまな著者および/またはフォーラム参加者によって表明された意見、信念や視点は、DigiKeyの意見、信念および視点またはDigiKeyの公式な方針を必ずしも反映するものではありません。