自己測定および診断の適用によりセンサデータの完全性を保証

DigiKeyの北米担当編集者の提供

2019-03-29

センサとモノのインターネット(IoT)の技術が産業用、商用、さらには消費者向けの分野にまで急速に広がり、存在感を増しつつあります。こうした展開につれ、そこで使用されるセンサとフロントエンドのインターフェース回路からのデータの完全性を保証する必要性が高まっています。

データ完全性の潜在的な問題は、単一のインターフェースICが複数のセンサをサポートする場合、その単一のICの問題によって1クラスタ分の読み取り値が損なわれる恐れがあるため、いっそう重大になります。このことが、ひいては状況の不正確な評価につながり、不適切あるいは危険さえあるシステムの動作を招くことがあります。

この記事では、センサからプロセッサに至る信号チェーンにおけるハードな故障とソフトな(一時的)故障の両方についてさまざまな要因を見ていきます。それから、Analog Devicesの高度に統合化されたICを紹介し、それを使用して、センサやIC自体、そのデジタルI/Oに対する診断により、問題を克服する方法を示します。

センサからプロセッサまでの信号経路

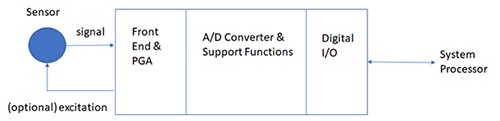

最終的にあらゆるセンサ読み取り値の完全性に影響を及ぼす要因の第一は、図1に示す信号チェーンの3つの主要機能ブロックです。これらのブロックは以下のとおりです。

- センサとそのリード線

- A/Dコンバータ(ADC)に信号コンディショニングICのアナログフロントエンド

- システムプロセッサへのデジタルI/O

図1: 基本的なセンサからプロセッサまでの信号経路は、原則的にほんの数個の基本機能から成りますが、実用的で有用なインターフェースICは他にも多くの機能や特長を備えています。(画像提供:DigiKey)

多チャンネルシステムの場合、そこで使用されるセンサ群はしばしば、熱電対、抵抗温度検出器(RTD)、圧力センサなどさまざまな種類が混在しています。もちろん、センサが故障することや、接続リード線の断線あるいは隣接したリード線や電源レールやグランドとの短絡が発生することもあります。

センサのタイプによっては、リード線の不具合によって読み取り値が「測定限界外」となり、即座に見てわかることがあります。それと対照的に、不具合の様態によっては不正確ながらも正規の信号に見える読み取り値になることもあります。また、RTDなど一部のセンサでは外部刺激電流が必要なものがあり、この電流は、有効な読み取り値を得るために設定された範囲内にある必要があります。これらの理由から、センサとアナログフロントエンド間の信号経路の連続性を検査し、さらに信号が許容される下限と上限の範囲内に収まっていることを確認することが適切であり、その場合、考えられるADCの問題の影響を受けないアナログ回路を使用することが望ましいと言えます。

このようにして得られる読み取り値は単に正確であるだけでなく、それにより極めて高い信頼性のあるソースデータを使用してシステムの意思決定アルゴリズムを実行できることにもなります。

しかし、こうした追加の検査と調整には、追加部品、より大きなフットプリント、より長い設計期間が必要になります。

自己測定ICによりセンサデータの完全性を保証

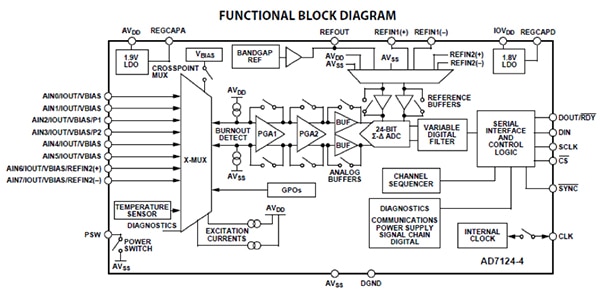

高度なデータ完全性の必要性に対し、設計期間およびフットプリントへの影響を最小限に抑えつつ応えるため、Analog Devicesはセンサ重視のADCと、基本的な信号の調整および変換を大幅に超えるインターフェースを備えたAD7124-8BCPZ-RL7を発売しました。この製品は、多信号機能およびデータ完全性を保証するための自己診断機能を備えています。

図2: センサ重視のADCおよびインターフェースを備えたるAD7124は、基本的な信号の調整および変換の機能を大幅に超え、多信号機能およびデータ完全性を保証する自己診断機能を備えています。(画像提供:Analog Devices)

AD7124は、4チャンネル、低ノイズ、24ビットのシグマデルタ(Σ-Δ)デバイスです。サンプリングレートは、多種類のセンサおよびそれらのアプリケーションに適した1サンプル/秒を少し上回るレートから19,2001サンプル/秒までに対応しています。最低サンプリングレート時の消費電流は255マイクロアンペア(µA)です。このデバイスの読み取り値の確度は、低ノイズ、実効値25ナノボルト(nV)未満、内蔵電圧リファレンスの低ドリフト(10 ppm/°C)を重視した設計により高められています。

AD7124自体は32ピンLFCSPおよび24ピンTSSOPのパッケージで提供されています。柔軟なデジタルI/Oは、3線式および4線式SPI、QSPI、MICROWIRETM、DSP互換のインターフェースをサポートしています。

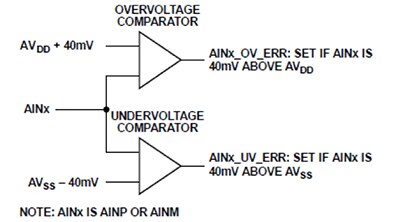

AD7124は、前述したセンサのリード線の問題に信号制限値アラームとバーンアウト電流検知という2つの技術を使用して対処しています。信号制限値アラームは過電圧/不足電圧アラームモニタを使用して4対のアナログ入力接続の各絶対電圧を検査します(図3)。この電圧はデータシートの仕様を満たす設定範囲内にある必要があります。

図3: 信号制限値アラームによるセンサの基本的検証では、固定の最小/最大設定値を持つハードウェアコンパレータを使います。(画像提供:Analog Devices)

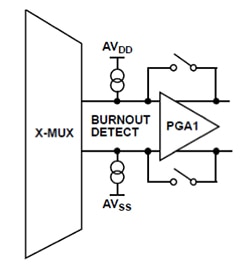

バーンアウト電流検知では、プログラム可能な相補電流シンクおよびソースのペアを使用します。事前定義された電流のペアのセンサピンへのソースとシンクにより、 AD7124はそれらの完全性を検証できます(図4)。これらの電流はフルオンまたはオフですが、選択した検査対象のアナログ入力線ペアへ切り換えられます。

図4: 事前定義された電流のペアのセンサピンへのソースとシンクにより、AD7124はそれらの完全性を検証できます(図4)。(画像提供:Analog Devices)

フルスケールの(またはそれに近い)読み取り値は、フロントエンドセンサ回路が断線していることを意味する場合があります。測定電圧が0ボルトの場合、トランスデューサが短絡していることを示している場合があります。エラーレジスタの対応するフラグビットがセットされ、エラーの発生とその種類を示します。

最後に、RTDまたは歪みゲージでよく行われることですが、内部リファレンスを使う代わりに外部のリファレンスをユーザーが提供するアプリケーションの場合、AD7124はすべての外部変換参照電圧が正確であることを検査します。

フロントエンドとADCの検証

外部センサとそのリード線は問題の原因となる可能性が最も高いですが、フロントエンド/変換IC自体の性能を検証することが不可欠です。仕様外となる、または全く誤動作する場合のある機能には、以下のものがあります。

- ADCの内部電圧リファレンス

- 最高の分解能を得るため入力信号を増幅してADCの入力幅に一致させるプログラマブルゲインアンプ

- 必要なセンサ励起のための低ドロップアウトレギュレータ(LDO)

- 本ICの内部電源レール

- ADC自体

信号チェーンのアナログ部分を検査するため、AD7124はハードウェアおよびファームウェアによる自己検査を開始します。4つの差動入力チャンネルのいずれにも内部的に接続してデジタル化できる20ミリボルト(mV)信号を生成します。こうすることは複数の目的に役立ちます。入力チャンネルマルチプレクサおよびADCの基本動作を確認できます。また、PGAのゲイン設定の変更とその結果得られるADCの読み取り値の確認によりPGAの評価もできます。

ADCも発生しうる問題の要因になります。AD7124は、確立されたΣ-Δコンバータアーキテクチャを採用し、1ビット変調器と必要なデジタルフィルタを備えています。ADCの性能を十分にテストするには、アナログとデジタルの両方の手法を用います。

AD7124の場合、変調器出力に20個の連続した1または0が含まれている場合、それは変調器が一方のレールまたはもう一方のレールに飽和していることを示し、エラーフラグビットがセットされます。同様に、このICは自己開始したオフセット較正の後、ADCオフセット係数が0x7FFFFと0xF80000の間にあることを確認します。範囲外である場合には、もう1つのエラーフラグがセットされます。最後に、フルスケール較正中にデジタルフィルタの何らかのオーバーフローが発生すると、別のエラーフラグビットがセットされます。

内部および外部の電源および電源レールも問題の原因になる可能性があります。多くのセンサは小さな励起電力を必要とし、これはしばしばアナログフロントエンドIC内の小さな低ノイズLDOによって供給されます。

AD7124はそのLDO出力を2通りの方法で検査します。1つ目として、LDOの出力を内部的にADCに接続して想定値と比較できます。2つ目として、ADCと独立のハードウェアコンパレータでLDOとこのICのリファレンスと継続的に監視できます。LDO出力が事前設定済みの閾値未満に低下すると、エラーフラグビットがセットされます。その結果、初期化中にLDOを評価することができ、またプロセッサリソースを絶えず消費することなく継続的に行うこともできます。

さらに信頼性を高めるため、電力供給の監視に使われるテスト回路は、入力をグランド(公称0ボルト)に接続してデジタル測定値を確認することにより(ある程度)検査できます。AD7124は、必要な0.1マイクロファラッド(µF)のカップリングコンデンサの存在と接続を確認することにより、このデータ完全性の保証をもう1段階高めます。これは、内部スイッチによってデカップリングコンデンサを物理的に切断してからLDO出力を検査することをAD7124に指示することで行います。LDO電圧が低下すると、デカップリングコンデンサは電気的に存在しないのと同じになります。この場合もやはりエラーフラグビットがセットされます。

もちろん、すべてのICには、それを超えると仕様外となる、または動作しなくさえなる最高温度定格があります。そのため、常にダイ温度の読み取り値を通常の確度±0.5°Cで与えるセンサがAD7124に組み込まれています。

デジタル誤差について

ここまではアナログセンサまたは変換の機能に関して性能と確度を保証することを見てきました。しかし、多数のこうしたセンサが配備されている、電気的に過酷な産業用環境には、デジタル電子回路に影響を及ぼすノイズ、EMI/RFI、過渡現象が存在します。そのため、内部電子回路に加えてに、データおよび読み書き動作の高い信頼性を確保するシステムプロセッサへのインターフェースリンクの性能を保証することが重要です。

AD7124は、以下の動作と特長をはじめとした多面的なアプローチによって、これを達成しています。

- マスタクロックの性能の検査マスタクロックは、出力データレート、フィルタセトリング時間、フィルタノッチ周波数を設定するために必要です。これは、いつでも再読み出しができる独立したカウントアップレジスタによって検査されます。

- SPIの各読み書き動作に使用されるSCLKパルスの数は特殊なクロックカウンタを介して検査されます。この数は8の倍数であることが必要です(すべてのSPI動作では8、16、40、48のいずれかのクロックパルスを使用)。

- AD7124は読み書き動作が有効なレジスタアドレスのみをアドレッシングすることを確認します。

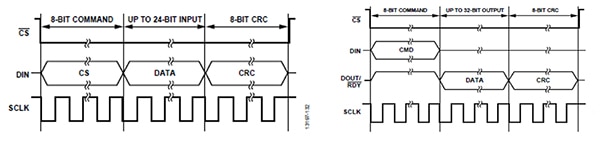

これらのステップにより内部動作に対処できますが、プロセッサインターフェースおよびそのデータの完全性は保証しません。データの極めて高い信頼性を実現するため、ユーザーはAD7124に対して巡回冗長検査(CRC)多項式チェックサムアルゴリズムを実行するよう指示できます。このチェックサムにより、有効なデータのみがレジスタに書き込まれることの保証と、レジスタから読み出したデータを検証することができます(図5)。チェックサムは、1ビットの誤りさえ検出する信頼性の高い技術ですが、誤りの訂正はできません。

図5: 1ビット誤り検出のために、多項式を使用したCRCチェックサムがSPI書き込み(左)およびSPI読み出し(右)のトランザクションに付加される。(画像提供:Analog Devices)

この動作が有効化されると、データブロックのチェックサムを計算し、読み書きの各トランザクションの末尾に付加します。レジスタ書き込みが正しく行われたことを保証するには、レジスタから読み出して、格納されているチェックサムをデータから計算したものと比較検証する必要があります。

電気的に過酷な状況においては、メモリでさえビット誤りが発生することがあります。内蔵レジスタにおけるそうした誤りに対する高度な検査を実現するため、AD7124は以下のような多くの動作ごとにチェックサムを計算します。

- レジスタ書き込みサイクルを実行したとき

- オフセット/フルスケール較正をしたとき

- 本デバイスが単一の変換サイクルを実行し、変換後にADCがスタンバイモードに入るとき

- 連続読み出しモードを終了するとき

信頼性を高めるため、内蔵の読み出し専用メモリ(ROM)も評価されます。電源投入時、全レジスタがROMに格納されているデフォルト値に初期化されます。ROMの内容についてのCRCの計算が電源投入時に実行されます。その結果が保存されているCRCの値と異なっていれば、それは少なくとも1ビットの誤りが存在していることを示します。

AD7124は、多種類のセンサの励起と共に、アンプおよびPGAによる信号調整およびセンサ出力信号のスケーリングも行うことができます。極めて高い信頼性を実現するため、AD7124は、初期化処理、必要な機能モードおよびパラメータの設定、各種エラーおよびフォルトのフラグのための内部レジスタを多数備えています。

AD7124設計の手始めにAD7124評価ボードを使う

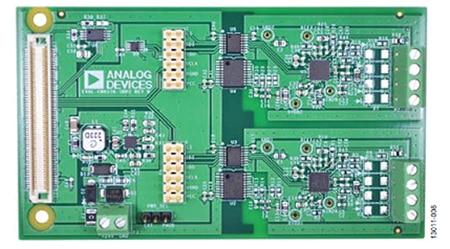

AD7124は多くの設計可能性と高性能機能を備えた複雑なシステムです。単なる「差し込んですぐ使える」タイプのセンサインターフェースICではありません。学習を促進し、その潜在機能に設計者が素早く精通できるように、Analog DevicesはEVAL-CN0376-SDPZ評価ボードも提供しています(図6)。

図6: EVAL-CN0376-SDPZ評価ボードはデザインインを迅速化し、AD7124の多くの機能および特長のすべて働かせることができます。(画像提供:Analog Devices)

この評価ボードには電源と、AD7124を実世界のさまざまなセンサおよびプロセッサと接続するために必要な外部コンポーネントが含まれています。Windows PC用のCN-0376評価ソフトウェアでサポートされており、このソフトウェアは設定およびこの評価ボードからのデータ取得のためにUSBポート経由で通信します。

まとめ

システムプロセッサに組み込まれたアルゴリズム、そして現在では多くの場合に人口知能(AI)によって強化された高度なアルゴリズムによって、多くの重要な決定が為されています。これらのアルゴリズムを適用して、結論を出し、アクションを取る。そのための生データに高い完全性をもたせることが、これまで以上に非常に重要になっています。AD7124などのICは、求められるデータの信頼性を高める仕組みを積み重ねることにより、リード線およびセンサインターフェースからICの性能および機能におよぶ信号チェーンの各部が想定通りに動作し、正常であることを保証します。

免責条項:このウェブサイト上で、さまざまな著者および/またはフォーラム参加者によって表明された意見、信念や視点は、DigiKeyの意見、信念および視点またはDigiKeyの公式な方針を必ずしも反映するものではありません。