すぐに入手可能なIEEE 802.3btソリューションを使用した高電力PoEにおける設計

DigiKeyの北米担当編集者の提供

2019-05-09

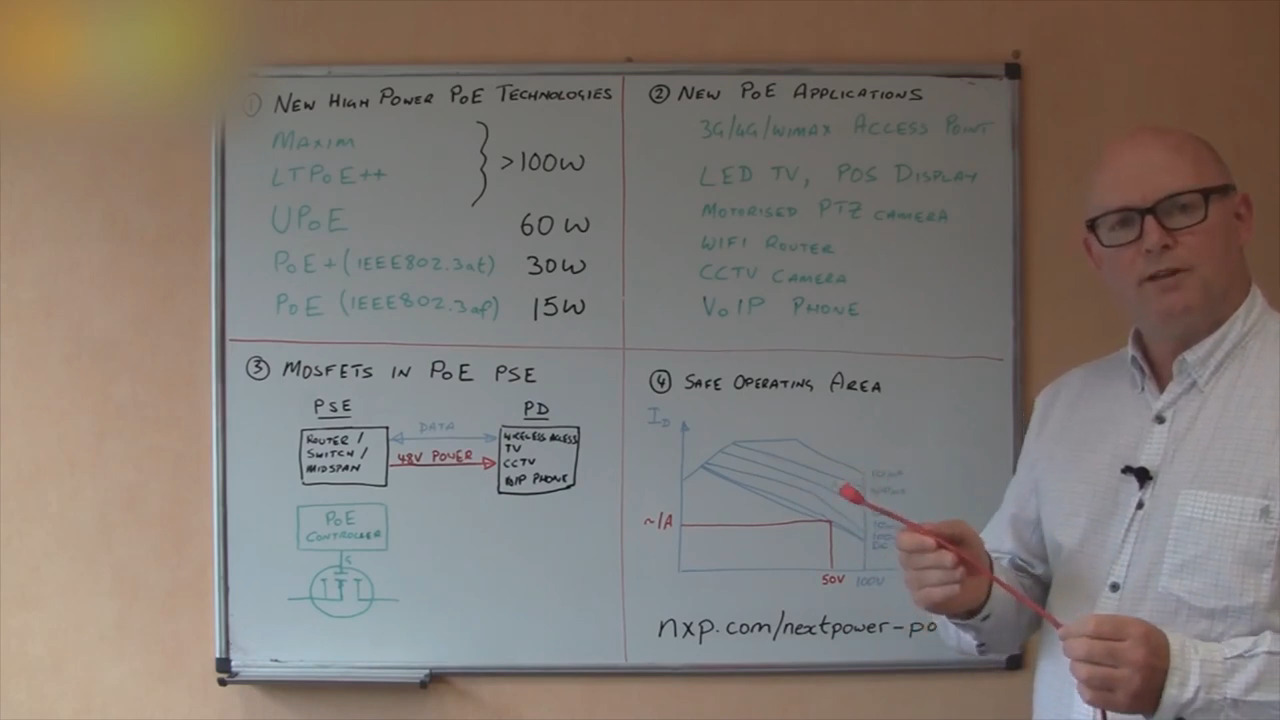

2003年にPoE(Power over Ethernet)が導入されて以来、その電力供給機能は15.4Wから30Wへ劇的に向上しましたが、設計者はアプリケーション用にさらなる向上を必要としています。PoE仕様の最新修正版であるIEEE 802.3btは、最大60W(一部のアプリケーションでは最大90W)の電源を実現することにより、そのニーズに対処しています。

修正版は2018年後半に承認され、現在では最初の商用統合電源装置(PSE)コントローラおよび受電側機器(PD)インターフェースが入手可能になっています。これにより、設計技術者は「高電力PoE」と呼ばれるものを活用できるようになりました。

この記事では、まずIEEE 802.3btと以前のバージョンのPoEとの違いを説明し、それからMicrosemi、Texas Instruments(TI)、Linear Technology、およびNexperiaの統合PSEコントローラおよびPDインターフェースを紹介します。これらのデバイスを応用してシステムを構築するのに最適な方法を説明し、回路保護や設計およびレイアウト要件などの重要な考慮事項を取り上げます。

IEEE 802.3btとは?

最大15.4Wの電源が仕様規定された元々の標準(IEEE 802.3af)は、IP電話やWi-Fiアクセスポイントなどのアプリケーションには十分でしたが、IPビデオ電話やパン/チルト/ズーム(PTZ)カメラなどの最新アプリケーションには不十分です。2009年の仕様修正(IEEE 802.3at)では、電源を30Wに規定することにより、この問題を解決しました。近年では、販売時点管理(POS)端末、IEEE 802.11acアクセスポイント、ネットワーク接続LED照明などのEthernetに接続されたアプリケーションに対応するため、電源需要はさらに増大しています。

増大する電源ニーズに対処するため、以前のPoEおよびPoE+仕様の最新修正版であるIEEE 802.3bt(高電力PoE)は、PSEの最小出力電力とPDの最小入力電力を増加させます。主な変更点は、Cat5e Ethernetケーブルの4つのツイストペアで電源をキャリーオーバーできるようになったことです。PoEおよびPoE+では、2つのツイストペア(「代替A」アプリケーションのデータラインまたは「代替B」アプリケーションのスペアライン)だけを使用していました。(DigiKeyのライブラリ記事『Power-over-Ethernetの紹介』を参照してください。)

新しい仕様では、「タイプ3」/「タイプ4」のPSE/PD(それぞれ60W/90Wに対応可能)、および出力/入力電力の追加クラス(5~8)も導入されました(表1)。設計者は、この修正版がISO/IEC 60950の制限電源および安全超低電圧(SELV)要件(ポートごとの電源を最大100Wに制限)に準拠するよう設計されていることに注意する必要があります。

|

表1: 高電力PoE(IEEE 802.3bt)とPoE(IEEE 802.3af)およびPoE+(IEEE 802.3at)の比較。IEEE 802.3btは、電力の増加、新しいタイプのPSE/PD、および新しいクラスを実現します。(表提供: Microsemi)

IEEE 802.3btがもたらす機能強化

高電力PoEの仕様では、高電力が使用可能になるだけでなく、他の機能も導入されます。主な機能強化には次が含まれます。

- 自動クラス機能

- 低スタンバイ電力サポート

- チャンネル(ケーブル)長が既知である場合の拡張電力機能

自動分類(または「Autoclass」)は、高電力PoE特有の新しい(オプションの)分類メカニズムであり、PDがPSEに対する有効な最大消費電力を通信できるようにします。これにより、PSEはそのレベルと正確に一致する電力バジェット(加えてチャンネル損失および「安全」マージン用のリザーブ)を設定し、システム効率を向上させることができます。

厳格なスタンバイ要件でアプリケーションを強化するために、高電力PoEにはPSEが電力を維持するのに使用される最小パルス電流の持続時間に対する重大な変更が含まれています。以前、タイプ1およびタイプ2のPDは「保持電源シグネチャ」(MPS)を使用していました。これは、325msごとに最低75ミリ秒(ms)にわたる10ミリアンペア(mA)のパルス電流、26.3キロオーム(kΩ)以下のACインピーダンス、0.05マイクロファラッド(μF)で構成されます。IEEE 802.3btの仕様がもたらす変更(タイプ3およびタイプ4 PSEに適用)の結果、パルス持続時間がタイプ1およびタイプ2 PSEの約10パーセントになります。

電力機能の拡張も重要な変更です。PDは、ケーブル抵抗を測定して電力損失を計算し、さらには仕様で詳細に規定された最小入力電力をPDが受けるのに必要な電力リザーブを計算します。最悪の場合、これは以前の修正版で規定された電力リザーブと等しくなりますが、実際のアプリケーションでは低くなる可能性が高く、省エネにつながります。

高電力PoEの起動

PSE出力電力の4つの追加クラス(クラス5~8)、対応するPD入力電力、PSE/PDの2つの新しいタイプ(タイプ3および4)の導入により、このテクノロジの起動シーケンスはますます複雑になりました。これは、高電力PoEシステムを設計する開発者に影響を与え、PSEコントローラの選択を左右する可能性があります。

一般的に、IEEE 802.3afまたはIEEE 802.3atに準拠したデバイスは、タイプ1(クラス0~3)またはタイプ2(クラス4)デバイスと呼ばれます。IEEE 802.3btに準拠したデバイスは、タイプ3(クラス5、6)またはタイプ4(クラス7、8)デバイスと呼ばれます。高電力PoEは、PSEがケーブル経由でPDに電力供給し、PDがケーブルから切断された場合に電源をオフにする安全な方法を定義します。

IEEE 802.3btの機能には、どのタイプまたはクラスのPSEとPD間でも互換性を確保するための突入電流と時間の制限も含まれます。突入制限は、400mA~450mA(クラス0~4)、400mA~900mA(クラス5~6)、800mA~900mA(クラス7~8)です。PSEの突入制限は、パワーアップ後最大75msにわたって適用されます。その後、タイプ2、3、4のPSEは、分類に基づいてより高い出力電流をサポートします。

高電力PoEの起動プロセスは、PSEの電源オフにより開始され、同時にケーブルに何かが接続されていないかを確認します。続いて、PSEはPDを分類してから、PDが要求する電力、またはPSEの最大電力(PDに完全供給するために十分な容量がない場合)を供給します。タイプ3および4のPSEが使用する第4の動作状態もあり、PDの各ツイストペアに同じ分類シグネチャがあるかどうかを確認します。

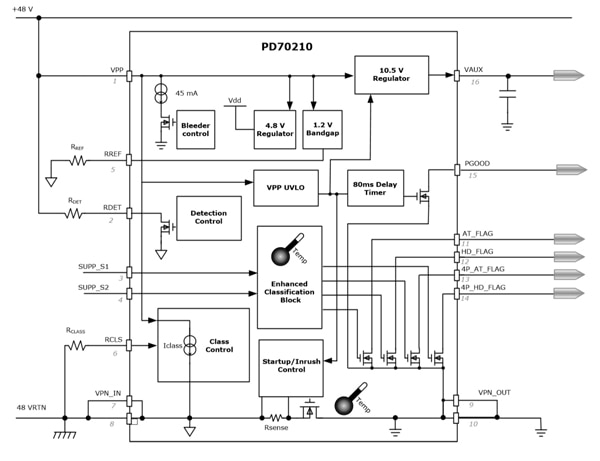

Autoclassはオプション機能であるため、すべての高電力PoE準拠のPSEおよびPDがサポートしているわけではありません。したがって、この機能が開発者のシステムの仕様の一部となっている場合は、データシートを確認する必要があります。MicrosemiのPD70210ILD-TRフロントエンドPDインターフェースコントローラは、「Enhanced Classification Block」によりAutoclassを実行する製品です。また、PD70210ILD-TRは、ケーブルの4つのペアのうちどれが実際に電力供給を受けるかを識別し、適切なフラグを生成します(図1)。

図1: MicrosemiのPD70210ILD-TRフロントエンドPDインターフェースコントローラには、高電力PoEに導入された新しいクラスとPDタイプの分類を簡単にするEnhanced Classification Blockが含まれます。また、このチップは、ケーブルの4つのツイストペアのうちどれが、SUPP_S1およびSUPP_S2ピン経由で実際に電力供給を受けるかを識別します。(画像提供: Microsemi)

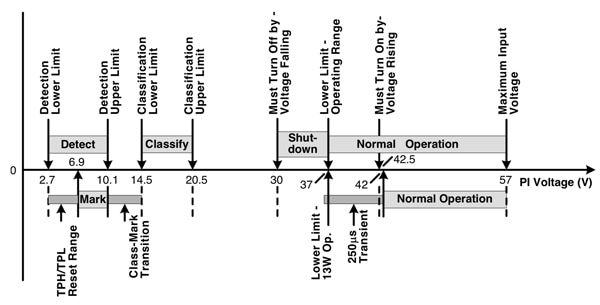

Autoclassを実装するPSEは、最初にPDがこの機能をサポートしているかを確認します。これには、クラス電流が短い遅延の後にクラス0電流レベルになることを確認する方法を使用します。サポートしている場合、PSEは起動直後にAutoclass測定に進むことができます。続く1.35~3.65秒にわたって、PDは最高電力を消費する必要があります。いったん開始すると、PDはMPSを提供して、PDが接続されたままであることをPSEに保証します。MPSの喪失はPSEの電源オフをトリガします(図2)。

図2: 高電力PoEの起動プロセスは、新しいPSEおよびPDのクラスとタイプを導入したため、以前のバージョンよりも複雑です。ここでは、プロセスの3つの主な段階(検出、分類、動作)およびそれらが発生する入力電圧が示されています。(画像提供:Texas Instruments)

高電力PoEの仕様に適合する新しいコントローラ

PoEの承認以降、設計の基盤となる統合PSEコントローラおよびPDインターフェースは豊富に提供されてきました。この傾向は、IEEE 802.3btでも続いています。仕様のドラフトバージョンに適合する製品を設計したメーカーにより、前述のMicrosemiのデバイスに加え、すでに複数のPSEコントローラおよびPDインターフェースが市場で販売されています。

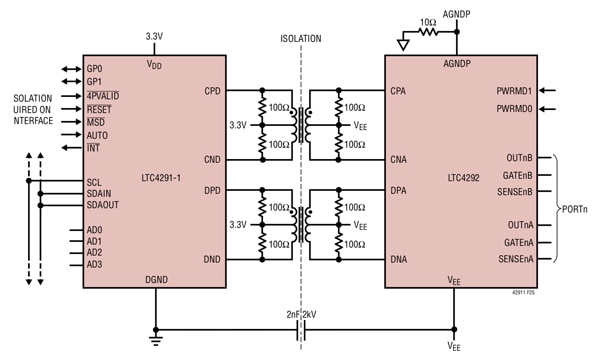

たとえば、Linear TechnologyはLTC4291-1/LTC4292チップセットを提供しています。このコンポーネントは、連携してタイプ3または4のPSEコントローラを構成するために設計されています。電源管理機能には、ポートごとの14ビット電流監視、プログラム可能な電流制限、および事前に選択されたポートのさまざまな手法によるシャットダウンが含まれます。PD検出は、誤ったPD識別を防止するのに役立つ独自のマルチポイント検出機構を使用しています。Autoclassがサポートされ、チップセットはPDで最大71.3WをネゴシエートするようピンまたはI2Cによりプログラム可能です。

LTC4291-1/LTC4292チップセットは、統合のレベルで注目されています。IEEE 802.3bt準拠のPSE設計を実装するのに必要な電気回路がほぼすべて含まれており、追加する必要があるのは数個の周辺機器だけです。このデバイスは、2つのチップ(プロセッサと電源)に分割され、LTC4291-1を非絶縁側に設置することにより、PSEの絶縁を簡素化しています。そこで、主なロジック電源から電力供給を受け、I2C/SMBusバスに直接接続することができます。このチップセットは、チップ間通信において独自の絶縁方式を使用しています。これにより、光アイソレータと絶縁電源を低コストのトランスで置き換えます。これらのトランスは、巻数比1:1、コモンモードチョークの10BASE-Tまたは10/100BASE-Tユニットです(図3)。

図3: Linear TechnologyのLTC4291-1/LTC4292 4ポートIEEE 802.3bt PoE PSEコントローラは、光アイソレータと絶縁電源を低コストのトランスで置き換えることにより設計を簡素化する独自の絶縁を実装します。(画像提供:Linear Technology)

高電力PoEを最大限に活用するために、PDはタイプ3または4のインターフェースを必要とします。それ以外の場合、PSEはIEEE 802.3afにより定義された最大電力15.4W(PDでは12.95W)のみを供給します。このインターフェースのオプションとして、TIのTPS2372-4RGWTがあります。これには、IEEE 802.3btのタイプ1~4のPDインターフェースを実装するのに必要なすべての機能が含まれています。

内部スイッチの低抵抗により、TPS2372-3とTPS2372-4は、それぞれ最大60Wと90Wの高電力PoEアプリケーションをサポートすることができます。また、自動MPS機能により、アプリケーションが必要とするスタンバイモードの消費電力を非常に低く抑えることができます。PDのIEEE 802.3bt MPS要件は、ケーブルのPSE側でも該当することに注意してください。そのため、ケーブル長、およびバルク静電容量などの他のパラメータに応じて、長いMPS持続時間の検証が必要とされる場合があります。その目的のために、TPS2372にはMPSパルス持続時間とデューティサイクルの3つの異なる選択肢があります(MPS_DUTY入力ピンにより選択可能)。

TPS2372は、すべてのPSEタイプと互換性のある突入電流レベルを実装します。また、このチップは遅延機能を実装しており、パワーグッド(PG)出力をリリースする前にPSEが突入フェーズを完了できます。これにより、IEEE 802.3btの起動要件が満たされます。このチップのAutoclassイネーブル入力は、IEEE 802.3bt規格で規定されたすべての高度なシステム電源最適化モードへのアクセスを提供します。

高電力PoEの導入ガイドライン

LTC4291-1/LTC4292のような高度に統合されたチップセットを使用する場合、困難な設計作業の多くはシリコンベンダーによって実行されます。ただし、依然として、外部コンポーネントの選択やプリント基板レイアウトに関するガイドラインを慎重に考慮する必要があります。この大部分はPoEシステム設計の一般設計ガイドラインに従いますが、高電力PoEで導入される高い電圧および電流レベルに適切なコンポーネントの選択は異なります。

たとえば、デジタル電源およびPoE主電源が、図3に表示されているVDDおよびVEEラインで必要です。VDDは3.3ボルト、VEEはタイプ3のPSEで–51~–57ボルト、タイプ4のPSEで–53~–57ボルトの負電圧を必要とします。少なくとも0.1μFのセラミックデカップリングコンデンサをVDDからDGNDへ設置し、実用範囲内で各LTC4291-1にできるだけ近くする必要があります。必要な絶縁を維持するため、LTC4292 AGNDPおよびLTC4291-1 DGNDは接続できません。

VEEは、PDに電力を提供する絶縁型PoE主電源です。比較的多くの電力を供給し、重大な電流過渡の対象になるため、シンプルなロジック電源よりも多くの設計配慮が必要です。最高のシステム効率を実現するには、VEEを最大振幅(57ボルト)付近に設定し、過渡オーバーシュートまたはアンダーシュート、温度ドリフト、およびライン安定化のために十分なだけのマージンを残す必要があります。電気的過渡が発生した場合にスプリアスリセットを最小化するには、AGNDPとVEE間に少なくとも47μFの電解バルクコンデンサが必要です。

外部MOSFETの選択は、開発者にとってもう1つの重要な設計上の決定です。このMOSFETは、PSE出力を制御する電力スイッチングデバイスを形成します。コンポーネントの選択は、システムの信頼性に大きな影響を与えます。また、選択にあたっては、さまざまなPSE電流制限条件に対するMOSFET安全動作領域(SOA)の分析とテストが必要とされます。Linear Technologyは、PDで最大51Wを供給するように設定されたPSE用にNexperia PSMN075-100MSEXを推奨し、PDで71.3Wを供給するように設定されたPSE用にPSMN040-100MSEXを推奨します。これは、PoEアプリケーションにおけるMOSFETの信頼性が実証されているためです。

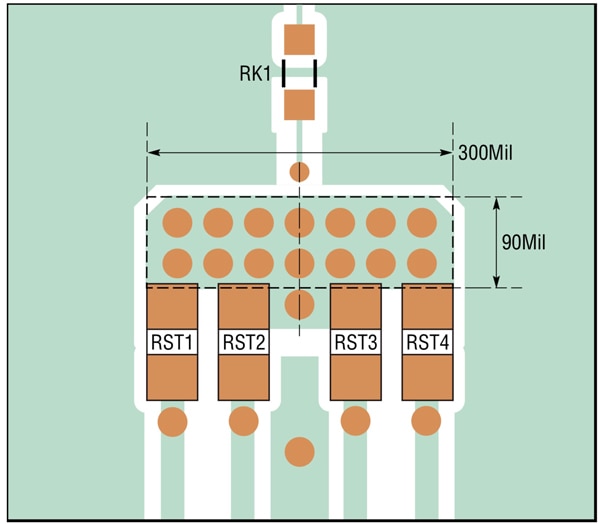

LTC4291-1/LTC4292チップセットは、チャンネルあたり0.15Ωの電流センス抵抗で設計されています。開発者は、図4で示す位置に2つのパラレル0.3Ω抵抗を追加する必要があります。高電力PoEの仕様を満たすために、センス抵抗には±1パーセントまたはそれより優れた許容誤差、±200ppm/°C以下の温度係数が必要です。

図4: LTC4292に必要な表面と裏面レイヤのセンス抵抗のブロックレイアウトを示しています。センス抵抗(RSTx)の選択と配置は、高電力PoEの仕様を満たすために極めて重要です。(画像提供:Linear Technology)

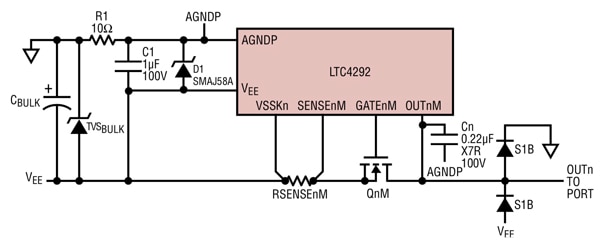

各ポートでは、起動中または過負荷中の電流制限においてLTC4292の安定性を維持するため、OUTnAおよびOUTnBとAGNDP間に0.22μFのコンデンサが必要です(図3を再度参照)。少なくとも100ボルト定格のX7Rセラミックコンデンサが推奨されており、LTC4292の近くに配置する必要があります。

Ethernetポートは、重大な電気的過渡の対象になります。PoEシステムの包括的なサージ保護は別個の記事を必要とする複雑なテーマですが、最小要件は各ポートのサージ電流/電圧を安全なレベルにまで抑制する過渡電圧抑制(TVS)ダイオード(TVSBULK)などのバルク電圧サプレッサおよびバルク静電容量(CBULK)です(図5)。10Ωの直列抵抗(R1)も供給AGNDからLTC4292のAGNDPピンの間で必要とされています。58ボルトのTVSダイオード(D1)をLTC4292のAGNDPピンとVEEピンにわたって配置し、1μF、100ボルトのバイパスコンデンサ(C1)をLTC4292ピンの近くに配置する必要があります。最後に、各ポートは2つのS1Bクランプダイオードを必要とします。1つはOUTnMから供給AGNDの間、もう1つはOUTnMから供給VEEの間に配置します。これらは電気的過渡を電源レールに誘導し、そこで電気的過渡はサージサプレッサにより吸収されます。

図5: PSEコントローラは、電気的過渡からの保護を必要としています。ここに示すのは、Linear TechnologyのLTC4292と、敏感なチップから過渡をそらすのに必要な電圧/電流サプレッサおよびコンポーネントです。(画像提供:Linear Technology)

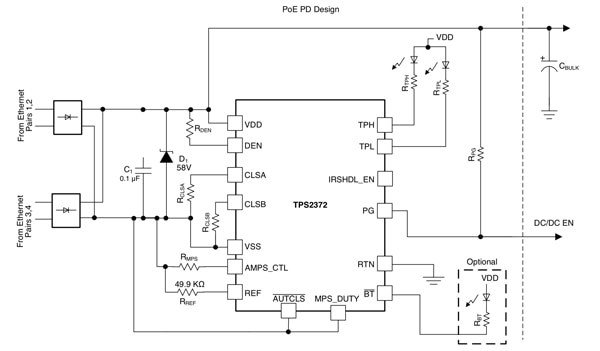

PDインターフェースでは、TIのTPS2327などのチップの高レベルな統合により開発者の作業が容易になりますが、一部の外部コンポーネントも必要になります(図6)。

たとえば、PDインターフェースへのケーブル入力でダイオードが必要です。TPS2327の場合、TIは高電力PoEアプリケーションに、従来のダイオードではなく3~5アンペア、100ボルト定格ディスクリートまたはブリッジショットキーダイオードを推奨しています。これにより、ダイオードの消費電力が30パーセント低減します。開発者が考慮すべき点として、ショットキーダイオードでは通常のPN接合ダイオードよりも高い逆リーク電流がしばしば発生します。これにより、仕様で定義された2.8ボルトの最大逆給電電圧を満たすのが困難になります。補償するために、この実装では控えめのダイオード動作温度制限と低リークデバイスを使用する必要があります。また、ショットキーダイオードは従来のダイオードよりも電気的過渡の影響を受けやすいため、フェライトビーズおよびコンデンサ形式の電圧/電流保護をお勧めします。

IEEE 802.3btの仕様には、VDDからVSS全体にわたって0.05~0.12μFの入力バイパスコンデンサが含まれます(標準0.1μF、100ボルト、±10%セラミック)。この仕様には、検出抵抗、RDEN、分類抵抗RCLSAおよびRCLSB、およびMPS抵抗RMPSも必要です。RDENには、24.9kΩ、±1%の抵抗が推奨されています。分類抵抗はCLSA/CLSBからVSSに接続し、IEEE 802.3bt規格に従って分類電流をプログラムします。これらの抵抗の値と割り当てられるクラス電力は、動作中にPDから供給される最大平均電力により決定されます。RMPSは、MPSのデューティサイクルを設定します。たとえば、1.3kΩの抵抗は26.4%のデューティサイクルを設定します。MPS_DUTYをRSSに短絡することにより、デューティサイクルを12.5%に設定します。

高電力PoE PDインターフェースには、電源ライン全体にわたってTVSダイオードおよびバルクコンデンサ(D1、CBULK)の電圧抑制も必要です。これにより、ケーブルのこちら側の電気的過渡を吸収します。

図6: TIのTPS2372高電力PoE PDインターフェースのアプリケーション図は、設計を完成させるのに必要なペリフェラルコンポーネント(主に入力ダイオード、抑制デバイス、および検出/分類/MPS抵抗)を示しています。(画像提供:Texas Instruments)

プリント基板レイアウト/部品配置/ルーティング要件がパラメトリック測定精度、システムの堅牢性、および熱放散におけるIEEE 802.3bt仕様の要件を確実に満たせるようにするため、多くの設計ガイドラインが用意されています。Linear TechnologyとTIの両社は、仕様に準拠したPSE/PDインターフェースのリファレンス設計や開発者にとって役立つ指針を提供しています。

まとめ

高電力PoEはPoEのアプリケーションを拡張し、効率を向上させます。ただし、PSEコントローラおよびPDインターフェースのタイプやクラスのさらなる導入、動作および安全機能の追加により、実装がより複雑になりました。

設計者を支援するために、これらの機能を標準として含む統合PSEコントローラおよびPDインターフェースソリューションが提供されています。これにより、システムを完成させるのに必要なペリフェラルコンポーネントの数を削減し、設計プロセスが大幅に簡素化および高速化されます。

免責条項:このウェブサイト上で、さまざまな著者および/またはフォーラム参加者によって表明された意見、信念や視点は、DigiKeyの意見、信念および視点またはDigiKeyの公式な方針を必ずしも反映するものではありません。