ポイントオブロードパワー変換の新認識

あらゆるシステムアーキテクトへの質問:「あなたの抱えている最大の問題は?」考えられる答えは、システムに電源を供給するためのデバイスが基板スペースの30~50%を占めており、さらにフィルタリングや電磁妨害(EMI)抑制のための部品も必要になるというものです。コンシューマアプリケーションからデータセンタやネットワーク製品に至るまで、ほとんどの電子システムにおいて、電源は小型化・薄型化の大きな制約の1つとなっています。

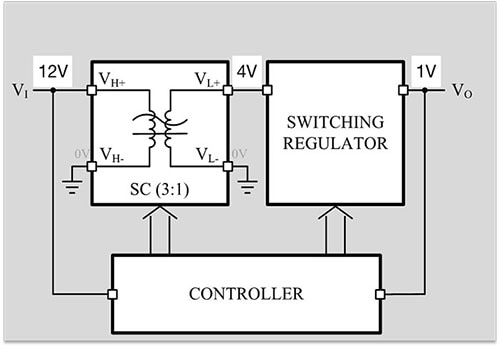

図1:Murataの2段降圧型アーキテクチャは、チャージポンプおよび降圧スイッチングレギュレータを搭載しています。(画像提供:Murata)

図1:Murataの2段降圧型アーキテクチャは、チャージポンプおよび降圧スイッチングレギュレータを搭載しています。(画像提供:Murata)

従来、システムアーキテクトは、コアプロセッサやアプリケーションプロセッサ、システムASIC、メモリなどのシステム負荷に電力を供給するために、12Vなどのバスレールから電流をステップダウンするポイントオブロード(POL)降圧コンバータに依存していました。降圧コンバージョンは、数十年にわたって産業に貢献してきましたが、堅牢でコスト効率の良いソリューションを形成するために改良と改善が重ねられてきました。しかし、本当の意味で電力密度を向上させるには、システムアーキテクトは単なる反復的な改善を超えて考える必要があります。そこで、Murataでは図1に示すように、チャージポンプと降圧スイッチングレギュレータの2段構成のPOLコンバータを開発しました。

多くの人にとって、2段階のアーキテクチャが効率を向上させるという考えは、個々のステージの効率が掛け合わされるため、直観的ではないかもしれません。しかし、革新的なスイッチドキャパシタ技術により、チャージポンプは実質的に無損失となり、最初の変換ステージで非常に高い効率を実現します。

図1に示すような12Vinから1Voutという標準的な例を考えると、チャージポンプはコンデンサを使用して、入力電圧を12Vから4Vへと3分の1にしています。2段目の降圧インダクタは、4Vから1Vの負荷への最終的な変換において、より少ない仕事をしていることになります。コンデンサはインダクタに比べて約400倍のエネルギー密度を持っているため、コンデンサを使用することが重要なポイントです。容量性ストレージに依存するソリューションは、本質的に高い電力密度をもたらします。これで、2段目の降圧レギュレータは、12Vの入力電圧ではなく、4Vの低い入力電圧で動作するようになりました。これにより、低電圧・高効率の電界効果トランジスタ(FET)を使用し、小型の出力インダクタと組み合わせることで、非常に高い周波数で高速過渡応答が可能な高効率の降圧レギュレータを実現しています。

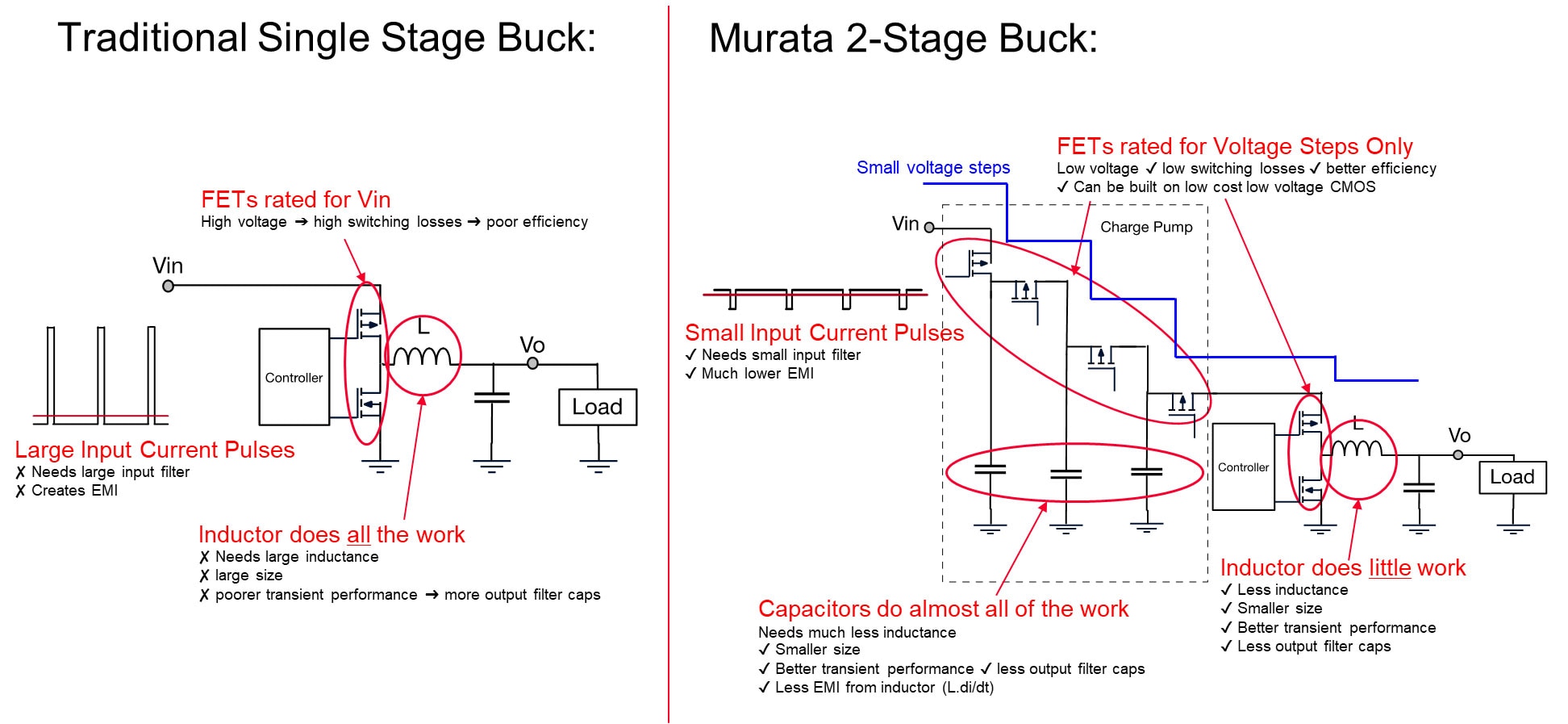

図2は、従来の1段降圧型と2段降圧型アーキテクチャの比較を示したものです。

図2:従来の1段降圧コンバータとMurataの2段降圧コンバータの比較。(画像提供:Murata)

図2:従来の1段降圧コンバータとMurataの2段降圧コンバータの比較。(画像提供:Murata)

12Vinから1Voutのシナリオで、図2に示すより伝統的な1段階の降圧アプローチを考えてみましょう。Vxノード(FETの中間点)では、グランドからVinへの揺らぎに加え、リークインダクタンスや寄生素子に蓄えられたエネルギースパイクがあります。この方法では、より高電圧のFETが必要となり、急激な電圧変化やリンギングによる電磁干渉(EMI)が問題となる可能性があります。インダクタがすべての作業をしており、比較的高い負荷であるため、効率と過渡応答に悪影響を及ぼします。さらに、12:1Vのシナリオでは、ハイサイドFETは1/12の時間しか導通していません。 そのため、入力に非常に大きなパルス電流が流れることとなり、伝導EMIへの影響を抑えるために追加のデカップリングが必要になります。また、このような低デューティサイクルの動作は、非常に高いスイッチング周波数で動作する能力を制限します。

この方法は、図2に示すMurataの2段式実装とは対照的です。この例において、チャージポンプは電圧を12V→8V→4Vのように整数のステップで下げていくため、各段の電圧は4Vで済み、低電圧・高効率のFET技術を利用することができます。降圧レギュレータは、4:1Vという変換の最後のステップを実行します。ほとんどの作業は、1段の容量性チャージポンプによってすでに行われています。このアーキテクチャによって2段目のインダクタを減らすことができ、その結果、優れた過渡応答を備え高周波数で動作する、小型で薄型の設計が可能になります。

初段のチャージポンプは、50%のデューティサイクルで位相差がある2つのフェーズとして実装されています。2段目の降圧は、より25%に近いデューティサイクルで動作し、入力電流や脈動電流を低減します。この2つの要素が相まって、コンバータの入力リップルとEMIプロファイルを最小限に抑えることができます。以上のことから、Murataの2段式アーキテクチャは、効率、サイズとプロファイル、そして電磁干渉(EMI)を改善することがわかります。

詳細は、Murataのウェビナー「Murataはどのように電力密度のパラダイムを変えているか」をご覧ください。

Have questions or comments? Continue the conversation on TechForum, Digi-Key's online community and technical resource.

Visit TechForum