高分解能の高速A/D変換にデジタルフィルタを使用する理由と方法

2021-03-17

まだまだアナログの世界ですが、デジタル電子機器が普及しているのには理由があります。デジタルはアルゴリズムアプローチによって複数の問題を解決しますが、どんなに優れたデジタルアルゴリズムであっても、アナログ領域に存在する実世界のエンティティを扱う点に短所があります。これは、計測器、モータ制御、データ収集システムなど、高速かつ高分解能のデータ収集を必要とするアプリケーションで特に顕著です。

このような実世界の信号をキャプチャおよび処理しようとする設計者にとって問題となるのは、その信号情報を損なうことなく、できるだけ早くデジタル領域に移行する必要があることです。その解決策は、フロントエンドのアナログローパスフィルタ(LPF)を使用したシンプルな平均化アルゴリズム(ノイズの低減)から始まります。このような技術により、適切なデバイスを使用してオンボードのアナログおよびデジタルフィルタリングによる高分解能の高速変換を提供することができます。

この記事では、アナログLPFと平均化デジタルフィルタを使用した逐次比較レジスタ(SAR)A/Dコンバータ (ADC)で高分解能の高速変換を実現する際の問題点と、このフィルタの組み合わせがほとんどのアプリケーションに適している理由について簡単に説明します。次に、Analog DevicesのAD7606C-18 8チャンネルSAR ADCを紹介し、1メガサンプル/秒(MSPS)の変換レート、同時サンプリングコンバータアレイ、および柔軟なデジタルフィルタ機能を活用する方法を示します。

この記事では、最高の全体性能を実現する方法を示すために、AD7606C-18と、同じくAnalog Devicesが提供するADR4525超低ノイズ高精度電圧リファレンスを組み合わせて、18ビット変換に必要なSARの精度を高めています。

アナログフィルタ対デジタルフィルタ

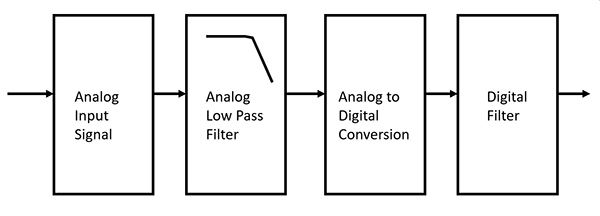

アナログ技術者とデジタル技術者がフィルタの話をすると、デジタル技術者はアナログを否定するかもしれません。これは間違いです。アナログ/デジタル(A/D)変換時のフィルタリングの基準は、デジタルフィルタの前にアナログLPFを置くことです(図1)。

図1:デジタルフィルタの前にアナログフィルタを配置したアナログ/デジタル信号チェーンのブロック図。(画像提供:DigiKey)

図1:デジタルフィルタの前にアナログフィルタを配置したアナログ/デジタル信号チェーンのブロック図。(画像提供:DigiKey)

アナログLPFで対象となる帯域幅以上の高周波を減衰させた後、ADCで信号をデジタルワードに変換します。これにより、デジタルフィルタは、対象となる帯域幅内の信号に対して動作することができます。

データ収集環境におけるアナログフィルタ

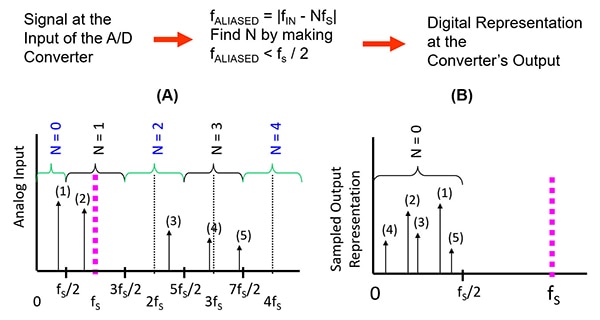

アナログLPFの重要性は、ADCの出力で明らかになります。ADCを通過するすべての信号には、大きさと周波数が関連付けられています。ADCの出力では、信号の周波数がADCの入力帯域幅以下であれば、信号の大きさは確実に同じままとなります。A/D変換では信号の大きさが保たれますが、信号の周波数については同様ではありません。ADCのサンプリング周波数fS(ナイキストサンプリングレートとも呼ばれる)の1/2以上の周波数で変化が見られます(図2)。

図2:グラフ(A)では、入力信号の高速フーリエ変換(FFT)表現に5つの周波数成分があります。A/D変換後、グラフ(B)のFFT表現では、5つの信号すべてがADCのサンプリング周波数(fS)の半分以下で発生しています。(画像提供:DigiKey)

図2:グラフ(A)では、入力信号の高速フーリエ変換(FFT)表現に5つの周波数成分があります。A/D変換後、グラフ(B)のFFT表現では、5つの信号すべてがADCのサンプリング周波数(fS)の半分以下で発生しています。(画像提供:DigiKey)

図2では、両方のFFTプロットで、X軸に対数周波数、Y軸にリニア電圧または大きさを使用します。グラフ(A)では、アナログ信号のFFT表現が、ADCのサンプリング周波数の半分(fS/2)以上の信号やノイズが複数存在するADCの入力信号を示しています。

この2つのグラフを比較すると、5つのFFT信号を追うのに役立ちます。ADC変換後、元の信号の大きさは変わりませんが、(A)のサンプリング周波数の半分以上の周波数が、(B)のfS/2以下に「反転」しています。この現象は、信号のエイリアシングとして知られています。信号を正確に取得するために、ADCのサンプリングレートfSは、fMAXの2倍以上にする必要があります。fMAXは、シャノン-ナイキストのサンプリング定理に基づき、信号の使用可能な帯域幅に相当します。

ADCがデジタル出力信号に不要なノイズや信号をどのように恒常的に埋め込んでいるかを確認できます。この変化により、コンバータの出力では、帯域内の信号と帯域外の信号の区別がつかなくなります。

これら2つのFFT表現間を行き来する経路があると予想されるかもしれません。しかし、一度このような変化が起きてしまうと、後戻りして元に戻すことはできません。残念ながら、数学はこのような前後の遷移をサポートしていません。

アナログ/デジタルの話に戻りますが、デジタルフィルタは、平均化、有限インパルス応答(FIR)または無限インパルス応答(IIR)のフィルタリングを適用して、間違いなくシステムノイズを低減することができます。しかし、すべてのデジタルフィルタは、かなりの量のオーバーサンプリング(最終的な出力データレートよりも大幅に高いサンプリング周波数で信号をサンプリングするプロセス)を必要とします。これには時間と電力がかかり、ADCのサンプリング速度も低下します。デジタルフィルタやコンバータ機能では、エイリアス信号の現象を克服することはできません。基本的なアナログ1次LPFであっても、最初から高周波数のノイズを単純に低減するのが最善です。

平均化デジタルフィルタ

SAR ADCは、平均化デジタルフィルタによってDCノイズの測定を改善します。平均化デジタルフィルタは、複数の変換を一定の時間軸で取得してビット数を増やします。ADCのユーザーは、コントローラ、プロセッサ、または複数のコンバータサンプルをキャプチャするオンチップ平均化エンジンで平均化アルゴリズムを使用します。平均化処理は、変換グループを「平滑化 」し、システムノイズの低減により有効分解能を向上させます。

変換データの平滑化を実装する際は、一定のサンプルレートで複数回の信号取得を行うことや、所定のサンプル数を平均化することが関係します。平均化のプロセスはよく知られています。ADCの結果(連続したサンプル、x)をサンプル数(N)で割ったものを合計すると、平均値が得られます(式1)。

![]() 式1

式1

このプロセスにより、出力データレートは1/Nになりますが、システムのセトリング時間は長くなります。

平均化されたノイズサンプルの標準偏差(σavg)は、元の信号の標準偏差(σsig)をNの平方根で割ったものです(式2)。

![]() 式2

式2

無相関のノイズを含む連続したサンプルは、一定の信号平均でより多くのノイズを低減することになります。連続したサンプルを平均化するたびに、信号がDCでノイズ成分がランダムであれば、SNR(信号対ノイズ比)が向上します。

SNRの向上は、平均化されたサンプル数の平方根に比例します。4つのDC信号サンプル(41)の平均では、SNRを6デシベル(dB)増加させることで、コンバータの有効分解能を1つ増加させます。16または42サンプル平均では、有効分解能が2倍になり、SNRが12dB増加します。この論理では、グループサイズを4Nにすると、変換による有効ビット数がN増加し、システムノイズがゼロになり、SNR値が無限大になります。

アラン分散

もちろん、SNR値が無限大というのは不条理です。実世界では、必要な数のサンプルを取得するのに時間がかかり、その間にシステムがドリフトの度合いで変化してしまうことがあります。

2サンプル分散とも呼ばれるアラン分散は、信号の平均化に使用するサンプル数の増加に伴うノイズの変化を示すことで、クロック、オシレータ、ADC、アンプなどの周波数安定性を測定します。アラン分散統計解析ツールは、特定のシステムに最適な最大必要サンプル数を決定し、周波数ドリフトや温度効果を指摘することで安定性を推定します。

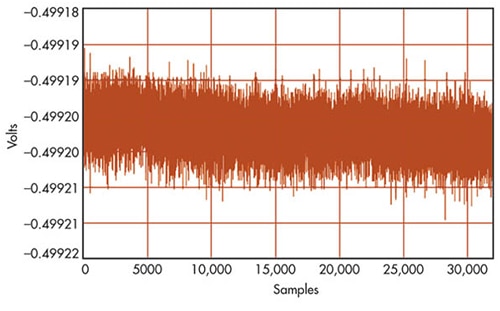

たとえば、ADCからのシステム内データの経時変化は、図3のようなシフトを示します。

図3:9分間にわたってキャプチャされた30,000個のADC出力データポイントでは、その期間にデータがわずかにドリフトし、アラン分散の計算が低下しています。(画像提供:Electronic Design)

図3:9分間にわたってキャプチャされた30,000個のADC出力データポイントでは、その期間にデータがわずかにドリフトし、アラン分散の計算が低下しています。(画像提供:Electronic Design)

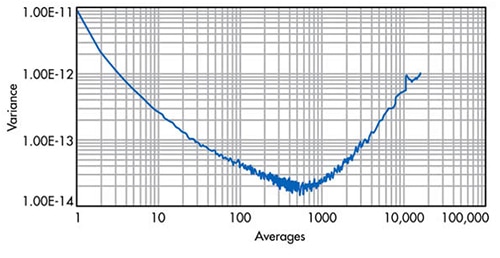

分散アルゴリズムは、より長い平均値の複数のバッチを取り、各バッチの結果としてのノイズを評価します(図4)。

図4:図3のデータポイントにアラン分散の計算を適用したもの。500ポイントの平均値では、この特定のADCシステムが4.48ビットを取得し、27dBのSNR向上を実現しています。(画像提供:Electronic Design)

図4:図3のデータポイントにアラン分散の計算を適用したもの。500ポイントの平均値では、この特定のADCシステムが4.48ビットを取得し、27dBのSNR向上を実現しています。(画像提供:Electronic Design)

図4は、この特定のシステムのデータポイントの分散が最小になるのが、ノイズの低減に最適なサンプル平均数である約500回のADC出力平均であることを示しています。500ポイントの平均値では、このADCシステムが4.48ビットを取得し、27dBのSNR向上を実現しています。図4では、500回目の平均ポイントの前後で、データドリフトの影響が大きな要因となり、結果が悪化しています。アラン分散の計算に影響を与える変数としては、時間、信号の安定性、ドリフト、電源の変動、製品の経年変化などがあります。デジタル平均化フィルタを使用している場合は、アラン分散ツールでシステム全体を評価するのが賢明です。

実世界のソリューション

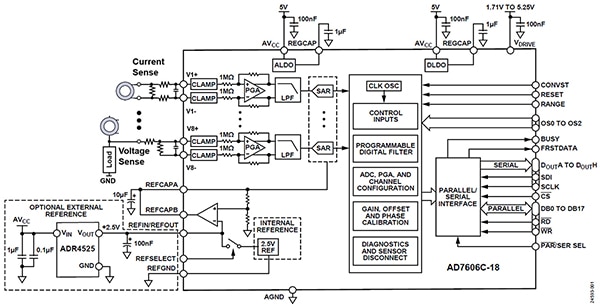

SARコンバータは、プログラマブルゲインアンプ(PGA)やデジタルフィルタ機能を備えており、有効分解能と最下位ビット(LSB)電圧を高めることができます。たとえば、Analog DevicesのAD7606C-18は、8チャンネルを備えた18ビット、1MSPS、同時サンプリングのA/Dデータ収集システム(DAS)です。各チャンネルには、アナログ入力クランプ保護、PGA、LPF、18ビットSAR ADCが搭載されています。

また、入力インピーダンスが1メガオームのアナログ入力バッファと、プログラム可能な真のバイポーラ差動、バイポーラシングルエンド、およびユニポーラシングルエンドの入力電圧構成を備えています。AD7606C-18は、8つの独立した入力センサまたは信号チャネルを接続することができます。

AD7606C-18のデジタルフィルタは、1から256(44)までの繰り返しのサンプルを平均化するオーバーサンプリングモードを備えています。アラン分散ツールでは、このオーバーサンプリング機能により、コンバータのデジタル出力のノイズ性能が向上します。ADR4525の低ノイズ、2.5Vの精密電圧リファレンスは、AD7606C-18 DASシステムを補完し、最大温度係数は1ppm/℃で、ピーク-ピークの標準出力ノイズは1マイクロボルトです(図5)。

図5:ADR4525 2.5V精密電圧リファレンスを備えたAD7606C-18 SAR-ADC。V1~V8の入力チャンネルの1次LPFを備えたインダクタは、8つすべてのチャンネルを同時にサンプリングします。(画像提供:Analog Devices)

図5:ADR4525 2.5V精密電圧リファレンスを備えたAD7606C-18 SAR-ADC。V1~V8の入力チャンネルの1次LPFを備えたインダクタは、8つすべてのチャンネルを同時にサンプリングします。(画像提供:Analog Devices)

図5に示すように、このような高入力インピーダンスのSARアレイは、一般的な外付け駆動アンプを必要とせず、センサと直接インターフェース接続することができます。また、外付けのセンサゲイン段も不要となります。同時に、SARコンバータには信号処理を行うPGAとLPFのステージが内蔵されており、平均化デジタルフィルタを使用することで、より高い有効分解能を実現し、ノイズをさらに低減します。このようなDASは、17.1ビットの有効分解能と、3.9キロサンプル/秒(ksps)の変換速度を実現します。変換速度スペクトルの他方の端にあるこのデバイスは、変換速度1MSPSで15ビットの有効分解能を提供します。

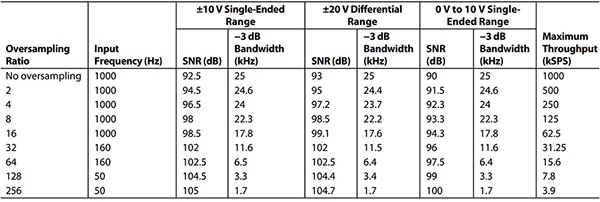

オーバーサンプリングが1に等しい場合、AD7606C-18の最大変換速度は1MSPSです。コンバータのチャンネルオーバーサンプリングが2の場合、またはチャンネルのサンプルを2回平均化する場合、変換速度は最大変換速度の半分の500kspsになります。オーバーサンプリングが4、または平均化したサンプル数が41の場合、そのチャンネルの変換速度は250kspsというようになります。8つの各チャンネルにおいて、オーバーサンプリング値が256のシステムでは、±10ボルトのシングルエンドレンジ、17.1ビットの有効分解能(105dBのSNR)、3.9kspsの変換速度を提供します(表1)。

表1:AD7606C-18のオーバーサンプリング性能、低帯域幅モードの表。(表提供:Analog Devices)

表1:AD7606C-18のオーバーサンプリング性能、低帯域幅モードの表。(表提供:Analog Devices)

SNRから有効分解能(有効ビット数またはENOB)への変換式を、式3に示します。

![]() 式3

式3

変換速度スペクトルの他方の端にあるこのデバイスは、1倍のオーバーサンプリングを備えており、変換速度1MSPSで15ビットの有効分解能(92.5dBのSNR)を提供します(表1)。

AD7606C-18には、さらなる改良が加えられています。8個の独立したオンチップSAR ADCがあるため、8チャンネルすべてが同時サンプリング機能を持ちます。この機能により、高分解能や高速性を実現するためのデジタルフィルタを全チャンネルに同時実装することが可能です。さらに、すべてのチャンネルに較正および診断機能があります。

たとえば、AD7606C-18のシステム位相較正では、ディスクリート入力フィルタの不整合を感知します。この貴重な機能により、同時にサンプリングされたチャンネル間の位相不整合を引き起こす原因となる、ディスクリート部品や使用センサの不整合を特定することができます。本デバイスのソフトウェアモードでは、チャンネルごとにサンプリングのタイミングを遅らせることで、位相不整合をチャンネル単位で補償します。

システムゲインの較正では、ディスクリート入力フィルタの抵抗の不整合を感知します。この機能は、外付け抵抗の不整合を克服するのに役立ちます。ソフトウェアモードでは、対応するレジスタに使用する直列抵抗の値を書き込むことで、チャネルごとにゲイン誤差を補償します。

システムオフセット較正は、較正作業中の入力信号のオフセットに対応するものです。ソフトウェアは、各チャンネルの外部センサのオフセットや、外付け抵抗ペアの不整合のオフセットを調整することができます。

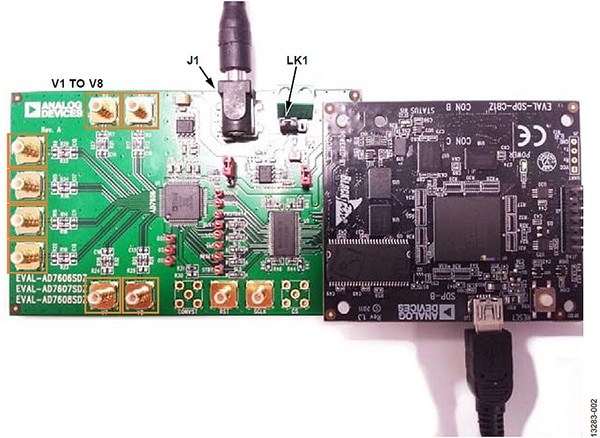

特定のアプリケーション向けに、AD7606用のEVAL-AD7606SDZボードには、デバイスプログラミングのほか、波形、ヒストグラム、FFTキャプチャなどによるデバイス評価を支援するソフトウェアが搭載されています(図6)。

図6:システムデモンストレーションプラットフォーム(SDP)ボード(右)に接続されたAD7606評価ボード(左)。これにより、PCのUSBポートから評価ボードを制御することができます。(画像提供:Analog Devices)

図6:システムデモンストレーションプラットフォーム(SDP)ボード(右)に接続されたAD7606評価ボード(左)。これにより、PCのUSBポートから評価ボードを制御することができます。(画像提供:Analog Devices)

評価ボードのソフトウェアにより、ユーザーは各チャンネルのオーバーサンプリング値、入力範囲、サンプル数、アクティブチャンネルの選択などを設定することができます。また、このソフトウェアでは、テストデータのファイルを保存したり、開いたりすることも可能です。

結論

デジタル化が進んでいるとはいえ、まだまだアナログの世界であり、設計者は高分解能、高速変換の問題を解決するためにアナログ中心の電子機器を必要としています。このように、アナログLPFとデジタル平均化フィルタをシンプルに組み合わせ、適切な数の平均化されたサンプルを実装することで、1MSPS SARコンバータの性能を大幅に向上させることができます。

免責条項:このウェブサイト上で、さまざまな著者および/またはフォーラム参加者によって表明された意見、信念や視点は、DigiKeyの意見、信念および視点またはDigiKeyの公式な方針を必ずしも反映するものではありません。