すぐに利用可能なコンポーネントを使用した疑似ランダム2進数シーケンスとホワイトノイズの生成の生成

DigiKeyの北米担当編集者の提供

2018-03-22

ノイズのような不規則な信号は問題と見られがちですが、その独自の特性により、ランダムなビットシーケンスとノイズによって変化する通信や機器のテストなどの用途があります。ただし、1回限りのテストや予算の厳しい設計者の場合は、専用の疑似ランダム2進数シーケンス(PRBS)または任意波形発生器を購入できない場合があります。このような場合は、すぐに利用可能なCMOS機器を使用して構築した方がコスト効率が良くなります。

この記事では、電子機器でのPRBSとノイズの有益な役割について説明します。その後、すぐに利用可能なCMOS ICについて紹介し、CMOS ICを使用して必要な疑似ランダムノイズと2進数シーケンスを生成する方法を説明します。

「良い」ノイズの役割

ホワイト(ランダム)ノイズでは、周波数領域に平坦なスペクトラムがあります。ホワイトノイズ源によって励起されたアンプまたはフィルタの平均化された出力振幅スペクトラムにより、その機器の振幅周波数応答が与えられます。

通信では、CDMAトランスのデータストリームは疑似ランダム2進数シーケンス(PRBS)で乗算されます。これは複数の他の信号と同じRFチャンネル上で送信できます。コンポジット信号を受信側の同じPRBSと関連付けると、ほとんどまたは全く干渉なしで元のデータストリームが抽出されます。これらのランダム信号が非常に有用な場合においては、必要に応じて信号を生成できることが重要です。

PRBSの生成

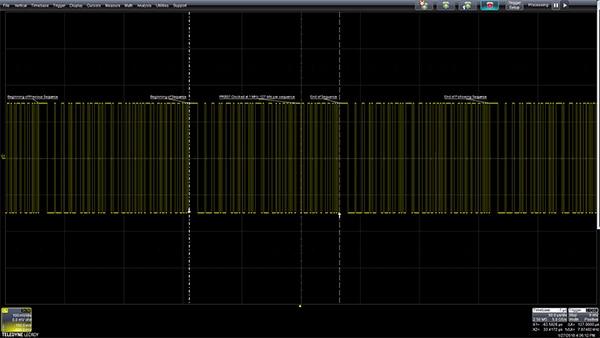

PRBSは、一連のデジタル1と0で構成される断続的な決定論的信号です。1または0レベルの持続時間は、PRBS発生器のクロック周期の倍数です。1と0のパターンは、発生器のパターン繰り返し周期内でランダムです(図1)。

図1:PRBS7信号は、27 – 1(127ビット)の周期を持つ7ビット長のPRBSテスト信号です。この信号は1MHzで記録され、オシロスコープカーソルでマークされているように127ミリ秒の周期性を示しています。(画像提供:DigiKey)

図1の信号は、各パターン周期内に127ビットが含まれる7つのステージを含む発生器により生成されたPRBS7テスト信号です。各周期内のビットパターンはランダムですが、シーケンス全体は127クロック周期ごとに同様に繰り返されます。

これらのテスト信号はソフトウェアまたはハードウェアで生成できます。テストのハードウェア実装の利点は、信号を外部で使用してテストしている機器を操作できることです。

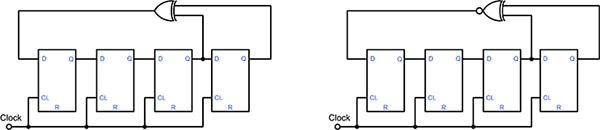

線形帰還シフトレジスタ

PRBSのハードウェア実装には、線形帰還シフトレジスタ(LFSR)を使用します。一部のシフトレジスタは、EXCLUSIVE-OR/NORゲートを使用して後半のステージから入力への帰還と直列に配置されます。使用されるシフトレジスタの数は、パターンの長さまたは持続時間を決定します(図2)。

図2:排他ORと排他NOR帰還ロジックの両方を使って実装された4ビットLFSRの例。帰還タップによって、データ状態のシーケンスが決まります。(画像提供:DigiKey)

多くの帰還設定が可能ですが、ほぼすべてのデザインで、最大長のシーケンスを生成するタップを使用し、状態の合計数が(2N-1)になるようにします。ここでNはシフトレジスタのステージ数です。表1に、LFSRの長さ(2~32)最長シーケンスに対応するタップの概要を示します。これらのタップは排他的ではありません。どのシフトレジスタの長さでも複数の最長多項式が存在する可能性があります。

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

表1:2~32のLFSRの長さの最長シーケンスに対応するタップの概要。(画像提供:DigiKey)

この例では、長さ32,767ビットのランダムなシーケンスを生成する15ステージのLFSR(PRBS15テストシーケンス)を使用します。さらにシーケンスを長くするには、ステージ数の大きいLFSRを使用します。PRBSテストシーケンスの使用制限は、テストの時間です。500kHzで記録される15ビットシーケンスでは65ミリ秒かかります。31ビットのシーケンスでは4,295秒(72分)かかります。

図2の例では、4つのシフトレジスタを使用して、15の異なる状態のデータパターンを生成しています。どちらの設定にも、1つの禁止状態があります。排他OR帰還モデルの場合、一度ロードされたシフトレジスタはその状態で固定されるため、すべて0の状態は使用されません。同様に、排他NOR実装ではすべて1の状態が禁止されます。表2と表3は、ステージ3と4の帰還タップを使用した4ビットLFSRの両方の設定のデータパターンを示しています。

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

表2と3:図1に示したORおよびNOR設定のデータパターン。(画像提供:DigiKey)

どちらの実装も既知の状態、つまりORの場合はすべて1、NORの場合はすべて0から開始されます。これら4ビットの最長LFSRは、表に示すように15の可能な状態(2N-1)を提供します。

出力データパターンは周期的で、15クロックの後に繰り返されます。このパターンは、特定の設定や既知の開始状態の場合、出力が予測できるという点において、決定論的でもあります。ただし、出力パターンは15カウント周期内ではランダムです。

疑似ランダム2進数シーケンス発生器の設計

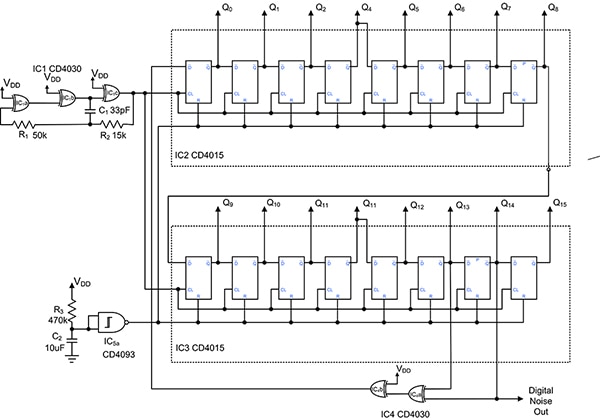

Texas Instruments CD4015BM96デュアルクワッドスタティックシフトレジスタとCD4030BM96クワッドXORゲートを使用したLFSR実装に基づく実際の低コストのPRBS発生器設計を図3に示します。

図3:Texas Instruments CD4015BM96デュアルクワッドスタティックシフトレジスタとCD4030BM96クワッドXORゲートを使用したPRBS15発生器の簡略化した回路図。(画像提供:DigiKey)

この発生器では、PRBS15データパターンを生成する14番目と15番目の帰還タップを含む16のDタイプフリップフロップ(ICあたり8個)を使用しています。 帰還接続はXORゲートを通じて行われ、XORゲートは反転されてXNORに設定されたLFSRが作成されます。このデータパターンの長さは、500kHzクロックレートで約62ミリ秒の時間を表す32,767ビットです。帰還タップの適切な変更を行った長いシフトレジスタを使用してさらに長いパターンを実現できます。設計を31ビットパターンに拡張すると、パターン時間は20億を超える状態(500kHzのクロック周波数で約72分)まで長くなります。

発生器は、CD4093BM96シュミットトリガNANDゲート(IC5)とシンプルなRCネットワークを使って電源投入時にすべて0の状態に初期化されます。クロックは500kHz近くで動作するシンプルなCMOS発振器によって提供されます。デジタル出力はいずれかのシフトレジスタQ出力から取得できます。この例では、Q14が使用されています。

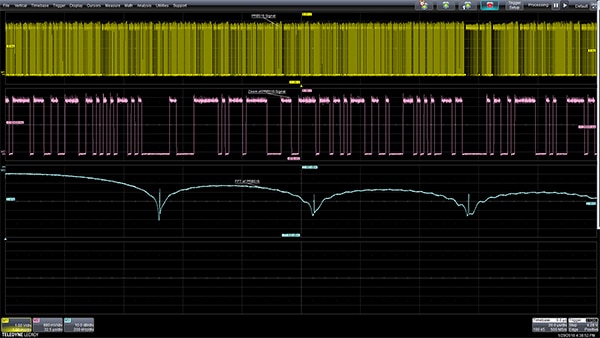

図4には、出力の高速フーリエ変換(FFT)とともに発生器の出力がオシロスコープに表示されています。

図4:発生器の出力(上のトレース)は中央のトレースに水平に展開され、詳細な構造が表示されます。発生器出力(下のトレース)のFFTには、スペクトラムがクロックレートの10分の1を下回ると平坦になることが示されています。 (画像提供:DigiKey)

デジタルノイズのFFTは、クロック周波数の倍数におけるゼロのパルス波形の予想sin(x)/x応答を示しています。スペクトラムは、クロック周波数の約10%で完全に平坦になります。これは、ローパスフィルタリングを使用してデジタル出力からホワイトノイズを抽出する際に重要です。

ホワイトノイズ発生器

ホワイトノイズは、周波数範囲においてスペクトル的に平坦な状態になるノイズです。電力スペクトル密度とユニット帯域幅あたりの電力は、ノイズ帯域幅で一定です。PRBS発生器では、デジタルノイズ出力をフィルタして、ホワイトノイズを生成します。

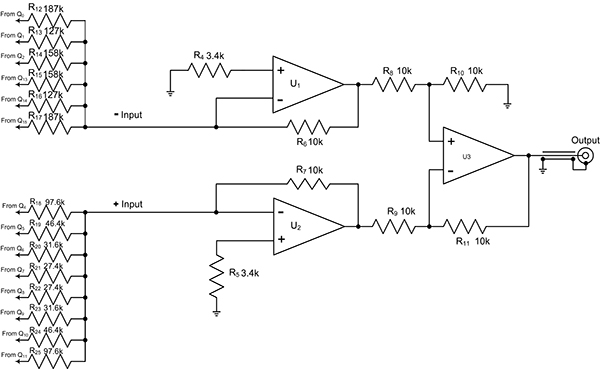

アナログフィルタを使用できますが、特定のクロック周波数に制限されます。有限インパルス応答(FIR)ローパスデジタルフィルタを使用して、フィルタカットオフはクロック周波数のすべての変化を追跡します。また、FIRフィルタは、アナログフィルタに非常に大型のコンデンサを必要とする非常に低いカットオフ周波数を提供できます。FIRフィルタは、シフトレジスタ出力の加重和を結合します。周波数領域で長方形のローパスフィルタ応答を生成するために必要な加重は、時間領域のsin(x)/xです(図5)。

図5:発生器の出力ステージでは、シフトレジスタ出力のsin(x)/x加重サンプルを使って、FIRローパスフィルタを実装します。sin(x)/x加重には負の項が必要であるため、正および負の加重コンポーネントの両方を差動アンプを使って合計します。(画像提供:DigiKey)

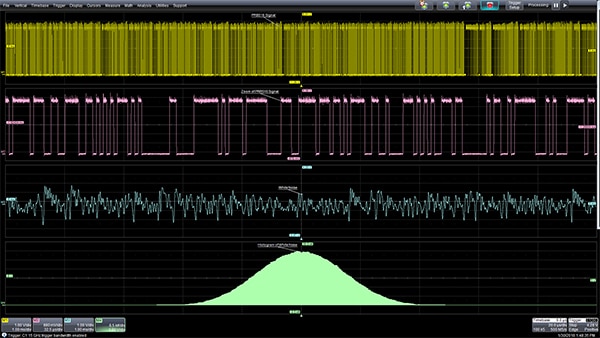

加重されたシフトレジスタ出力は差動アンプで合計されます。このアンプはLM324KDRクワッドオペレーショナルアンプの3つのセクションを使用して構築されています。上の抵抗器バンクは、sin(x)/x加重の負のコンポーネントを表します。下の抵抗器バンクは正の値を表します。出力Q3およびQ12は、sin(x)/x関数のゼロクロスポイントを表すため、接続されていません。結果のホワイトノイズ出力には、クラッシックなガウス確率密度関数(PDF)が示されます(図6)。

図6:PRBSデジタルノイズ(上の2つのトレース)とアナログホワイトノイズ出力(上から3番目のトレース)。ホワイトノイズ(下のトレース)のヒストグラムには、クラッシックなベル型の標準またはガウスPDFが示されます。(画像提供:DigiKey)

ホワイトノイズ信号は上から3番目です。以下は、予想される標準またはガウス確率分布を示すノイズのヒストグラムです。ホワイトノイズは、クロック周波数の5%(25kHz)に帯域制限されます。これは、可聴周波数テストに適しています。

まとめ

説明したように、すぐに利用可能なCMOS ICを使用して、通信およびテスト目的で疑似ランダム2進数シーケンスとアナログホワイトノイズの両方を生成できます。使用されるパーツのBOMは安価であるため、学術研究、ホビースト、コストを意識するエンジニアや技術者に最適です。

免責条項:このウェブサイト上で、さまざまな著者および/またはフォーラム参加者によって表明された意見、信念や視点は、DigiKeyの意見、信念および視点またはDigiKeyの公式な方針を必ずしも反映するものではありません。