フラッシュレスMCUの使用によるシステムコストの低減と性能の強化

DigiKeyの北米担当編集者の提供

2019-08-22

IoT(モノのインターネット)ネットワークに対して、より複雑なタスクを実行することが求められる中で、IoTエンドポイントのメモリ要件は高まりつつあります。中でも、より高度なエッジコンピューティングを実行するようになったエンドポイントでそれは顕著になっています。しかし、オンチップのマイクロコントローラフラッシュメモリは約1Mビットに制約されていますが、多くのハイエンドIoTエンドポイントではその何倍ものメモリが必要になります。

これまでは、マイクロコントローラのプログラムメモリを外部フラッシュチップで拡張することによってこの問題を解消してきました。しかし、メモリ要件が8Mビット以上になると、プログラムメモリの大部分がチップ外になってしまいます。

結果として、設計者にとっては、多くの場合オンチップフラッシュを完全に省き、代わりにフラッシュレス(ROMレスとも呼ばれる)のマイクロコントローラを外部の高速オクタルSPI eXecute-in-place(XiP)フラッシュチップと結合して使用するのがより良い方法とも考えられます。こうすることで、マイクロコントローラのコストが大幅に減り、スケーラビリティの向上により将来も通用する設計が保証されます。超高速なオクタルメモリインターフェースの登場によって、メモリアクセス時間についてのあらゆる懸念が払拭されます。

この記事では、ROMレスマイクロコントローラと外部メモリについて検討し、それらが大量のプログラムメモリを必要とするIoTエンドポイントや組み込みシステムの有望なオプションとして進化している状況を解説します。さらに、NXP SemiconductorsのROMレスマイクロコントローラやAdesto TechnologiesのオクタルSPI XiPフラッシュチップを活用して、フラッシュレスの概念を応用する方法をご紹介します。

IoTエッジでのメモリ拡張

性能的に低~中程度の大半のIoTエンドポイントは、マイクロコントローラを使用してエンドポイントを管理し、ファームウェアをオンチップフラッシュに保存しています。ファームウェアは、追加のアプリケーションコード、ワイヤレスIP通信スタック、拡張セキュリティコードが増えるにつれて増加します。コードの増加は開発の途上で生じ、フィールド更新によっても起こり得ます。

現在このようなIoTエンドポイントの中には、より多くの演算機能の実行が求められるものもあります。未加工データまたは一部処理済みのセンサデータをネットワークで中央コンピュータに送信して処理する代わりに、これらのIoTエンドポイントは、センサフュージョンアルゴリズム、データ補間、パターンまたは画像認識、一段と複雑化する人工知能(AI)コンピューティングなどのより複雑なタスクを実行します。

これにより、中央のコンピュータは未加工センサデータを丸ごとではなく、IoTノードのローカルの処理結果のみを受信するので、結果的にワイヤレスネットワーク上のトラフィックを減少させることができます。IoTエンドポイントではRFトランスミッタが最も顕著な電力消費の要因になり得るので、多くの場合エッジコンピューティングは電池駆動によるエンドポイントの電池寿命を延ばすことになります。

フィールドでの更新が必要なシステムには、さらに別のメモリの問題があります。従来のシステムでは、そのような更新を処理できるように、想定されるプログラムメモリ容量の少なくとも2倍の容量が必要です。これは、既存のプログラムメモリと、ある一定サイズのオーバーザエア(OTA)更新の両方を処理するためです。システムによっては、工場出荷時の読み取り専用ファームウェアイメージに追加メモリが割り当てられることで、推定プログラムメモリ容量の3倍が必要になる場合もあります。ハッキング検出やファームウェアイメージの破損など特定のシステム障害が発生した場合に、システムは出荷時の初期ファームウェアイメージをロードしてシステムを回復できます。

一部のアプリケーションでは、このメモリ拡張が1Mビットの組み込みフラッシュの限界をすぐに超える可能性があり、外部メモリ拡張が必要になります。従来は、外部パラレルフラッシュメモリチップを追加することでこの問題を解決してきました。しかし、この場合は約36本の外部ピンをマイクロコントローラで使用するという難点があります。その必要がなければ、これらのピンはアプリケーションI/Oに使用できるはずのピンでもあります。これにより、プリント基板のスペースも無駄になり、基板から電磁妨害(EMI)が生じる可能性も高まります。

SPIプログラムメモリ拡張

パラレルバスを使用する以外に、プログラムメモリの拡張にはシリアルペリフェラルインターフェース(SPI)を使用することもできます。従来のSPIは半二重シングルビット伝送に1本のデータラインのみを使用しましたが、長年にわたってデュアルおよびクアッドデータラインをサポートするように性能が強化され、それに応じてデータスループットも向上しました。このスループットは、大容量外部SPIフラッシュチップへのインターフェース接続が実用的なレベルになるまで高まっています。

プログラムメモリアプリケーションについては、従来のデュアルまたはクワッドSPIではシャドウフラッシュ構成を使用しますが、この場合、外部フラッシュデータメモリが、プログラムメモリ空間にマッピングされる組み込みSRAM(スタティックランダムアクセスメモリ)にコピーされます。この仕組みには、プログラムメモリを簡単に拡張できるとともに、高速SRAMからの実行により処理速度を向上できるという長所がありますが、一方で重大な欠点もあります。内部SRAMの容量は限られているので、フラッシュメモリが必要に応じて内部SRAMにスワップされる際、メモリへのアクセスはページモードで行われます。このネックはオンチップのSRAMを増やせば低減できますが、SRAMは半導体部品の中でも非常に高価な部品なので、マイクロコントローラのコストが著しく増えるというデメリットがあります。

SPIが進化して最近登場したのがXiPです。SPI XiPにより、マイクロコントローラのCPUがファームウェアコードを外部のSPIフラッシュから直接実行できます。SPI XiPインターフェースにキャッシュを追加することで、プログラムの実行速度が大幅に向上します。

SPI XiPの普及により、最近ではインターフェースが8本のデータラインで拡張されるようになりました。このオクタルSPI XiPインターフェースによりスループットが高まり、オンチップフラッシュメモリからの実行よりもはるかに高速なレベルに達し、その速さは100Mビット/秒を凌駕します。

SPIメモリの革命

これにより、30年前に先祖返りするような皮肉な進化が生まれました。1Mビットのオンチップフラッシュと32メガビットの外部フラッシュプログラムメモリがオクタルSPI XiPインターフェースでアクセスされるシステムを想像してください。オンチップのプログラムメモリは極めて小さいので、そのオンチップのマイクロコントローラフラッシュを省いても、コスト効率の良いシステムが成立するのか、という疑問が湧いてきます。

フラッシュマイクロコントローラを備えたミッドレンジシステムは、外部フラッシュチップを備えたフラッシュレスマイクロコントローラをともなうシステムと比べると、常にコスト効率が良いと、以前から考えられてきました。それが変わり始めたのは、ごく最近です。

オンチップフラッシュメモリを省くと、当然ながらマイクロコントローラのコストは下がります。しかし、詳しく調査してみると、フラッシュが必要でなくなる場合、フラッシュにのみ使用されるプロセステクノロジ機能も同様に必要がなくなることが分かりました。これにより製造プロセスのコストが下がり、マイクロコントローラのコストが大幅に削減されます。その結果、約30年前に「ROMレス」マイクロコントローラと呼ばれていたものが再び登場したのです。現在はそれをフラッシュレスと呼んでいます。

フラッシュレスマイクロコントローラの(再)登場

フラッシュメモリの速度を最大限に活用できる高性能マイクロコントローラには、NXP SemiconductorsのフラッシュレスMIMXRT1052DVL6B(RT1052)があります。RT1052はNXPのi.MX RT1050プロセッサファミリに属し、32KBの命令キャッシュと32KBのデータキャッシュを備えた600MHzのArm® Cortex®-M7をベースにしています。フラッシュを省き、内部フラッシュメモリに制約されない高速CMOSプロセス技術を使用することで、600MHzのクロック速度が実現されています。RT1052は大容量のSRAM(512KB)を備えており、プログラムまたはデータメモリ用にパーティションを設けることができます。

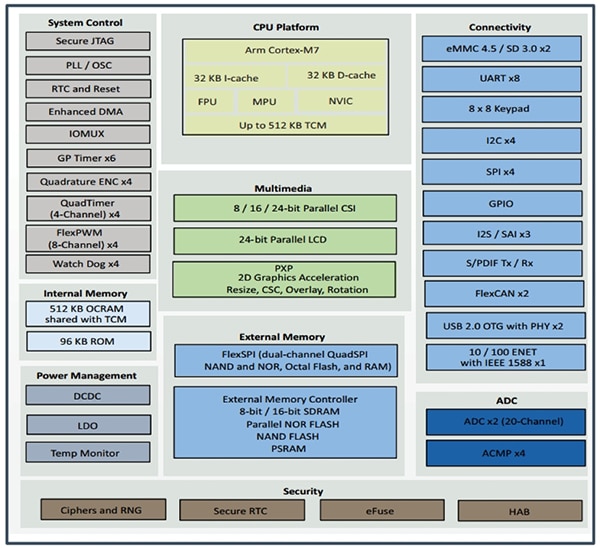

また、LCDインターフェース、デジタルカメラセンサ用インターフェース(CSI)、ハイエンドのカメラをサポートするピクセル処理パイプライン(PXP)、デジタルオーディオ用SPDIFインターフェース、2つのUSB OTGインターフェース、2つのeMMC/SDフラッシュカードインターフェース、2つの20チャネルA/Dコンバータ(ADC)、暗号化モジュールなど、ハイエンドの各種周辺モジュールも備えています。周辺モジュールの一覧は、ブロック図をご覧ください(図1)。

図1:NXP RT1052には、SPI XiPシリアルインターフェースやデータ暗号化のサポートなど、さまざまなハイエンド周辺モジュールが搭載されています。(画像提供:NXP)

図1:NXP RT1052には、SPI XiPシリアルインターフェースやデータ暗号化のサポートなど、さまざまなハイエンド周辺モジュールが搭載されています。(画像提供:NXP)

もう1つのオプションとなるのが、NXP MIMXRT1051DVL6B(RT1051)です。LCDインターフェース、CSI、およびPXPを除き、RT1052と同じ機能をすべて備えています。

RT1052にはFlexSPIインターフェースがあり、デュアル、クワッド、またはオクタルSPI XiPフラッシュインターフェースを使用してコードを実行できます。ファームウェアのセキュリティ強化のために、このマイクロコントローラではSPI XiPを通じて暗号化されたプログラムメモリがサポートされます。その代表的な例がAdesto TechnologiesのATXP032-CCUE-Tです。

最新のXiPフラッシュ機能

AdestoのATXP032-CCUE-Tは32Mビットオクタルフラッシュチップで、毎秒最大266メガバイト(Mバイト)のデータ転送を、オクタルデュアル転送レート(DTR)モードでサポートします。これは、オンチップのマイクロコントローラフラッシュメモリに比べてはるかに高速です。このデバイスには1.8V単一電源が必要で、35μAのオクタルモードスタンバイ電流(標準)をともないます。また133MHzの最大SPIクロック速度をサポートします。

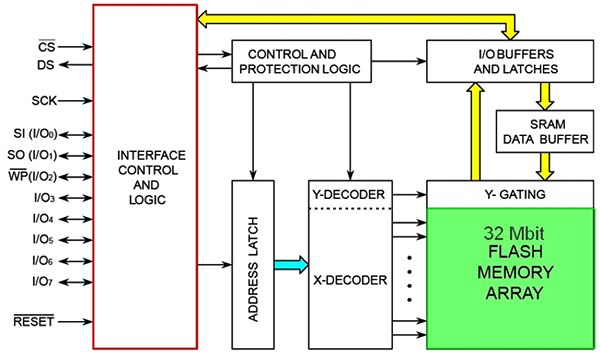

図2:AdestoのATXP032-CCUE-Tフラッシュメモリは、オクタルSPI、I/O0~I/O7を使用して、マイクロコントローラにインターフェース接続します。書き込みSRAMデータバッファによりフラッシュへの書き込み動作の性能が向上しています。(画像提供:Adesto Technologies)

図2:AdestoのATXP032-CCUE-Tフラッシュメモリは、オクタルSPI、I/O0~I/O7を使用して、マイクロコントローラにインターフェース接続します。書き込みSRAMデータバッファによりフラッシュへの書き込み動作の性能が向上しています。(画像提供:Adesto Technologies)

アクティブフラッシュ読み取り中のATXP32の消費電流は142μA/MHz、プラス1mAのオーバーヘッド(標準)です。オクタルモードでの133MHzという最高SPIクロック速度では、わずか19.9mAしか消費しません。

さらにATXP032-CCUE-Tは、標準SPIモード0および3、そしてクワッドSPIモードをサポートします。256バイトのセキュリティレジスタには、工場出荷時にプログラムされた128バイトの一意識別子と、128バイトのワンタイムプログラマブル(OTP)メモリがあり、OTPを使用してEthernetメディアアクセス制御(MAC)アドレスやセキュリティキーなどのデバイス情報を格納できます。

注目すべきはATXP032-CCUE-Tのメモリ配列です。ATXP032-CCUE-Tでは、各8Mビットの4つのバンクができるように、パーティションが設けられています。内部ロジックは、ホストマイクロコントローラが1つのバンクからコードを実行し別のバンクをプログラミングするか消去できるように構成されています。ホストマイクロコントローラに対して透過的に動作するため、特別な構成に設定する必要はありません。

また、ATXP032-CCUE-Tには3つのステータスレジスタと制御レジスタもあり、デバイスの動作パラメータを低電力モードなどに構成し、DTRモードを有効または無効にして、標準、クワッド、またはオクタルSPIモードを設定できます(デフォルトは標準SPI)。ステータスレジスタからの読み取りによって、プログラムまたは消去操作のステータス、低電力ステータス、およびメモリのいずれかが書き込み保護されているかどうかを示すことができます。

フラッシュレスマイクロコントローラと外部XiPの組み合わせ

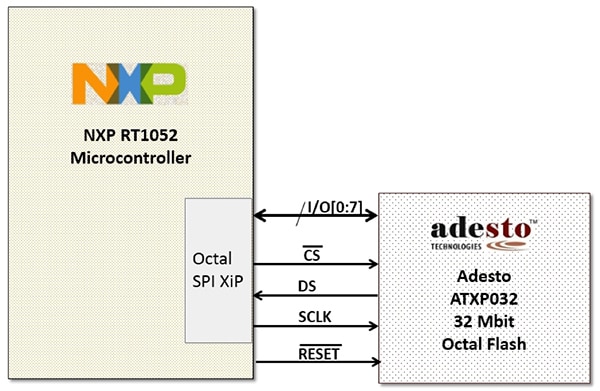

RT1052とATXP032-CCUE-Tの組み合わせは簡単です(図3)。電源投入時に、RT1052は96KBのオンチップブートROMからコード実行を開始します。このブートROMは14本のブートモード構成ピンの状態を読み取ります。これらのピンは、多くのRT1052外部メモリインターフェースの中からプログラムメモリに使用するインターフェースを選択します。オプションとして、外部eMMCカード、マイクロSDカード、従来の外部パラレルインターフェース、またはSPI XiP(この場合、AdestoのATXP032-CCUE-T)があります。

図3:NXP RT1052フラッシュレスマイクロコントローラはオクタルSPI XiPインターフェースを備えており、AdestoのATXP032-CCUE-Tと簡単にインターフェース接続できます。オクタルSPI XiPインターフェースはArmコアに対して透過的に動作します。(画像提供:DigiKey)

図3:NXP RT1052フラッシュレスマイクロコントローラはオクタルSPI XiPインターフェースを備えており、AdestoのATXP032-CCUE-Tと簡単にインターフェース接続できます。オクタルSPI XiPインターフェースはArmコアに対して透過的に動作します。(画像提供:DigiKey)

各種のRT1052ブートオプションには、USB OTGまたはUARTからコードをダウンロードして、SRAMから実行する機能も含まれています。これらのブートモードオプションは、ブートモード構成ピンを使わずにRT1052内部にある内蔵ヒューズを飛ばすことによって、製造時に設定することもできます。RT1052のブートROMによって、オクタルSPI XiPインターフェースがプログラムメモリ実行用に有効になると、プログラムが即座に実行されます。続いて、ArmコアがAdestoのATXP032-CCUE-Tからファームウェアを実行します。その方法は外部パラレルフラッシュデバイスまたは内部フラッシュからの実行方法と同じです。

高速なデータ転送を伴うため、オクタルシリアルフラッシュはプリント基板上でマイクロコントローラのオクタルSPI XiPポートになるべく近い箇所に配置する必要があります。干渉を減らすため、どのPCトレースも120mmより短くしてください。クロック信号は、干渉防止のため、他の信号からプリント基板トレース幅の少なくとも3倍の距離は離す必要があります。また、スキュー防止のため、I/O [0:7]双方向データ信号は、すべて相互間隔10mm以内にする必要があります。

まとめ

エッジコンピューティングを志向するトレンドや、OTA更新の必要性、さらには関連しているメモリのスケーラビリティニーズによって、IoTエンドポイントのメモリ要件は高まっています。これらのエンドポイントデバイスの設計者は、いつの日か、フラッシュレスのマイクロコントローラを活用することが検討に値する選択肢であることに気付くでしょう。

本記事で述べたように、フラッシュレスマイクロコントローラ、高速インターフェース、およびオクタルSPI XiPフラッシュチップの進歩により、開発者は、従来のフラッシュに基づいたマイクロコントローラのアプローチを使用する代わりに、高性能でコスト効率の良いIoTエンドポイントや組み込みシステムを構築できます。

免責条項:このウェブサイト上で、さまざまな著者および/またはフォーラム参加者によって表明された意見、信念や視点は、DigiKeyの意見、信念および視点またはDigiKeyの公式な方針を必ずしも反映するものではありません。