超低電力HMPシングルプロセッサでリアルタイム処理とアプリケーション処理の両ワークロードに対応

DigiKeyの北米担当編集者の提供

2019-08-06

消費者は、パーソナル電子機器やモバイル機器がより高速なレスポンスと高度な機能の両方を発揮し、しかも電池寿命が長持ちすることに期待します。一方で開発者は、多くのアプリケーションでリアルタイムのレスポンスと高い性能が要求されると、これらの相反するニーズを満たすには別々のプロセッサが必要であるという発想から逃れられませんでした。そのため、より多くのコスト、電力、スペースが必要な上に、ハードウェアレイアウトとソフトウェアの両方の複雑性にも直面しました。

そこでより良い解決方法として考えられるのは、必要なハードウェアをシングルチップに統合することです。つまり異種マルチコア処理(HMP)デバイスの採用です。異なるタイプの複数のコアを含むこのようなプロセッサには、性能の最適化、消費電力の低減、システムセキュリティと信頼性の向上という利点があります。

この記事では、NXP Semiconductorsの異種マルチコアプロセッサを使用することで、低消費電力と設計の簡素化への要求に応えながら、こういったさまざまなワークロードに対する需要を満たす方法について説明します。

変化する要求

センサ技術とデータ処理アルゴリズムの進歩にともない、リアルタイムのデータ収集と演算集約的なアルゴリズムの実行という相反する要求に応える大きな可能性が生まれました。これまで、これらのワークロードは一般的に別個のシステムとして分けて扱われていました。

ネットワーク階層の最下位のレベルでは、Arm® Cortex®-M4コアベースのプロセッサなどの組み込みプロセッサがデータを収集し、最適化されたコードをリアルタイムオペレーティングシステム(RTOS)またはベアメタルシステムで実行します。階層の上位レベルでは、Arm Cortex-A7コアベースのプロセッサなどの高性能アプリケーションプロセッサがデータ解析アルゴリズムを実行し、LinuxやAndroidなどの一般的なオペレーティングシステムでアプリケーションコードを実行します。

エッジコンピューティングシステムの高まりにより、アプリケーションコードの実行がデータソースに接近してきました。実際に、複雑化する解析アルゴリズムからより素早いレスポンスを求める傾向によって、末端の機器本体がアプリケーション処理の要求を引き受けるようになりました。消費者は、AI(人工知能)を駆使した手法などの高度な解析機能がIoT(モノのインターネット)センサ、ウェアラブル端末、他の低電力製品などの機器に組み込まれることをより強く望んでいます。

異種マルチコア処理(HMP)の役割

組み込みプロセッサとアプリケーションプロセッサのコアを組み合わせたHMPデバイスが登場し、多くのアプリケーションでさまざまなワークロードをより効率的に扱えるようになりました。HMPプロセッサは各種のコアを統合し、それぞれのコアがターゲット製品のワークロードと結びついたそれぞれの要件を満たすように最適化されています。NXPのi.MX 7ULP(超低電力)プロセッサファミリにより、開発者はHMPアーキテクチャの能力を活用することで、次世代ULP製品に対して高い性能と長時間の電池寿命を妥協なしに求める消費者の要望を満たすことができます。

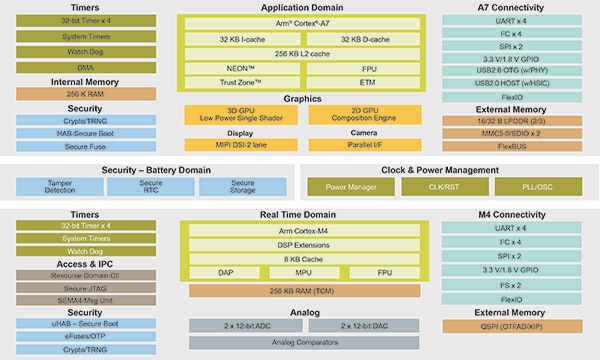

i.MX 7ULPプロセッサには、民生用(MCIMX7U5DVP07SC)と産業用(MCIMX7U5CVP06SC)の両バージョンがあり、それらの異種コアをグラフィックス処理ユニット、セキュリティアクセラレータ、メモリコントローラ、フルセットの周辺機器インターフェースと統合しています(図1)。

図1:NXPのi.MX 7ULPアプリケーションプロセッサファミリは、モジュールと周辺機器が充実しているとともに、リアルタイム処理用のArm Cortex-M4コアとアプリケーション処理用のArm Cortex-A7コアを組み合わせています。また個別のパワードメインを使用して、電力と性能の最適化を図っています。(画像提供:NXP)

図1:NXPのi.MX 7ULPアプリケーションプロセッサファミリは、モジュールと周辺機器が充実しているとともに、リアルタイム処理用のArm Cortex-M4コアとアプリケーション処理用のArm Cortex-A7コアを組み合わせています。また個別のパワードメインを使用して、電力と性能の最適化を図っています。(画像提供:NXP)

電力に制約があるポータブル機器の設計に特化して開発されたNXP i.MX 7ULPファミリは、それぞれ個別のパワードメインから給電されるArm Cortex-A7コアとCortex-M4コアの組み合わせにより、新たな要求に対応します。さらに、異なるパワーアイランドの使用により、個別のモジュールを(もしそれが必要なければ)選択的にパワーダウンできます。以下で述べるように、i.MX 7ULPデバイスに統合された高度な電源管理機能により、これらのパワードメインとパワーアイランドを使用して、性能と消費電力をアプリケーションに応じて最適に調整できます。

電力の最適化

NXPはi.MX 7ULPファミリの設計時に、チップ設計レベルを手始めにアーキテクチャ全体にわたり電力と性能の最適化機能を組み入れました。

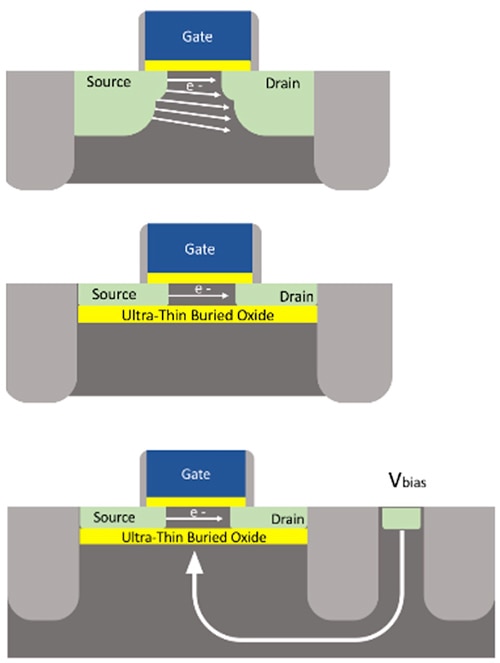

最も基礎的なレベルで、i.MX 7ULPファミリはリーク電流を削減する製造手法と寄生を低減するトランジスタジオメトリを組み合わせており、これによって動的消費電力を低減しています。従来のトランジスタ構造とは異なり(図2、上)、i.MX 7ULPデバイスは極薄の埋め込み酸化膜を用いて製造されており(図2、中央)、ソースからドレインへの電子の流れを減らすことで、リーク電流を減らします。さらなる改良により、フォーワード基板バイアス(FBB)またはリバース基板バイアス(RBB)の追加が可能になっています(図2、下)。

図2:従来のトランジスタでは、電子がソースからドレインへ流れる際に顕著なリークが見られる場合がありますが(上)、NXP i.MX 7ULPファミリは電子の流れを妨げる極薄埋め込み酸化膜で製造されており(中央)、その構造はフォワード基板バイアス(FBB)またはリバース基板バイアス(RBB)によって電子の流れを速めたり遅くしたりします(下)。(画像提供:NXP)

図2:従来のトランジスタでは、電子がソースからドレインへ流れる際に顕著なリークが見られる場合がありますが(上)、NXP i.MX 7ULPファミリは電子の流れを妨げる極薄埋め込み酸化膜で製造されており(中央)、その構造はフォワード基板バイアス(FBB)またはリバース基板バイアス(RBB)によって電子の流れを速めたり遅くしたりします(下)。(画像提供:NXP)

エネルギー効率が最優先の場合は、RBBを使用して電子の流れを減らし、性能の低下と引き換えにリーク電流とデバイス全体の消費電力をさらに低減できます。逆に、FBBを使用して電子の流れを高めると、リーク電流の増加により消費電力が増えるのと引き換えに、性能をアップさせることができます。

チップ設計レベルでは、i.MX 7ULPファミリは複数の手法、たとえば動的周波数スケーリング(DFS)および動的電圧スケーリング(DVS)、ソフトウェアベースのクロックゲーティング、ソフトウェアベースのパワーゲーティングなどを組み入れています。さまざまな周辺機器の消費電力の削減に加えて、これらの機能を使用することで、内部メモリのブロックを選択的にシャットダウンしたり、メモリを異なる省電力モードにすることができます。

アーキテクチャのレベルでは、Cortex-A7サブシステムとCortex-M4サブシステムの個別のパワードメイン(前述を参照)など複数のパワードメインを使用することで、電力と性能の調整機能がさらに拡張されています。

プロセッサコアのパワードメインごとに、FBBおよびRBBドライバ、専用の低ドロップアウト(LDO)レギュレータ、さらに指定のしきい値以上または以下の電源エクスカーションを通知するように設計された高レベル検出器(HVD)と低レベル検出器(LVD)モニタが含まれています。個別のパワーオンリセット(PoR)モニタは、常時オンのパワードメインの電圧レベルを追跡します。

個別のコアパワードメインとともに、個々のパワードメインも常時オンのハードウェアなどのシステム機能を制御する一方、電池でサポートされるドメインは、リアルタイムクロックやセキュアな不揮発性ストレージモジュールなど重要な機能への電力を管理します。コアパワードメインと同様に、これらの専門化されたパワードメインはいずれも、省電力専門の機能の包括的なセット(1つの記事では紹介し切れないほど多数の機能を含む)をサポートします。

その一例として、常時オン機能のパワードメインには低リークウェイクアップユニット(LLWU)モジュールが含まれており、複数の外部ピンまたは内部モジュールを特別な低リーク電力モードのウェイクアップソースとして使用できます(以下の説明を参照)。

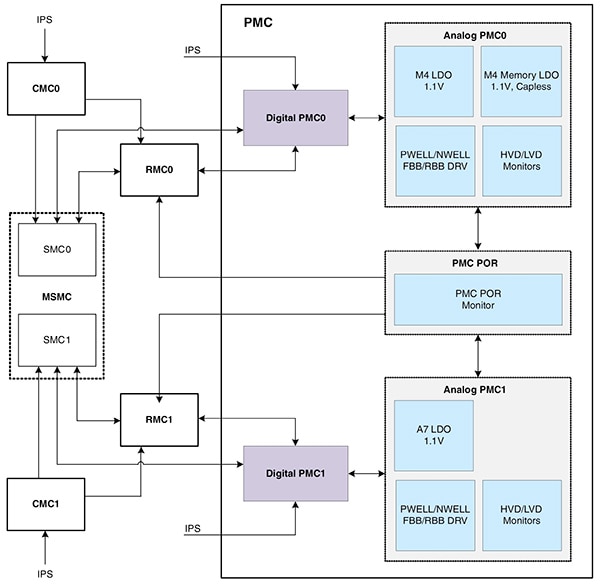

これらのアーキテクチャ機能は、デバイスの統合電源管理コントローラ(PMC)で互いに結びついており、このPMCはこれらの個別パワードメインとデバイスのパワーアイランドに対応します(図3)。

図3:NXP i.MX 7ULPファミリは高度な制御機能を統合しているため、パワードメインとパワーアイランドをプログラムで構成して、変化するアプリケーションの要求を満たすように電力と性能を調整できます。(画像提供:NXP)

図3:NXP i.MX 7ULPファミリは高度な制御機能を統合しているため、パワードメインとパワーアイランドをプログラムで構成して、変化するアプリケーションの要求を満たすように電力と性能を調整できます。(画像提供:NXP)

この手法では、電力モードの移行を開始するにあたり、通常のインテリジェントペリフェラルサブシステム(IPS)バスを経由して3つの密結合モジュールから構成される制御複合システムにコマンドを送信します。

- コアモードコントローラ(CMC):複数のコア機能をサポートします。

- マルチコアシステムモードコントローラ(MSMC):Cortex-M4パワードメイン用のシステムモードコントローラ0(SMC0)とCortex-A7パワードメイン用のSMC1から構成され、異なる電力モード間のシーケンシングを処理し、電力モードの移行開始に使用されるイベントを監視し、電力の最適化に関連した電力、クロック、メモリ機能の基本制御を行います。

- リセットモードコントローラ(RMC):チップのリセット機能を処理します。

電力と性能の調整

i.MX 7ULPファミリは、そのすべての電源管理機能について、馴染みのあるプログラミングモデルを提供します。他の高度なプロセッサと同様に、i.MX 7ULPデバイスは一連のプログラム可能な低電力モードによって各種の低電力な動作状態を実現します。実際、i.MX 7ULPプロセッサコアは、いくつかのソフトウェア制御による低電力モードをサポートしているため、必要な機能に応じて消費電力を可能な最低限レベルまで削減できます。

これらのさまざまな低電力モードを使用して、一方または両方のコアとそのサブシステムを通常のRUNモード、WAITモード、STOPモードの各種バリエーションに設定できます。

通常のRUNモードと高速なHSRUNモードでは高性能な動作が可能になり、アプリケーションの計算集約的な部分をサポートします。HSRUNモードでは、コアのサブシステムがその最高周波数で動作します。アプリケーションがより低い性能も許容できる場合は、コアを超低電力実行(VLPR)モードに設定し、最大周波数48MHzでの動作を可能にすることで、消費電力を低減できます。

通常のWAITモードでは、周辺機器は完全に動作しますが、コアはクロックゲーティングされ静的な状態で待機し、WFI(Wait-For-Interrupt)信号を受信すると起動できる態勢にあります。このモードでは、コアをWAIT状態から解放する割り込みを発行する前に、自律的な周辺機器の動作でバッファを充填させるか、あるいはダイレクトメモリアクセス(DMA)トランザクションを使用してシステムメモリを充填させることができます。超低電力待機(VLPW)モードは、低減された周波数で周辺機器の動作を継続させますが、コアクロックをゲーティングします。

ウェアラブル端末やポータブル機器などのアプリケーションでは、システムは非アクティブな状態が長く続く場合があり、アクティビティのバーストによる周期的な中断が考えられます。このような場合は、省電力機能が電池寿命の面で重要になります。アプリケーションがコアのさらに遅いウェイクアップ時間を許容できれば、デバイスをRUN、WAIT、または超低電力のバリエーションよりもさらに深いスリープ状態にする機能が、特に効果的な選択肢になります。この手法をサポートするために、それぞれのi.MX 7ULPコアサブシステムをより深いスリープ状態にして、ウェイクアップ時間が異なる長さになるように設定できます。

- STOP状態では、周辺機器によっては非同期的に動作できるものもありますが、コアは静的な状態のままになり、ウェイクアップ時間はCortex-A7で7μs(マイクロ秒)、Cortex-M4で7μsとなります。

- 超低電力停止(VLPS)モードでは、周辺機器の動作はさらに制限されますが、コアは静的状態のままになり、ウェイクアップ時間は21.5μs(Cortex-A7)または9μs(Cortex-M4)です。

さらに厳格な電力要件のアプリケーションでは、各コアを以下の特別な低リークモードに設定し、より多くの機器のサブシステムをシャットダウンできます。

- 低リーク停止(LLS):コア、バス、周辺機器をクロックゲーティングします。コアはWFI状態のままで、ウェイクアップ時間は40μs(Cortex-A7)または58μs(Cortex-M4)です。

- 超低リーク停止(VLLS):コアのパワードメイン全体をクロックゲーティングします。これによりウェイクアップ時間はさらに延びて、60μs(Cortex-A7)または375μs(Cortex-M4)などになります。

より大幅な省電力が求められる場合でも、RBBをVLPSやLLSなどの電力モードで使用し、それに伴った性能の低下と引き換えにウェイクアップ時間を約2~4μs延ばすことができます。

対照的に、演算集約型のワークロードへの対処が必要な場合は、特別な高速実行(HSRUN)モードでコアを実行できます。HSRUNモードでは、Cortex-A7コアを通常の動作周波数500MHzから720MHzで動作するオーバードライブモードにシフトします。

このような細かい制御によって、基本的な機能を低下させずに極端な電力要件を満たすようにi.MX 7ULPを構成することもできます。たとえば、アプリケーションが最小限の消費電力を必要としながら、Cortex-M4コアのリアルタイム機能が要求される場合や、特定のCortex-A7サブシステム周辺機器やメモリの使用が必要な場合が考えられます。このような場合は、Cortex-A7サブシステムをSTOPまたはVLPS状態にして、Cortex-M4のコアがリアルタイム動作を実行する際にCortex-M4からCortex-A7サブシステムのメモリまたは周辺機器にアクセスできます。さらなる省電力が求められる場合は、Cortex-M4クロックを使用してCortex-A7の周辺機器を駆動できます。

シンプルなシステム実装

i.MX 7ULPで低電力システムを実装するために、利用できるソフトウェアプログラム可能な電力モードと構成の中から選択して、電力と性能の要件に一致させることができます。ハードウェア側では、システム設計はさらにシンプルになります。

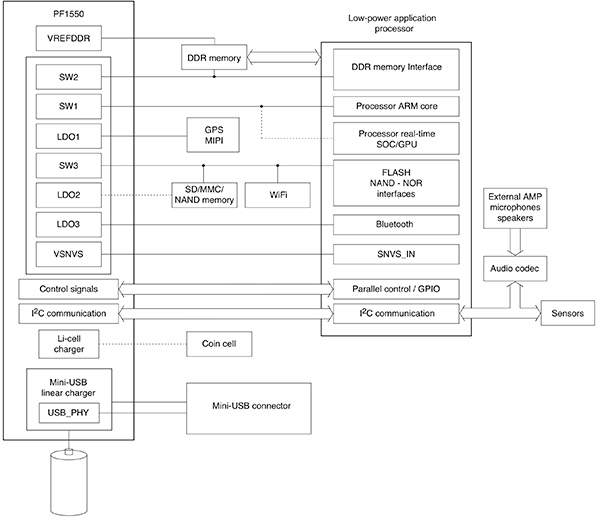

標準アプリケーションの場合は、単にi.MX 7ULPプロセッサとコンパニオンのNXP MC32PF1550A3EPR2電源管理IC(PMIC)を組み合わせて、限られた電力バジェットを犠牲にせずに、さまざまなワークロードを処理できる設計を完成できます(図4)。

図4:NXP MC32PF1550A3EPR2電源管理ICは、NXP i.MX 7ULPプロセッサに必要な電源の完全なセットを提供し、ハードウェア設計をこれら2つのデバイスと少数の受動部品の簡単な組み合わせに簡素化します。(画像提供:NXP)

図4:NXP MC32PF1550A3EPR2電源管理ICは、NXP i.MX 7ULPプロセッサに必要な電源の完全なセットを提供し、ハードウェア設計をこれら2つのデバイスと少数の受動部品の簡単な組み合わせに簡素化します。(画像提供:NXP)

i.MX 7ULPファミリに代表されるNXPプロセッサの電源要件を特別にサポートするように設計されたMC32PF1550A3EPR2は、3つのスイッチドモード降圧レギュレータ(SW1、SW2、SW3)、3つのLDOレギュレータ(LDO1、LDO2、LDO3)、メモリ基準電圧源、完全なシングルセルリチウムバッテリチャージャ、デバイス構成用のワンタイムプログラマブル(OTP)メモリを統合します。

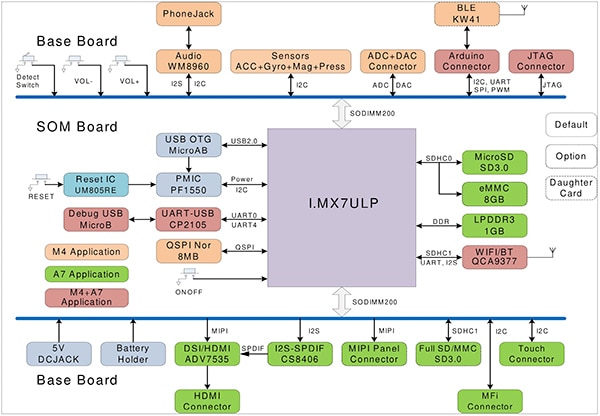

NXPは同社のMCIMX7ULP-EVK評価キットで、MC32PF1550A3EPR2 PMICとi.MX 7ULPデバイスの組み合わせに必要なのは簡潔なハードウェアインターフェースであることを実証しています。このキット内容には、i.MX 7ULPプロセッサとMC32PF1550A3EPR2 PMICを含んでいるシステムオンモジュール(SOM)ボードとともに、複数センサ、ワイヤレス機能、オーディオコーデック、SDコネクタ、およびJTAGやArduinoなど複数のコネクタを搭載したベースボードが含まれています(図5)。

図5:MCIMX7ULP-EVK評価キットは、i.MX 7ULPプロセッサとMC32PF1550A3EPR2 PMICを含んでいるシステムオンモジュールボードと、センサ、コネクタ、そしてi.MX 7ULPデバイスでの迅速なソフトウェア開発に必要な他のコンポーネントを含んでいるベースボードを組み合わせています。(画像提供:NXP)

図5:MCIMX7ULP-EVK評価キットは、i.MX 7ULPプロセッサとMC32PF1550A3EPR2 PMICを含んでいるシステムオンモジュールボードと、センサ、コネクタ、そしてi.MX 7ULPデバイスでの迅速なソフトウェア開発に必要な他のコンポーネントを含んでいるベースボードを組み合わせています。(画像提供:NXP)

評価キットにはそのまま使用できる機能が含まれる一方で、NXPはリアルタイムコードにFreeRTOSを使用しアプリケーションコードにLinuxまたはAndroidを使用するカスタムソフトウェアを対象に、ダウンロード可能な設計ファイル、ツール、基板サポートパッケージも提供します。

結論

より高度な機能と長時間の電池寿命の両方が求められるモバイル製品では、これまで開発者は電力と性能の間で何らかの妥協点を探る必要がありました。また、IoT機器、ウェアラブル端末や他のポータブル製品で増加しているセンサからのタイムリーなデータがさらに求められていることで、リアルタイム機能とアプリケーションレベルの性能の間でさらに妥協点を探る必要が生じています。

本記事で述べたように、これらの状況に対して、NXPのi.MX 7ULPプロセッサファミリで使用されているようなHMPアーキテクチャを活用することにより、各種の機能を犠牲にせずに、超低電力の厳しい要件を満たすことができます。

免責条項:このウェブサイト上で、さまざまな著者および/またはフォーラム参加者によって表明された意見、信念や視点は、DigiKeyの意見、信念および視点またはDigiKeyの公式な方針を必ずしも反映するものではありません。