コプロセッサアーキテクチャ:ラピッドプロトタイピングのための組み込みシステムアーキテクチャ

2021-07-06

編集者注 - コプロセッサアーキテクチャは、そのデジタル処理性能とスループットでよく知られていますが、組み込みシステムの設計者に対しては、開発コストと市場投入までの時間の両方を改善するプロジェクト管理戦略を実行する機会をもたらします。この記事では、特にディスクリートのマイクロコントローラ(MCU)とディスクリートのフィールドプログラマブルゲートアレイ(FPGA)の組み合わせに焦点を当て、このアーキテクチャが効率的で反復的な設計プロセスにいかに適しているかを紹介します。研究資料、経験的な知見、ケーススタディを活用して、このアーキテクチャの利点を探り、例示的なアプリケーションを示します。組み込みシステムの設計者はこの記事を読むことで、汎用性の高いこのハードウェアアーキテクチャをいつ、どのように実装すればよいのかを、より深く理解することができるでしょう。

はじめに

組み込みシステムの設計者は、設計上の制約、期待される性能、スケジュールや予算などの問題に直面します。「フェイルファスト」、「アジャイル」、「フューチャープルーフ」、「ディスラプティブ」など、現代のプロジェクト管理における流行語やフレーズの矛盾は、その役割の不安定さをさらに際立たせています。このような期待に応えようとするための離れ業的な作業は大変なものですが、それでもこれらの期待は市場で語られ、また強化され続けています。必要なのは、進化的な反復プロセスの導入を可能にする設計手法であり、多くの組み込みシステムと同様に、それはハードウェアアーキテクチャから始まります。

コプロセッサアーキテクチャは、マイクロコントローラユニット(MCU)とフィールドプログラマブルゲートアレイ(FPGA)という両技術の長所を組み合わせたハードウェアアーキテクチャとして知られており、組み込み機器の設計者に対し、最も厳しい要件も満たすことができるプロセスを提供することができ、しかも、既知の課題と未知の課題の両方に対応するために必要な柔軟性を備えています。繰り返し適応できるハードウェアを提供することで、設計者は進歩を実現し、重要なマイルストーンを達成し、ラピッドプロトタイピングのプロセスを最大限に活用することができます。

このプロセスの中には、プロジェクトの重要なマイルストーンがあり、それぞれのマイルストーンには、開発作業に付加する独自の価値があります。この記事全体を通して、それらを以下の用語で表現します。「マイクロコントローラによるデジタル信号処理」、「マイクロコントローラによるシステム管理」、「製品展開」という3つのマイルストーンです。

この記事の結論として、柔軟なハードウェアアーキテクチャは、より厳格なアプローチよりも、現代の組み込みシステム設計に適していることが示されるでしょう。さらに、このアプローチによって、プロジェクトのコストと市場投入までの時間を両方とも改善することができます。議論、提供された例、ケーススタディを用いて、この主張を裏付けます。このアーキテクチャが提供する設計上の柔軟性の中で、各マイルストーンの価値を観察することにより、適応性のあるハードウェアアーキテクチャが、組み込みシステムの設計を前進させる強力な原動力となることが明らかになります。

コプロセッサアーキテクチャの強みを探る:設計の柔軟性と高性能処理の両立

FPGA設計の一般的な用途は、高速のA/Dコンバータ(ADC)と直接インターフェース接続することです。信号はデジタル化されてFPGAに読み込まれ、この信号にいくつかのデジタルシグナルプロセッサ(DSP)のアルゴリズムが適用されます。そして最後に、その結果に基づいてFPGAが意思決定を行います。

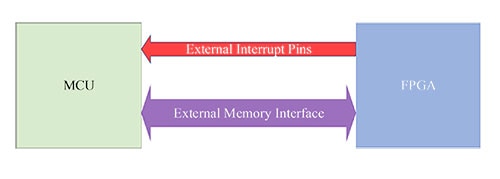

この記事では、このようなアプリケーションを例に挙げて説明します。さらに、図1は一般的なコプロセッサアーキテクチャを示しており、MCUとFPGAはMCUの外部メモリインターフェースを介して接続されています。FPGAは、あたかも外部のSRAM(スタティックランダムアクセスメモリ)のように扱われます。信号は、FPGAからMCUに戻ってきて、ハードウェア割り込みラインやステータスインジケータとして機能します。これにより、FPGAはMCUに対して重要な状態を示すことができます。たとえば、ADC変換の準備ができたこと、障害が発生したこと、その他の重要なイベントが発生したことなどを伝えます。

図1:一般的なコプロセッサの図(MCU + FPGA)。(画像提供:CEPD)

図1:一般的なコプロセッサの図(MCU + FPGA)。(画像提供:CEPD)

コプロセッサによるアプローチの強みは、上述の各マイルストーンの成果物を見ればよくわかります。価値は、タスクやフェーズの達成事項を列挙するだけでなく、これらの達成事項が可能にする内容を検証することで評価されます。以下の質問に答えると、マイルストーンの成果物に対する全体的な価値を評価するのに役立ちます。

- プロジェクトの依存関係やボトルネックが解消されたことで、他のチームメンバが進捗を迅速に継続できるようになりましたか?

- マイルストーンの達成により、さらなる並列実行がどのように可能になりますか?

マイクロコントローラによるデジタル信号処理のマイルストーン

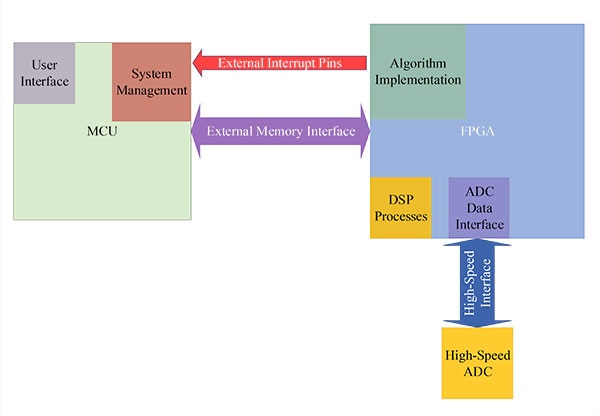

図2:アーキテクチャ - マイクロコントローラによるデジタル信号処理。(画像提供:CEPD)

図2:アーキテクチャ - マイクロコントローラによるデジタル信号処理。(画像提供:CEPD)

このハードウェアアーキテクチャによって可能になる最初の開発段階では、MCUが中心になります。すべての条件が同じであれば、MCUと実行可能なソフトウェアの開発は、FPGAとハードウェア記述言語(HDL)の開発に比べて、リソースと時間がかかりません。したがって、MCUを主要なプロセッサとして製品開発を開始することで、アルゴリズムの実装、テスト、検証をより迅速に行うことができます。これにより、アルゴリズムや論理的なバグを設計の初期段階で発見することができ、信号チェーンのかなりの部分をテストして検証することも可能になります。

この初期段階におけるFPGAの役割は、高速データ収集インターフェースとして機能することです。そのタスクは、高速ADCからのデータを確実にパイプし、データが利用可能であることをMCUに知らせ、そのデータをMCUの外部メモリインターフェースに表示することです。この役割には、HDLベースのDSPプロセスやその他のアルゴリズムの実装が含まれていませんが、非常に重要です。

この段階で行われるFPGAの開発は、製品開発においても、市場に投入されてからも、製品を成功させるための基礎となるものです。低レベルのインターフェースだけに焦点を当てることで、これらの本質的な動作のテストに十分な時間を割くことができます。FPGAがこのインターフェースとしての役割を安定して確実に果たすことができて初めて、自信を持ってこのマイルストーンを終えることができるのです。

この最初のマイルストーンで得られる主な成果物には、以下のような利点があります。

- 増幅、減衰、変換など、すべての信号経路がテストおよび検証されます。

- 最初にアルゴリズムをソフトウェア(C/C++)で実装することにより、プロジェクトの開発期間と労力が削減できます。これは、プロジェクトの実現可能性を見極めてから設計段階への移行を承認する必要がある管理者やその他のステークホルダにとって、大きな価値があります。

- C/C++でアルゴリズムを実装する際に得られた教訓は、ソフトウェアからHDLへの変換ツール(XilinxのHLSなど)を使用することで、HDLの実装に直接反映させることができます。

マイクロコントローラによるシステム管理のマイルストーン

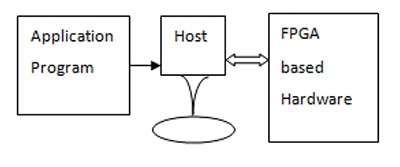

図3:アーキテクチャ - マイクロコントローラによるシステム管理。(画像提供:CEPD)

図3:アーキテクチャ - マイクロコントローラによるシステム管理。(画像提供:CEPD)

このコプロセッサのアプローチによる2つ目の開発段階は、DSPプロセスやアルゴリズムの実装をMCUからFPGAに移すことで定義されます。FPGAは高速ADCのインターフェースを担当していますが、その他の役割を担うことで、FPGAの持つ高速性と並列性を最大限に活用できます。また、MCUとは異なり、複数のDSPプロセスやアルゴリズムチャンネルを実装し、同時に動作させることができます。

設計者は、MCUの実装で得た教訓をもとに、次のマイルストーンに向けて自信を持って取り組めます。前述したXilinxのVivado HLSのようなツールは、実行可能なC/C++コードから合成可能なHDLへの機能変換を行います。現在は、タイミング制約やプロセスパラメータ、その他のユーザー設定を定義して実装する必要がありますが、コア機能は永続的に維持され、FPGAファブリックに変換されます。

このマイルストーンにおいて、MCUの役割はシステムマネージャとなります。FPGA内のステータスおよび制御レジスタは、MCUによって監視、更新、および報告されます。さらに、MCUはユーザーインターフェース(UI)を管理します。このUIは、EthernetやWi-Fi接続を介してアクセスされるウェブサーバの形をとることもあれば、ユーザーが使用するポイントでアクセスできる産業用タッチスクリーンインターフェースの形をとることもあります。MCUの役割がより洗練されたものになったことで、計算負荷の高い処理タスクから解放され、MCUとFPGAの両方がそれぞれに適したタスクに活用されるようになったことが重要です。

このマイルストーンで得られる主な成果物には、以下のような利点があります。

- DSPの処理やアルゴリズムの実装をFPGAで高速に並列実行します。MCUは、応答性に優れた合理的なUIを提供し、製品のプロセスを管理します。

- 最初にMCU内で開発・検証されたことで、アルゴリズムのリスクが軽減され、これらの軽減内容が合成可能なHDLに変換されます。Vivado HLSのようなツールを使用することで、この変換を簡単に行うことができます。さらに、Vivado設計スイートなどの統合されたシミュレーションツールによって、FPGA固有のリスクを軽減することができます。

- プロセスをFPGAに移行しても、ステークホルダが大きなリスクにさらされることはありません。それどころか、FPGAの高速性や並列性がもたらす利点を実感し、楽しむことができます。測定可能なパフォーマンスの向上が確認され、製造に向けてこの設計を準備することに焦点を当てることができます。

製品展開のマイルストーン

計算負荷の高い処理はFPGAで行い、MCUはシステム管理とユーザーインターフェースの役割を担うことで、製品展開の準備ができました。さて、この記事はアルファ版やベータ版のリリースを回避することを提唱するものではありません。それよりも、このマイルストーンで強調したいのは、コプロセッサアーキテクチャによって製品展開にもたらされる機能です。

MCUもFPGAも現場でアップデート可能なデバイスです。FPGAのアップデートもソフトウェアのアップデートと同様にできるよう、いくつかの工夫がなされています。さらに、FPGAはMCUのアドレス可能なメモリ空間内にあるため、MCUはシステム全体のアクセスポイントとして機能し、自身とFPGA両方のアップデートを受け取ることができます。アップデートは、エンドユーザーごとに条件付きでスケジューリング、配信およびカスタマイズできます。最後に、ユーザーやユースケースのログを維持し、特定のビルドの実装と関連付けることができます。製品が現場に置かれた後でも、これらのデータセットから性能を継続的に改善・向上させることができます。

このようなシステム全体のアップデートしやすさは、宇宙での用途で顕著に表れます。製品が発射された後は、メンテナンスやアップデートをリモートで行う必要があります。これは、論理的条件の変更という単純なものから、通信変調方式の更新という複雑なものまであります。FPGA技術が提供するプログラム可能性とコプロセッサアーキテクチャは、放射線硬化性を持つコンポーネントの選択肢を提供しながら、このようなさまざまな機能全体に対応することができます。

このマイルストーンから得られる最後の重要なポイントは、段階的なコスト削減です。また、コスト削減やBOM(部品表)の変更などの最適化もこのマイルストーンで行われます。現場での展開時、安価なMCUや性能の劣るFPGAでも同じように動作することが分かっている場合があります。コプロセッサのおかげで、アーキテクチャ設計者は、アプリケーションのニーズを超えた性能のコンポーネントを使用する必要がありません。さらに、あるコンポーネントが使用できなくなった場合でも、新しいコンポーネントを設計に組み込むことができるアーキテクチャになっています。これは、シングルチップのシステムオンチップ(SoC)アーキテクチャや、高性能なDSPやMCUで製品のすべての処理を行おうとした場合には当てはまりません。コプロセッサアーキテクチャは、機能性と柔軟性をうまく組み合わせたもので、開発段階と市場投入時の両方において、設計者の選択と自由度を高めています。

裏付けとなる研究および関連するケーススタディ

衛星通信の例

簡単にいうと、コプロセッサの価値は、プライマリプロセッシングユニットの負荷を軽減し、タスクをハードウェアで実行することで、加速と合理化を実現することにあります。このような設計上の選択の利点は、計算速度と能力が純粋に向上するとともに、この記事で論じているように、開発コストと開発期間が削減できることです。このような利点が得られる最も魅力的な分野の一つが、宇宙通信システムの分野です。

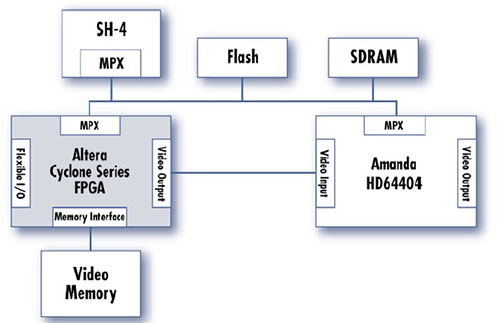

G・プラサード氏とN・ヴァサンタ氏は、その著書「FPGA based hardware as coprocessor(コプロセッサとしてのFPGAベースハードウェア)」の中で、特定用途向け集積回路(ASIC)のような高額な非反復エンジニアリング(NRE)コストや、ハードアーキテクチャのプロセッサのように特定用途向けの制約を受けることなく、FPGA内のデータ処理によって衛星通信システムの計算ニーズを満たす方法を詳しく説明しています。「マイクロコントローラによるデジタル信号処理のマイルストーン」で説明したように、彼らは計算量の多いアルゴリズムの大部分をアプリケーションプロセッサで実行するように設計しています。この出発点から、中央演算処理装置(CPU)のクロックのサイクルの大部分を消費するソフトウェアの主要部分を特定し、これらの部分をHDL実装に移行します。見た目はこれまでに紹介したものとよく似ていますが、アプリケーションプログラムはホスト(プロセッサ)でもFPGAベースのハードウェアでも実現可能なため、独立したブロックとして表現することを選択しています。

図4:アプリケーションプログラム、ホストプロセッサ、FPGAベースのハードウェアが衛星通信の例で使用されています。

図4:アプリケーションプログラム、ホストプロセッサ、FPGAベースのハードウェアが衛星通信の例で使用されています。

ペリフェラルコンポーネントインターコネクト(PCI)インターフェースとホストプロセッサのダイレクトメモリアクセス(DMA)を利用することで、周辺機器の性能が飛躍的に向上します。これは主に、非ランダム化プロセスの改善で見られます。この処理をホストプロセッサのソフトウェアで行った場合、システムのリアルタイムレスポンスに明らかなボトルネックが発生しました。しかし、FPGAに移行すると、次のような利点が見られました。

- 非ランダム化プロセスがボトルネックを発生させることなく、リアルタイムで実行されました

- ホストプロセッサの計算オーバーヘッドが大幅に削減され、望ましいロギングの役割を果たすことができるようになりました。

- システム全体のトータルパフォーマンスがスケールアップしました。

これらはすべて、ASICのようなコストをかけずに、プログラマブルロジックの柔軟性を生かして実現されました[5]。衛星通信には大きな課題がありますが、このアプローチはこれらの要件を検証可能な形で満たし、かつ設計の柔軟性を継続して提供することができます。

車載用インフォテイメントの例

自動車に搭載されたエンターテイメントシステムは、こだわりのある消費者にとって特徴的な機能です。多くの車載用エレクトロニクスとは異なり、これらのデバイスはよく目立ち、優れた応答速度と性能が期待されます。しかし設計者は、現在の設計ニーズと、将来的な機能が必要とする柔軟性との間で板挟みになることが多くあります。この例では、信号処理と無線通信の実装ニーズを用いて、コプロセッサのハードウェアアーキテクチャの長所を説明しています。

車載用エンターテイメントシステムのアーキテクチャとして主流なものの1つに、Delphi Delco Electronics Systemsが発売したものがあります。このアーキテクチャでは、SH-4 MCUおよび、ASICとしてHitachiのHD64404 Amandaペリフェラルが採用されています。このアーキテクチャは、自動車市場の基本的なエンターテイメント機能の75%以上を満たしていましたが、動画処理アプリケーションや無線通信への対応が不十分でした。この既存のアーキテクチャにFPGAを組み込むことで、既存の設計手法にさらなる柔軟性と機能を加えることができます。

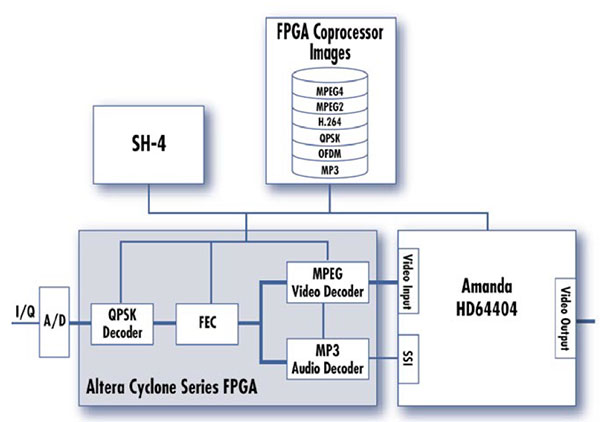

図5:インフォテイメント用FPGAコプロセッサのアーキテクチャ例1

図5:インフォテイメント用FPGAコプロセッサのアーキテクチャ例1

図5のアーキテクチャは、動画処理と無線通信管理の両方に適しています。DSPの機能をFPGAに移すことで、Amandaプロセッサはシステム管理の役割を果たし、無線通信スタックの実装から解放されます。また、AmandaとFPGAの両方が外部メモリにアクセスできるため、システムのプロセッサやコンポーネントの間でデータを素早く交換することができます。

図6:インフォテイメント用FPGAコプロセッサのアーキテクチャ例2

図6:インフォテイメント用FPGAコプロセッサのアーキテクチャ例2

図6の2つ目のインフォテイメントでは、FPGAが、入力される高速アナログデータと、動画アプリケーションに必要な圧縮およびエンコーディング処理の両方に対応できることが示されています。実際に、これらの機能はすべてFPGAに移され、並列処理を利用することで、これらすべてにリアルタイムで対応することができます。

既存のハードウェアアーキテクチャにFPGAを組み込むことで、既存のハードウェアが持つ確かな性能と、柔軟性や将来性を組み合わせることができます。既存のシステムであっても、コプロセッサアーキテクチャは、他の方法では利用できないオプションを設計者に提供します[6]。

ラピッドプロトタイピングの利点

ラピッドプロトタイピングのプロセスでは、タスクを並行して実行し、バグや設計上の問題点を迅速に発見し、データや信号の経路(特にプロジェクトのクリティカルパス内のもの)を検証することで、製品開発のかなりの部分をカバーしようとします。しかし、このプロセスが本当に合理的で効率的な結果を生み出すためには、必要なプロジェクト分野の十分な専門知識が必要です。

慣例では、ハードウェアエンジニア、組み込みソフトウェアまたはDSPエンジニア、そしてHDLエンジニアがいなければなりません。現在では、複数の役割を果たすことができる学際的なプロフェッショナルが多くいますが、これらの取り組みを調整するには、かなりのプロジェクトオーバーヘッドが必要です。

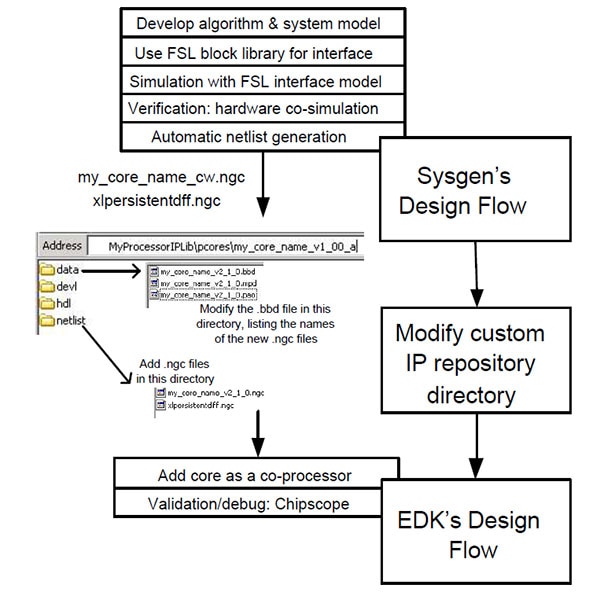

論文「An FPGA based rapid prototyping platform for wavelet coprocessors(ウェーブレットコプロセッサに向けたFPGAベースのラピッドプロトタイピングプラットフォーム)」では、コプロセッサアーキテクチャを使用することで、1人のDSPエンジニアがこれらの役割をすべて、効率的かつ効果的に果たすことができるというアイデアが提案されています。この研究では、MATLABのSimulinkツールを使って、必要なDSP機能の設計とシミュレーションを開始しました。これは、1)必要な性能をシミュレーションによって検証する、2)将来的な設計の選択肢を比較・参照するためのベースラインとする、という2つの主要な機能を果たすものです。

シミュレーションの結果、重要な機能が特定され、FPGA内で合成可能なソフトコアコンポーネントとプロセッサという、異なるコアに分割されました。今回の作業で最も重要だったのは、これらのコアやコンポーネントのインターフェースを定義し、データ交換の性能を、シミュレーションされた必要な性能と比較することでした。この設計プロセスは、Xilinxの組み込みシステムの設計フローと密接に連携しており、以下の図7にまとめられています。

図7:実装設計フロー。

図7:実装設計フロー。

システムを合成可能なコアに分割することで、DSPエンジニアは信号処理チェーンの最も重要な側面に集中することができます。ハードウェアやHDLの専門家でなくても、さまざまなソフトコアプロセッサやコンポーネントを修正したり、配線したり、FPGAに実装したりすることができるようになります。設計者がインターフェースとデータのフォーマットを把握していれば、信号経路を完全にコントロールでき、システムのパフォーマンスを向上させることができるのです。

実証的知見 - 離散コサイン変換のケーススタディ

実証された結果によって、コプロセッサアーキテクチャが組み込みシステムの設計者にもたらす柔軟性が確認されただけでなく、最新のFPGAツールで利用可能な性能向上オプションも示されました。以下に示すような機能拡張は、他のハードウェアアーキテクチャでは利用できないか、あるいは影響が少ない可能性があります。計算量の多いアルゴリズムとして離散コサイン変換(DCT)を選択し、C言語ベースの実装からHDLベースの実装へと進化させたことが、今回の発見の核心です。DCTが選択されたのは、パターン認識やフィルタリングのためにデジタル信号処理で使用されるアルゴリズムであるためです[8]。この実証結果は、筆者と同僚が2020年から2021年の間にXilinx Alliance Partnerの認証を取得するために行った実験に基づいています。

この取り組みには、以下のようなツールやデバイスが使用されました。

- Vivado HLS v2019

- 評価とシミュレーションのために使用したデバイスは、xczu7ev-ffvc1156-2-eでした。

まず、Cベースの実装ですが、DCTアルゴリズムは16ビット数の2つのアレイを受け入れます。アレイ「a」はDCTの入力アレイ、アレイ「b」はDCTの出力アレイです。そのため、データ幅(DW)は16と定義され、アレイ内の要素数(N)は1024/DW、つまり64となります。最後に、DCTマトリクスのサイズ(DCT_SIZE)が8に設定されていますが、これは8 x 8のマトリクスが使用されることを意味しています。

この記事の前提に従って、Cベースのアルゴリズム実装を行うことで、設計者はアルゴリズムの機能を迅速に開発・検証することができます。重要な検討事項ではありますが、今回の検証では、実行時間よりも機能性に重みを置いています。このように重みを置くことができるのは、このアルゴリズムの最終的な実装が、ハードウェアアクセラレーションやループアンローリングなどの技術が容易に利用できるFPGAで行われるためです。

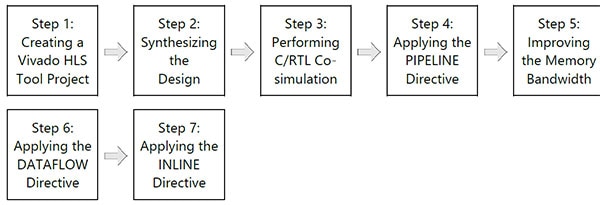

図8:Xilinxが提供するVivado HLSの設計フロー

図8:Xilinxが提供するVivado HLSの設計フロー

DCTコードをVivado HLSツールでプロジェクトとして作成したら、次はFPGA実装のために設計の合成を開始します。アルゴリズムの実行をMCUからFPGAに移行することで得られる最も大きな利点が明らかになるのは、このステップです。参考までに、このステップは、前述した「マイクロコントローラによるシステム管理」のマイルストーンに相当します。

最新のFPGAツールでは、複雑なアルゴリズムの性能を大幅に向上させる一連の最適化と拡張が可能です。結果を分析する前に、いくつかの重要な用語を覚えておく必要があります。

- レイテンシ - ループの全反復を実行するのに必要なクロックサイクル数[10]

- インターバル - ループの次の反復でデータ処理が開始されるまでのクロックサイクル数[11]

- BRAM - ブロックランダムアクセスメモリ

- DSP48E - UltraScaleアーキテクチャ用のデジタル信号処理スライス

- FF - フリップフロップ

- LUT - ルックアップテーブル

- URAM - ユニファイドランダムアクセスメモリ(単一のトランジスタで構成可能)

|

||||||||||||||||||||||||||||||||||||||||

表1:FPGAアルゴリズム実行の最適化結果(レイテンシとインターバル)。

|

表2:FPGAアルゴリズム実行の最適化結果(リソース最適化)。

デフォルト

デフォルトの最適化設定は、Cベースのアルゴリズムを合成可能なHDLに変換した結果がそのまま反映されています。最適化されていないため、他の最適化をより良く理解するための参考パフォーマンスとして使用できます。

パイプライン内部ループ

PIPELINEディレクティブは、Vivado HLSに内部ループをアンロールするように指示し、既存のデータがパイプラインに残っている間に新しいデータが処理されるようにします。そのため、新しいデータは、既存のデータが完了するのを待たずに処理を開始することができます。

パイプライン外部ループ

外部ループにPIPELINEディレクティブを適用することで、外部ループの処理がパイプライン化されます。しかし、内部ループの操作が同時に行われるようになります。これを外部ループに直接適用することで、レイテンシとインターバル時間の両方が半分になります。

アレイパーティション

このディレクティブは、ループの内容をアレイにマッピングし、アレイ内の単一要素へのメモリアクセスをすべてフラットにします。これにより、より多くのRAMを消費することになりますが、このアルゴリズムの実行時間は半分になります。

データフロー

このディレクティブは、設計者が各入力読み込みの間の目標クロックサイクル数を指定できるようにします。このディレクティブは、トップレベルの機能にのみ対応しています。このレベルの影響を受けるループと機能のみが、このディレクティブの恩恵を受けます。

インライン

INLINEディレクティブは、内部と外部両方のループをすべてフラットにします。行プロセスと列プロセスの両方が同時に実行できるようになりました。FPGAのリソースを消費しても、必要なクロックサイクル数を最小限に抑えることができます。

結論

コプロセッサハードウェアアーキテクチャは、開発から製品リリース後まで、設計の柔軟性を維持する高性能プラットフォームを組み込み設計者に提供します。最初にCやC++でアルゴリズムを検証することで、プロセス、データや信号の経路、重要な機能を比較的短時間で検証することができます。そして、プロセッサ負荷の高いアルゴリズムをコプロセッサFPGAに変換することで、設計者はハードウェアアクセラレーションの利点を享受し、モジュラー設計をより多く行うことができます。

部品が古くなったり、最適化が必要になったりしても、同じアーキテクチャによってこれらの変更が可能です。新しいMCUや新しいFPGAを設計に組み込むことができますが、その際、インターフェースにはほとんど手を加えません。さらに、MCUとFPGAの両方が現場でアップデートできるため、ユーザー固有の変更や最適化を現場およびリモートで適用することができます。

つまり、このアーキテクチャは、MCUの開発速度や可用性と、FPGAの性能や拡張性を融合させたものなのです。すべての開発段階で最適化と性能向上が可能なコプロセッサアーキテクチャは、現在の設計だけでなく、それ以降の設計においても、最も厳しい要件を満たすことができます。

免責条項:このウェブサイト上で、さまざまな著者および/またはフォーラム参加者によって表明された意見、信念や視点は、DigiKeyの意見、信念および視点またはDigiKeyの公式な方針を必ずしも反映するものではありません。