デュアルMOSFETによるスイッチングコンバータアプリケーションの電力密度および性能の最大化

2024-02-27

産業用および車載用のスイッチングコンバータやモータドライバには、小型で効率が高く、電気ノイズの発生が少ないMOSFET(金属酸化膜半導体電界効果トランジスタ)が必要です。デュアルMOSFETのアプローチは、これらの要件を満たすのに役立ちます。

2つのMOSFETを1つのパッケージに配置することで、適切に設計されたデュアルMOSFETは、プリント回路基板(PCB)上のスペースを小さくし、寄生インダクタンスを低減し、熱性能を向上させることで、かさばり、そしてコストのかかるヒートシンクを不要にします。このようなデバイスは、数百キロヘルツ(kHz)で干渉なしにスイッチングでき、広い温度範囲で安定して動作し、低リーク電流を示します。しかし、設計者はこれらの部品の利点を十分に理解するために、その動作特性を理解しなければなりません。

この記事では、 Nexperia のデュアルMOSFETの例を紹介し、設計者がそれらを使用して、堅牢で高効率、かつスペースに制約のある設計の課題にどのように対応できるかを説明します。さらに、回路およびPCB設計を最適化する方法を説明し、電熱シミュレーションと損失解析のヒントを提供します。

高速スイッチングにおける高効率化

デュアルMOSFETは、DC/DCスイッチングコンバータ、モータインバータ、ソレノイドバルブコントローラなど、多くの車載用(AEC-Q101)および産業用アプリケーションに適しています。これらのアプリケーションでは、スイッチペアやハーフブリッジトポロジなどでデュアルMOSFETを使用することができます。

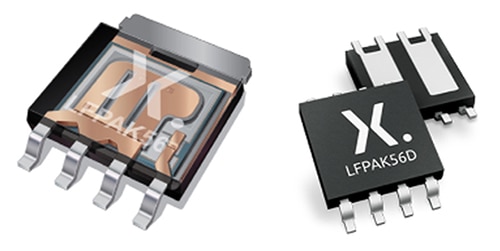

Nexperia LFPAK56D シリーズは、デュアルMOSFETデバイスの注目すべき例です。これらの製品はNexperiaの銅クリップ技術を採用しており、卓越した電流能力、低パッケージインピーダンス、高信頼性を実現しています(図1、右)。この固体銅クリップは、半導体基板からPCBへのはんだ接合部を通して熱放散を改善し、除去された全熱量の約30%をソースピンを通して流すことが可能です。また、銅の断面積が大きいため、オーミックによる電力損失が少なく、寄生ラインインダクタンスを低減することでリンギングを減衰させることができます。

図1:LFPAK56Dパッケージ(右)は独立した2つのMOSFETを集積し、 LFPAK56 シングルMOSFETパッケージ(左)と同様の銅クリップ構造を採用しています。(画像提供:Nexperia)

図1:LFPAK56Dパッケージ(右)は独立した2つのMOSFETを集積し、 LFPAK56 シングルMOSFETパッケージ(左)と同様の銅クリップ構造を採用しています。(画像提供:Nexperia)

高電圧スイッチングコンバータ向けのほとんどの部品と同様に、LFPAK56Dはスーパージャンクション技術を採用しています。この設計により、ドレイン-ソース間のオン抵抗(RDS(on))とゲート-ドレイン間の電荷(QGD)パラメータが低減され、電力損失を最小限に抑えることができます。同じ基板上で2つのMOSFETを動作させることで、ドレイン-ソース間抵抗をさらに低減できます。

スーパージャンクションMOSFETであるLFPAK56Dシリーズは、アバランシェ現象に強く、安全動作領域(SOA)が広くなっています。たとえば、 PSMN029-100HLX トレンチMOSデバイスの各100ボルトMOSFETは、29ミリオーム(mΩ)のRDS(on)を持ち、68ワットを処理でき、最大30アンペア(A)を流すことができます。

また、LFPAK56Dシリーズは、 NXPのSchottkyPlus技術を採用し、スパイク動作とリーク電流を低減しています。たとえば、 PSMN014-40HLDX の典型的なRDS(on) は通常11.4mΩであり、ドレイン-ソース間のリーク電流は極めて低い10ナノアンペア(nA)です。

MOSFETの大電流をフルに活用するには、高熱を放散するようにPCBを設計し、安定した電気接続を確保しなければなりません。十分なビアと大きく厚い銅導体トラックを持つ多層PCBは、高い熱性能を保証します。

熱暴走の回避

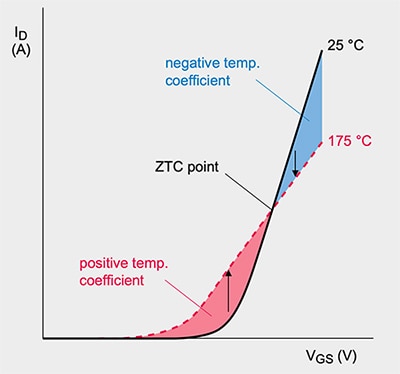

完全にスイッチオンされたパワーMOSFETは熱的に安定していますが、ドレイン電流(ID)が低い場合には熱暴走のリスクがあります。この動作状態では、局所的な加熱によってゲート-ソース間閾値電圧(VGS(th))が低下する傾向があり、デバイスがより容易にオンすることを意味します。このため、電流が増えると加熱が進み、VGS(th)がさらに低下するという正帰還の状況が生じます。

図2は、ドレイン-ソース間電圧(VDS)が一定の場合のこの効果を示しています。VGS が増加するにつれて、ゼロ温度係数(ZTC)として知られる臨界ID が存在します。この電流より上では、負帰還が働き、熱的に安定します(青い領域)。それ以下では、閾値電圧降下が支配的となり、熱的に不安定な動作点となり、熱暴走につながります(赤い領域)。

図2:ZTC点を下回ると、MOSFETは熱によるVGS 低下(赤い領域)により熱暴走に陥る可能性があります。(画像提供:Nexperia)

図2:ZTC点を下回ると、MOSFETは熱によるVGS 低下(赤い領域)により熱暴走に陥る可能性があります。(画像提供:Nexperia)

この効果により、低電流でドレイン-ソース間電圧が高いときのSOAが減少します。このことは、dV/dtの傾斜が急な高速スイッチング動作では大きな問題ではありません。しかし、たとえば電磁干渉を減らすためにスイッチング時間が長くなると、熱不安定性が起こりやすくなり、潜在的に危険な状態になります。

高周波におけるスイッチング損失の低減

高速スイッチングアプリケーション用にスーパージャンクションMOSFETを選択する場合、QGD が低いことが不可欠です。

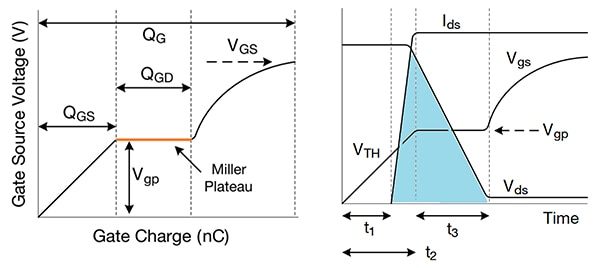

ドレイン、ゲート、ソース間で電圧と電流が同時に大きく変化すると、スイッチング時に大きな電力損失が発生します。QGD が小さいとミラープラトーが短くなり(図3、左)、スイッチングスロープ(dVds/dt)が急峻になり、最終的にスイッチオン時のダイナミックエネルギー損失が低くなります(図3、右の青い領域)。

図3:ミラープラトー(左)が短いということは、スイッチングスロープが急であることを意味し、その結果、ダイナミックロスが小さくなります(右の青い領域)。Vgp はミラープラトーのゲート-ソース間電圧、VTH はゲート閾値電圧、IDS はドレイン-ソース間電流です。(画像提供: Vishay)

図3:ミラープラトー(左)が短いということは、スイッチングスロープが急であることを意味し、その結果、ダイナミックロスが小さくなります(右の青い領域)。Vgp はミラープラトーのゲート-ソース間電圧、VTH はゲート閾値電圧、IDS はドレイン-ソース間電流です。(画像提供: Vishay)

アバランシェエネルギーの制限およびMOSFETの保護

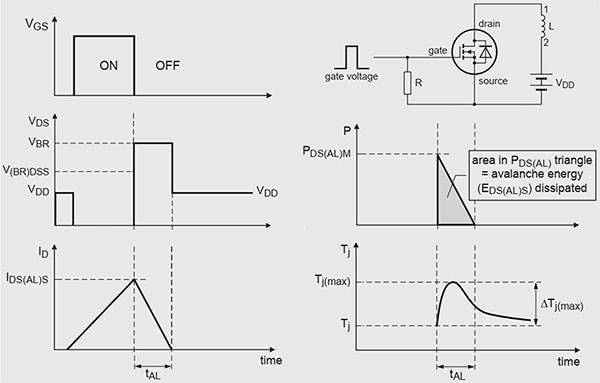

モータ駆動アプリケーションにおけるステータコイルのスイッチオフの瞬間には、崩壊する磁界が電流の流れを維持し、電源電圧(VDD)に重畳する高い誘導電圧をMOSFETに発生させます。しかし、MOSFETボディダイオードの逆方向降伏電圧(VBR)が、この高電圧を制限しています。アバランシェ効果と呼ばれるもので、MOSFETはコイル電流がゼロになるまで、流出する磁気エネルギーをアバランシェエネルギー(EDS)に変換します。これでは、半導体結晶がすぐに過熱してしまいます。

図4は、MOSFETスイッチによる単純なコイル制御と、1回のアバランシェ現象発生前、発生中(時間窓tAL)、発生後の時間信号を示しています。アバランシェのエネルギー散逸量(EDS(AL)S)が大きすぎると、その結果生じる熱が半導体構造にダメージを与えます。

図4:1回のアバランシェ現象発生前、発生中(tAL)、発生後のMOSFETのタイミング信号。(画像提供:Nexperia)

図4:1回のアバランシェ現象発生前、発生中(tAL)、発生後のMOSFETのタイミング信号。(画像提供:Nexperia)

LFPAK56D MOSFETは非常に堅牢に設計されており、Nexperiaの実験室におけるテストによれば、数十億回のアバランシェ現象にも損傷することなく耐えることができます。最大アバランシェエネルギーを考慮すると、コイルドライバ段では、追加のフリーホイールダイオードやクランプダイオードを省くことができ、これらのMOSFETのアバランシェ動作のみを使用することができます。

電熱オンラインシミュレーション

システム効率を向上させるためには、RDS x QGD ような単純な性能指数(FOM)に頼るのでは不十分です。その代わりに、設計者は、MOSFETの損失に起因するものを考慮した、次のようなより正確な損失解析を行う必要があります

- スイッチオン時の導電性

- スイッチオンおよびスイッチオフ時の損失

- 出力静電容量の充放電

- ボディダイオードの導通損失とスイッチング損失

- ゲート静電容量の充放電

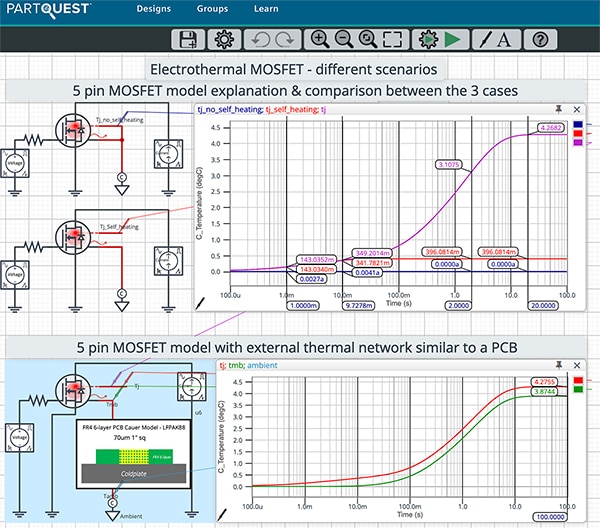

全体の損失を最小限に抑えるには、設計者はMOSFETのパラメータと動作環境の関係を理解する必要があります。このため、Nexperiaは、電気的性能と熱的性能を組み合わせ、すべての重要なMOSFETの動作を表現するMOSFETの精密電熱モデルを提供しています。開発者は、 PartQuest Explore オンラインシミュレータを使用するか、SPICEおよびVHDL-AMS形式のモデルを選択したシミュレーションプラットフォームにインポートすることができます。

本記事執筆時点では、LFPAK56D MOSFETの電気モデルのみが入手可能です。したがって、以下の熱シミュレーション例では、異なるタイプのMOSFETである BUK7S1R0-40Hを扱います。

IAN50012パワーMOSFET用電熱モデル の対話型実験では、36.25Aの負荷電流を流した後のBUK7S1R0-40H MOSFETの3つの発熱シナリオをシミュレートしています。図5は、左側の3つのシミュレーションセットアップを示しています。

図5:PartQuest Exploreオンラインシミュレータを使用したMOSFETの電熱シミュレーション。(画像提供:Nexperia)

図5:PartQuest Exploreオンラインシミュレータを使用したMOSFETの電熱シミュレーション。(画像提供:Nexperia)

上の「tj_no_self_heating」ケースでは、ジャンクションと取り付けベースは、熱抵抗(Rth)なしで0°Cの周囲温度(Tamb)に直接結合されています。中間のケース「tj_self_heating」では、チップはRth-jを介して結合され、Tj は約0.4°Cまで上昇します。下のケースは、ヒートシンク付き6層FR4基板のRth_mb を介して周囲温度に結合された取り付けベース(mb)を示しています。Tmb (緑)は3.9°C、Tj (赤)は4.3°Cまで上昇します。

まとめ

超低損失LFPAK56D MOSFETは、高速スイッチングコンバータやモータドライバに優れた効率と電力密度を提供します。ここで説明する回路と熱PCB設計の考慮事項および電熱シミュレーションは、設計者が堅牢で高効率、かつスペースに制約のある設計の課題を克服する方法を示しています。

免責条項:このウェブサイト上で、さまざまな著者および/またはフォーラム参加者によって表明された意見、信念や視点は、DigiKeyの意見、信念および視点またはDigiKeyの公式な方針を必ずしも反映するものではありません。