アナログの基礎:サンプルアンドホールド回路の働きとADCの確度を確保する方法

DigiKeyの北米担当編集者の提供

2020-04-22

「実」世界のアナログ信号をアップストリームで処理できるデジタル信号に変換することは、オーディオ録音からモノのインターネット(IoT)、産業用IoT(IIoT)、そして今やモノの人工知能(AI)(AIoT)にまで至る電子システムの基本的機能です。しかし、それを効果的かつ効率的に行うには、根本原理と、見過ごされがちなステップに対する一定の理解が必要です。

たとえば、A/Dコンバータ(ADC)の入力に印加される典型的なアナログ信号の振幅が連続的に変化していて、変換の始めと終わりで異なっている場合、どれだけ正確に信号が「ホールド」され、変換前に「サンプリング」されるのでしょうか。この振幅の変化またはスキューは、信号変換に要する時間の長い高分解能ADCの場合に特に重大な誤差を生じることがあります。設計者にとっての課題は、この誤差の原因を理解し排除することです。

この記事では、ADCにサンプルアンドホールド(S&H)回路またはトラックアンドホールド(T&H)回路を使うことで、振幅のスキューを防ぐ方法を紹介します。S&H(またはT&H)回路は、実際の入力サンプリングを行うもので、入力アンチエイリアスローパスフィルタとADCの間で動作します。記事では、S&H ICの特性および選択基準について検討し、S&H回路内蔵ADCを見ていきます。各種アプリケーション向けにさまざまな特性を有するデバイスの例としてTexas Instruments社、Maxim Integrated社、Analog Devices社の製品を説明のために使用します。

ADCにおけるサンプルアンドホールド回路の役割

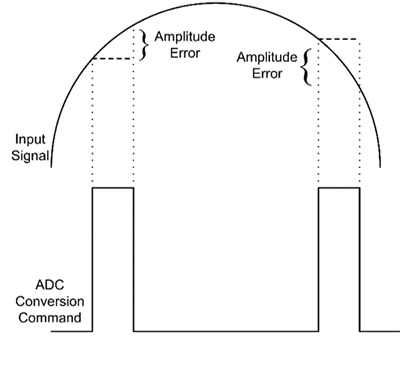

直流以外の信号をADCの入力に加えた場合、振幅が連続的に変化します。しかし、A/D変換プロセスには有限の時間を要するため、その間にADC入力の振幅が変化します(図1)。問題になる可能性のある誤差が生じるのは、この振幅の傾斜です。

図1:ADCに変動する入力信号が印加されると、振幅誤差(上)がデジタル化処理(下)中の信号振幅の変動によって生じます。(画像提供:DigiKey)

図1:ADCに変動する入力信号が印加されると、振幅誤差(上)がデジタル化処理(下)中の信号振幅の変動によって生じます。(画像提供:DigiKey)

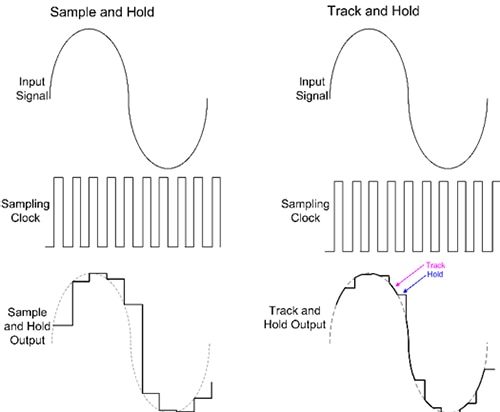

ADCにおける振幅のスキューを防ぐには、信号のサンプリングおよび変換処理中に一定の振幅を維持します。これは、ADCにS&H回路またはT&H回路を使うことで実現します(図2)。

図2:S&H回路(左)とT&H回路(右)の主な違いはトラック期間の長さ。S&H回路では短く、T&H回路では長いです。(画像提供:DigiKey)

図2:S&H回路(左)とT&H回路(右)の主な違いはトラック期間の長さ。S&H回路では短く、T&H回路では長いです。(画像提供:DigiKey)

どちらのタイプの回路も、入力信号をサンプリングし、サンプリングした電圧を変換プロセスの間、一定に維持します。T&H回路の出力(右)はサンプリングの合図を受け取るまで入力信号を追跡します。次にサンプル値をADCが変換する間、維持します。S&H回路の方がサンプルアパーチャが短く、出力はサンプリングした一連のレベルです(左)。T&HとS&Hの重要な違いはトラック期間の長さです。S&Hは非常に短く、T&Hの方は著しく長いです。どちらの回路も、信号入力に接続されているストレージコンデンサを分離する高速スイッチに依存しています。この記事では以降、S&HをS&HおよびT&Hと同義に使います。

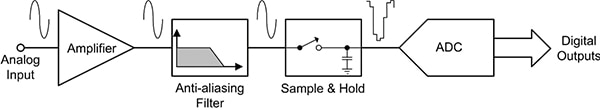

S&H段は、実際の入力サンプリングを行うもので、入力アンチエイリアスローパスフィルタとADCの間で動作します。このローパスフィルタは、アンチエイリアス帯域制限を行いますが、エイリアシング防止のためサンプリングの前に信号の帯域制限を行うには、S&H回路よりも前になければなりません(図3)。

図3:デジタイザの信号経路中、S&H回路はアンチエイリアスローパスフィルタとADCの間に位置します。(画像提供:DigiKey)

図3:デジタイザの信号経路中、S&H回路はアンチエイリアスローパスフィルタとADCの間に位置します。(画像提供:DigiKey)

S&H回路より前の信号は、すべてアナログ信号であることに注意してください。S&H回路の出力はサンプリングされた波形で、ADCに送られます。

代表的なS&Hデバイス

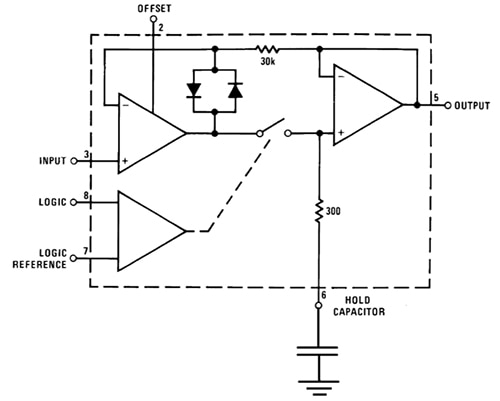

Texas Instruments社製S&H集積回路(IC)LF398MX/NOPBのブロック図(図4)は基本的な回路構成を示します。S&H回路は高速スイッチと高品質コンデンサを使用して実装されています。LF398MX/NOPBの場合、コンデンサはICの外部です。スイッチが閉じると、コンデンサが入力信号電圧のレベルまで充電されます。スイッチが開いても、コンデンサはこの電圧をADCによってデジタル化されるまで維持します。このS&H回路は、FETとバイポーラトランジスタを組み合わせたバイFET技術の使用により、高DC確度(標準値0.002%)、極低電圧ドループ(標準値83µV/s未満)で高速アクイジション(振幅誤差0.01%で6µs未満)を実現します。内蔵アンプは、スイッチとホールドコンデンサのバッファとして働きます。

このS&H回路のアクイジション時間は、ホールドコンデンサの値(範囲は0.001~0.1µF)によって決まります。外部のホールドコンデンサは、低誘電吸収かつ低リークでなければなりません。ポリスチレン、ポリプロピレン、テフロンのコンデンサが推奨されます。

図4:Texas Instruments社が提供するLF398MX/NOPBのS&H回路のブロック図には、主な部品である高速スイッチと外付けホールドコンデンサが示されています。(画像提供:Texas Instruments)

図4:Texas Instruments社が提供するLF398MX/NOPBのS&H回路のブロック図には、主な部品である高速スイッチと外付けホールドコンデンサが示されています。(画像提供:Texas Instruments)

S&H特性

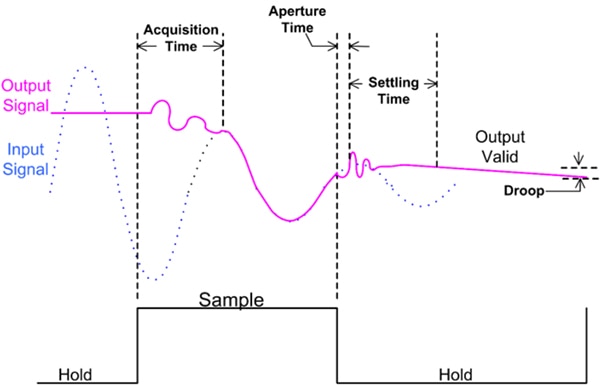

S&Hデバイスには、その動作を記述するために特有の用語が多数あります(図5)。

図5:一般的なS&H回路の動特性の定義には、アクイジション時間、整定時間、アパーチャ時間、振幅ドループなどがあります。(画像提供:DigiKey)

図5:一般的なS&H回路の動特性の定義には、アクイジション時間、整定時間、アパーチャ時間、振幅ドループなどがあります。(画像提供:DigiKey)

アクイジション時間とは、サンプルモードへの切り換えからS&H回路が入力信号の追跡を開始するまでの時間です。これは、ホールドコンデンサの値とスイッチおよび信号経路の直列抵抗の関数です。ホールドモードに戻る時、デバイスが入力の追跡を終了して値の保持を開始するまでに時間遅延がある場合があります。これがアパーチャ時間です。アパーチャ時間は、ドライバおよびスイッチの伝播遅延の関数です。アパーチャ不確定性またはアパーチャジッタとは、クロック変動およびノイズによる、アパーチャ時間の変動です。

ホールドモードに入ると、デバイスがそのモードに入った時点からホールド値の誤差範囲内に落ち着く時点までの、整定時間またはホールド整定時間と呼ばれる時間があります。整定時間の一部には、スイッチドライバとホールドコンデンサの間で望ましくない電荷の移動がある場合があります。これをホールドステップ誤差またはペデスタル誤差と呼びます。ホールドステップは通常mVの範囲の大きさで、その影響は、信号のフルスケール範囲を可能な限り大きく保つことで最小化できます。

S&H回路の最短のサンプリング期間は、アクイジション時間、アパーチャ時間、整定時間の和です。 可能な最大サンプリングレートは、アクイジション時間、アパーチャ時間、整定時間の和の逆数です。

ホールドモードの間、S&H回路のホールド値は、ホールドコンデンサからのリークのため減少する場合があります。この電圧の差分をドループと呼びます。通常、これはドループ率(単位はmV/s)として記載されます。

S&H回路の構成

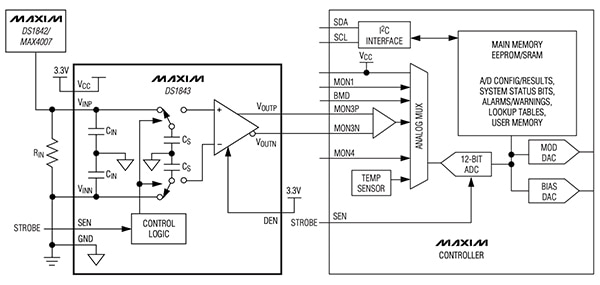

S&H ICは、デバイスのニーズに合うように多様な構成の製品があります。加速度計や歪ゲージ、光電流モニタのような差動出力トランスデューサとのインターフェース接続など、差動入力が必要なデバイスを考えてみましょう。Maxim Integrated社のDS1843D+TRLは、そうしたデバイス向けのS&H ICのよい例です(図6)。

図6:この代表的動作回路が示すように、Maxim Integrated社のDS1843+TRLは、差動サンプリングの実行にデュアルホールドコンデンサを使用する差動S&Hです。(画像提供:Maxim Integrated)

図6:この代表的動作回路が示すように、Maxim Integrated社のDS1843+TRLは、差動サンプリングの実行にデュアルホールドコンデンサを使用する差動S&Hです。(画像提供:Maxim Integrated)

図のDS1843+TRLは、代表的なバーストモード受信信号強度インジケータ(RSSI)測定向け光伝送路アプリケーションの場合です。Maxim Integrated社のDS1842/MAX4007は、その基準入力に付加されたアバランシェフォトダイオードからの電流を反映する電流モニタです。出力電流は抵抗器RINに送って、電圧に変換します。この電圧はDS1843によって差動測定されます。DS1843は完全差動サンプリングスイッチおよびコンデンサCSと、差動出力バッファで構成されています。このS&Hは、2つの5pFコンデンサの一方を正の差動入力に、他方を負の差動入力に接続して使います。小さな静電容量値によって、短いアクイジション時間が保証されます。このデバイスの高速サンプリング(アクイジション)時間は300ns未満です。S&H回路のホールド時間は100µs超です。

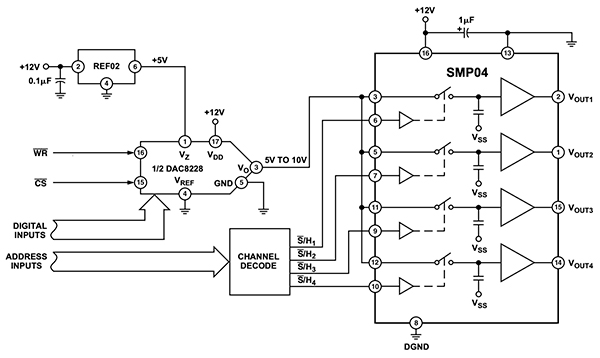

単一ICパッケージに4つまたは8つのS&H回路を内蔵したデバイスが販売されています。一例として、Analog Devices社製クワッドS&HのSMP04ESZ-REELがあります。SMP04ESZ-REELは、4つのS&H回路を単一パッケージに収めたCMOSデバイスで、7µsのアクイジション時間と、わずか2mV/sのドループ率が特長です(図7)。

また、図7は、S&H回路をD/Aコンバータ(DAC)と組み合わせた使い方を示しており、この場合は、DACでのコード遷移による過渡出力またはグリッチ出力を防止します。

図7:Analog Devices社製クワッドS&HのSMP04は、独立した4つのS&H回路および対応するバッファアンプを内蔵。図の回路は、SMP04を使用してDACの出力を4つのチャンネルに分岐させています。(画像提供:Analog Devices)

図7:Analog Devices社製クワッドS&HのSMP04は、独立した4つのS&H回路および対応するバッファアンプを内蔵。図の回路は、SMP04を使用してDACの出力を4つのチャンネルに分岐させています。(画像提供:Analog Devices)

図のSMP04はDAC出力の分岐に使われており、単一のDAC出力を4つのマルチプレクサチャンネルに分岐させています。S&H回路は、DACの出力をグリッチ後まで選択的に遅延させてDAC出力を平滑化するために使うことができます。

複数のS&H回路を使ってマルチプレクサ入力をパイプライン化することでADCのスループットを大きくすることができます。その場合、複数のS&H回路を共通のマルチプレクサ出力に接続します。ADCが1つのS&H回路に接続され、これが入力レベルを変換用にホールドします。1番目のS&H回路は自由に他のマルチプレクサチャンネルに接続できるのに対して、他のS&H回路は他のマルチプレクサチャンネルと固定接続しておき、順にADCに接続します。このパイプライン化手法により、ADCの信号経路におけるS&H回路のアクイジション時間を排除できます。

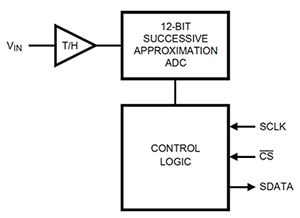

ADCの多くは、S&H回路またはT&H回路をその集積パッケージに内蔵しています。一例がTexas Instruments社の12ビット逐次比較レジスタ(SAR)ADCのADC121S021CIMFXで、毎秒50~200キロサンプル(kS/s)の範囲のサンプリングレートで動作するT&H回路を内蔵しています。この製品は配線レイアウトを簡素化する高速シリアル出力バスを特長としています(図8)。

図8:Texas Instruments社のADC121S021は、T&H回路を内蔵した12ビットシングルチャンネルSAR ADCです。(画像提供:Texas Instruments)

図8:Texas Instruments社のADC121S021は、T&H回路を内蔵した12ビットシングルチャンネルSAR ADCです。(画像提供:Texas Instruments)

このADCはT&H回路を内蔵している点で多くのADC集積回路の典型であり、プリント基板レイアウトを簡素化し、部品点数を削減することができます。外付けのT&H回路は、差動入力接続、マルチプレクス入力などの特殊な構成や、ADCがT&H回路またはS&H回路を内蔵していない場合に使われます。

まとめ

オーディオ録音から最先端のIIoTやAI解析に至るまで、最も基本的な電子機能であるアナログ信号のデジタル信号への変換においては、S&H回路またはT&H回路に注意する必要があります。これらは、A/D変換プロセスにおける電圧の傾斜誤差を最小化するために不可欠で、変換時のADCへの入力電圧を一定にホールドします。S&H回路はADCが内蔵している場合と外付けされている場合がありますが、アンチエイリアスローパスフィルタとADCの間の信号経路になければなりません。上述したように、これらにはさまざまな設計用途に適合するために、多くの構成(シングル、差動、単一IC内に複数回路を内蔵)があります。このような用途は、DACのコード遷移による過渡出力またはグリッチ出力の防止などを含めて拡大しています。

お勧めの記事

免責条項:このウェブサイト上で、さまざまな著者および/またはフォーラム参加者によって表明された意見、信念や視点は、DigiKeyの意見、信念および視点またはDigiKeyの公式な方針を必ずしも反映するものではありません。