多相降圧コンバータに結合インダクタを使用して効率を向上

DigiKeyの北米担当編集者の提供

2025-04-23

多相降圧コンバータは、データセンター、人工知能(AI)システム、通信インフラなどの12Vアプリケーションで広く使用されています。これらの使用例に共通するテーマは、性能を損なわず、物理的な設置面積を増やすことなく効率を向上させる必要性です。

有望なアプローチのひとつに、結合インダクタ(CL)があります。CLは相間の相互インダクタンスを利用することで、大幅な電流リップルのキャンセルを可能にし、従来のレイアウトとの互換性を保ちながら大幅な効率向上を実現します。

この記事では、多相降圧コンバータの設計者が直面する効率とレイアウトの課題について簡単に説明します。その後で、CLを紹介し、効率改善を検証する実験結果を示し、Analog DevicesのコンバータでCLがどのように適用されているかを示します。

従来の多相降圧コンバータの効率に関する課題

高性能コンピューティングおよび通信システムでは、電源供給における効率損失が、システムのコスト、信頼性、および熱管理に大きな影響を与える可能性があります。従来の多相降圧設計の設計者は、この点で、特にスイッチング損失と交流損失が顕著になる軽負荷条件下で、しばしば課題に直面します。

同時に、パワー段のレイアウトや機械的な制約により、性能向上のための利用できる選択肢が制限されます。多くのシステムでは、部品サイズを大きくする余地はほとんどなく、プリント回路基板(プリント基板)のレイアウトを変更することは、一般的なフットプリント戦略の前では実行不可能な場合があります。

その結果、パワーアーキテクチャを大幅に変更することなく、より高い効率を実現するアプローチに強い関心が寄せられています。このようなソリューションは、同じフットプリントを維持し、既存の出力静電容量(CO)を使用でき、幅広い負荷条件にわたって過渡性能を維持することが理想的です。

CLは、従来の設計と同じ物理的フットプリントで、リップルの低減とスイッチング損失の改善を可能にすることで、こうした要求に対応します。

CLがパワー変換を改善する方法

CLは、レイアウトを変更することなく多相降圧コンバータの効率を改善する効果的な方法を提供します。各相を電気的に独立したものとして扱う従来の設計とは異なり、CLは相間の相互作用を可能にする標準的な磁気構造を共有しています。

この相互作用を左右するのは、漏れインダクタンス(Lk)と相互インダクタンス(Lm)という2つの重要なパラメータです。漏れインダクタンスは、従来の設計における相間インダクタンス(L)と同じように動作、一方、相互インダクタンスは相間に磁気結合をもたらします。一方の相で電流が増加すると、他方の相では電流変化を打ち消す方向に電圧が誘起され、リップル電流が大幅にキャンセルされます。

式1と式2 は、従来のディスクリートインダクタ(DL)設計(dILDL)とCL設計(dILCL)の予想されるリップル電流を定義しています。これらの電流は、入出力電圧(VIN、VO)、インダクタンスL、Lk、Lm、スイッチング周波数(FS)、および性能指数(FOM)に依存します。

式1

式1

式2

式2

ここで、式の記号の意味は次のとおりです。

ρ = 結合係数 = Lm/L

D = デューティサイクル

Nph = 結合相の数

式3は、FOMの計算方法を示しています。この式は、さまざまなパラメータの関数としてリップルのキャンセル程度を捉えたものです。具体的には、FOMはρ、Nph、およびDに左右されます。

![FOM = (1 + ρ/ρ+1 x 1/Nph-1) / 1- [(Nph - 2 x j - 2) + j x (j+1)/ Nph x D + Nph x D x (Nph -2 x j-1) + j x (j +1)/Nph x (1 - D)] x ρρ+1/Nph-1 式3](http://sc-b.digikeyassets.com/-/media/Images/Article%20Library/TechZone%20Articles/2025/April/Use%20Coupled%20Inductors%20in%20Multiphase%20Buck%20Converters%20to%20Improve%20Efficiency/article-2025april-use-coupled-inductors-in-multiphase-equation3.jpg?la=en&ts=73a7c156-06a3-4b9c-aba7-4440849523dd) 式3

式3

ここで、式の記号の意味は次のとおりです。

j = floor(D×Nph)

FOMは多くの要因に影響を受けますが、結合係数ρが重要な役割を果たします。この点を説明するのに、実際の例を考えてみましょう。

結合インダクタのリップル電流の評価

図1は、VINが12V、VOが1V、Dが~0.083、従来のDL値が100ナノヘンリー(nH)のアプリケーションのFOM値を示してます。この設計と同じCOタンクで過渡性能を維持しながらこの設計をCLにアップグレードするには、CLのLkを100nHにする必要があります。これにより、Lmが設計変数として残ります。Lmの値が大きいほどリップルは小さくなりますが、控えめな260nHのLmで十分です。

図1:さまざまなLm/Lk値に対する4相CLのFOM値をDの関数として示しています。(画像提供:Analog Devices, Inc.)

図1:さまざまなLm/Lk値に対する4相CLのFOM値をDの関数として示しています。(画像提供:Analog Devices, Inc.)

このかなり控えめな設計でも、リップルを低減することができ、スイッチング周波数を低下させることが可能です。これは、さまざまなインダクタ構成とスイッチング周波数の電流リップルを比較した図2に示されています。このグラフは、400キロヘルツ(kHz)で動作するCLが、800kHzで動作する従来の設計よりも低いリップルを維持していることを示しています。

図2:VIN=12VにおけるDL=100nH(800kHz)およびCL=4 × 100nH(800kHz、400kHz)の電流リップル(VOの関数として)。(画像提供:Analog Devices, Inc.)

図2:VIN=12VにおけるDL=100nH(800kHz)およびCL=4 × 100nH(800kHz、400kHz)の電流リップル(VOの関数として)。(画像提供:Analog Devices, Inc.)

スイッチング周波数の低下は、トランジスタのスイッチング損失、MOSFETのボディダイオードのデッドタイム損失、逆回復損失、ゲート駆動損失などのスイッチング損失の低減に直結します。これらの周波数依存損失は、スイッチング周波数を低下させると比例して減少し、結果として効率が大幅に向上します。

効率向上は軽負荷時に最も顕著で、交流損失は出力電流に関係なく固定されるため、より顕著となります。しかし、その利点は全負荷範囲に及びます。図3は、結合インダクタを用いた8相システムを400 kHzで、従来設計の600 kHzと比較した実験結果を示しており、ピーク効率で約1% 、全負荷で約0.5%の改善が確認されています。

図3:共通のフットプリントを持つ8相DL=100nH(破線の曲線)と2 × CL=4 × 100nH(実線の曲線)設計の効率測定比較を示しています。(画像提供:Analog Devices, Inc.)

図3:共通のフットプリントを持つ8相DL=100nH(破線の曲線)と2 × CL=4 × 100nH(実線の曲線)設計の効率測定比較を示しています。(画像提供:Analog Devices, Inc.)

過渡応答を犠牲にすることなく効率を向上

特に、これらの効率向上は、過渡性能を損なうことなく達成されています。図4は、4相降圧コンバータの過渡特性を、ディスクリートインダクタを使用した8相設計(600kHzでDL=100nH)と、VIN=12V、VO=0.9V、135Aの負荷ステップで2つのCLを使用した構成(400kHzで2×CL=4×100nH)の波形を比較しています。同じ電流スルーレートとCOを使用すると、同様の過渡応答が得られます。

図4:VIN =12V、VO = 0.9V、135A負荷ステップにおける8相DL=100nH(600kHz)と2 × CL= 4 × 100nH(400kHz)の過渡特性を示します。(画像提供:Analog Devices, Inc.)

図4:VIN =12V、VO = 0.9V、135A負荷ステップにおける8相DL=100nH(600kHz)と2 × CL= 4 × 100nH(400kHz)の過渡特性を示します。(画像提供:Analog Devices, Inc.)

CLのスイッチング周波数が低いため、一般的にフィードバック帯域幅が狭くなりますが、この制限を相殺する2つの要因があります。すなわち、多相構成の固有の利点と、結合設計による位相マージンの向上です。この位相マージンの向上は、1つの相で過渡事象が発生してデューティサイクルが変化すると、すべての結合された相電流が同時に応答するためです。

損失の低減は熱性能の向上につながり、これにより長期的な信頼性を向上し、熱的に制約のあるシステムの冷却要件を低減できる可能性があります。これらすべての利点は、既存のレイアウトとの互換性を維持しながら実現されます。

多相降圧コンバータの部品選定

効率的な多相降圧コンバータを実現するには、電圧レギュレータコントローラ、パワー段集積回路(IC)、CLという3つの主要部品に注目する必要があります。コントローラが位相タイミングと同期を管理し、パワー段が大電流スイッチングを処理し、CLがリップルキャンセルを行い効率の向上を実現します。

コントローラには、Analog DevicesのMAX16602GGN+T(図5)が最適な選択です。56-QFN(7mm × 7mm)パッケージで提供され、8相レールと独立した単相レールをサポートしています。主な機能には、自律的な位相遮断、PMBus経由のテレメトリ、統合された故障保護とログ記録、および内部1.8Vバイアスレギュレータなどがあります。これらの機能により、多相電圧レギュレータシステムにおける精密な制御、部品点数の削減、過渡応答の向上が実現します。

図5:MAX16602GGN+T電圧レギュレータコントローラは最大8相をサポートします。(画像提供:Analog Devices, Inc.)

図5:MAX16602GGN+T電圧レギュレータコントローラは最大8相をサポートします。(画像提供:Analog Devices, Inc.)

パワー段には、Analog DevicesのMAX20790GFC+Tが使用できます(図6)。このスマートパワー段は、MOSFET、ゲートドライバ、電流センシングを1つの12-FC2QFN(3.25 × 7.4mm)パッケージデバイスに統合しています。300kHz~1.3メガヘルツ(MHz)のスイッチング周波数で動作し、設計者はCL設計の性能を最適化できます。主な機能としては、コントローラのPMBusを介したテレメトリや故障報告、および高度な自己保護機能などがあります。

図6:MAX20790GFC+Tスマートパワー段は、MOSFET、ゲートドライバ、電流センシングを1つのデバイスに統合しています。(画像提供:Analog Devices, Inc.)

図6:MAX20790GFC+Tスマートパワー段は、MOSFET、ゲートドライバ、電流センシングを1つのデバイスに統合しています。(画像提供:Analog Devices, Inc.)

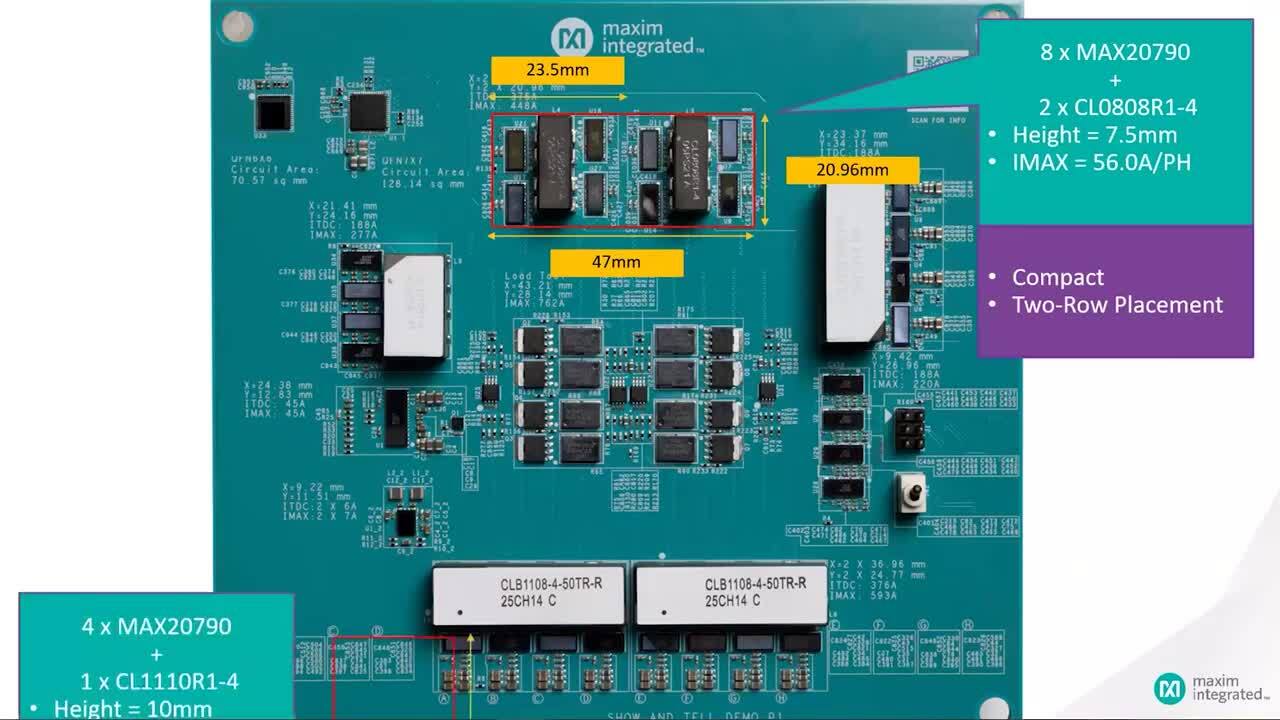

適切なCLの例としては、Eaton CLB1108-4-50TR-R(図 7)があり、これは4つの密結合された50nH相を1つのパッケージに統合しています。このコンポーネントの構造は、高い飽和電流と熱性能をサポートし、要求の厳しいAIやデータセンターのワークロードに適しています。

図7:CLB1108-4-50TR-Rは4 × 50nHの結合インダクタです。(画像提供:Eaton)

図7:CLB1108-4-50TR-Rは4 × 50nHの結合インダクタです。(画像提供:Eaton)

一般的な構成では、MAX16602コントローラは最大8つのMAX20790パワー段を駆動し、各出力相はデュアル4相CLの対応する巻線に接続されます。従来の設計と比較して、この構成は、同じ物理的フットプリントと過渡性能を維持しながら、電源効率の測定可能な改善を実現します。

評価用ハードウェアによる結合インダクタ設計のテスト

Analog DevicesのMAX16602CL8EVKIT#評価キット(図8)は、CLソリューションを検討する設計者に、テストと開発のための便利なプラットフォームを提供します。このボードは、MAX16602コントローラとMAX20790パワー段ICの機能を、結合インダクタと組み合わせて実証するために特別に設計されています。

図8:MAX16602CL8EVKIT#は、多相降圧コンバータの設計検討に適しています。(画像提供:Analog Devices, Inc.)

図8:MAX16602CL8EVKIT#は、多相降圧コンバータの設計検討に適しています。(画像提供:Analog Devices, Inc.)

評価キットは、これらのコンポーネントをいかに効果的に統合できるかを示す実用的なリファレンス設計です。このキットには、8相パワー変換ソリューションをサポートするために必要なすべての回路が含まれており、過渡応答などの主要パラメータの監視ができる包括的な測定ポイントが設けられています。

まとめ

CLは、多相降圧コンバータの設計に大きな利点をもたらします。相間に相互インダクタンスを用いることにより、これらの部品はリップル電流をキャンセルし、スイッチング周波数の低減と全体的な効率の向上を可能にします。重要なことは、物理的な実装面積を増やしたり、また過渡性能を損なったりすることなく、これらの利点を達成できることです。コントローラやパワー段のチップセットと組み合わせることで、これらのソリューションは、従来のトポロジから、より効率的な磁気結合の代替品に変更を計画している設計者に実用的な方向性を提供します。

免責条項:このウェブサイト上で、さまざまな著者および/またはフォーラム参加者によって表明された意見、信念や視点は、DigiKeyの意見、信念および視点またはDigiKeyの公式な方針を必ずしも反映するものではありません。