MCUアプリケーションにおけるウォッチドッグ機能の高まる重要性

Electronic Products の提供

2014-11-26

マルチスレッド、リアルタイム、およびマルチタスキング組み込みシステムのすべての複雑さにより、マイクロプロセッサがいつ誤動作しているかを知るのはますます難しくなっています。 非常に多くのサービスルーチンが幾分独立して動作している状態で、いくつかのルーチンが動作している一方、他のルーチンがロック状態だったり、機能していなかったり、または無意味なコードを実行している可能性が大いにあります。

その結果として、現在、組み込みシステムの設計者が、より低レベルのサービスルーチン、または正常に機能していないコアで発生している障害から全体のシステムを保護することはより困難です。

この記事では、より高度なウォッチドッグ機能の進化するニーズ、そして信頼できるMCU動作を確保するのに技術者が使用できる技術に目を向けます。 ハードウェアで外部で、そしてソフトウェアで内部で対処される必要があるその短所について考察し、ウォッチドッグ部品の例に目を向けます。 この記事で言及されているすべての部品、データシート、チュートリアル、および開発リファレンスは、DigiKeyウェブサイトでご覧いただけます。

シンプルな保護

ウォッチドッグ機能の必要性は、4ビットから高度な32ビットのマシン以上にわたります。 危険な可能性のある状況でシンプルなプロセッサが実行するのを目にするのは珍しくはありません。 たとえば、スロットル制御ループには、安定した閉ループ制御を提供するために、ローカルのシンプルな混合信号8ビットマイクロコントローラのみが必要である可能性があります。 それは、車のCANバスにわたってコマンドを取得し、リモートカーコンピュータからすべての処理をオフロードすることができます。 しかし、そのシンプルなプロセッサに障害が発生すると、フルスロットルが致命的になる可能性があります。

実質的にあらゆる現代的なマイクロコントローラには、ソフトウェア制御のウォッチドッグ機能を実装するのに使用できる専用ウォッチドッグハードウェアブロックまたは汎用タイマなどの何らかの基本的なウォッチドッグ機能が含まれていると言ってよいでしょう。 これらはすべて、プロセッサのシステムクロックに同期されます。

プロセッサがより高度になるにつれて、プロセッサ内のクロッキング構造やクロック分配も高度になる可能性があります。 発振器は、たとえばESDヒットの影響を特に受けやすく、クロックが機能しなくなるど、同期ウォッチドッグは役に立たなくなります。

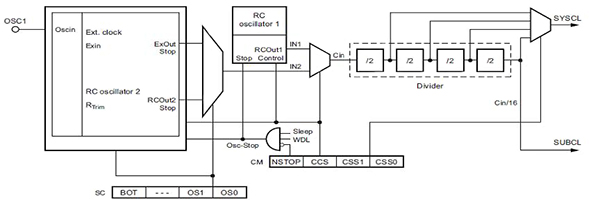

R/C発振器および時定数は古風であるものの、フォールバックまたはバックアップとして独立したクロッキング機構およびリセット機構を提供することができます。 同様に、冗長内部および外部発振器は、不利な障害中にモニタリング回路を動作し続けるために、ある種のハートビートを提供することができます。 また、クロックの選択可能な統合は、ツリー内のクロックの位置と同様に重要です(図1)。

図1:バックアップR/C発振器とシステムクロックを組み合わせることで、システムクロックが破損した場合にウォッチドッグ機能向けの電力節約および信頼できる独立したバックアップクロックを実現することができます。 ここで2つのR/C発振器がいかにして使用されるかにご留意ください。

同じことが、低電圧検出回路に当てはまります。 内部基準電源を使用して基本的な精度を達成できる一方で、コンパレータ、および検出器、外部回路は、より高い分解能とより高精度の電圧レベル選択性を提供する可能性があります。 たとえば、電圧障害モードソフトウェアの一部に、EEPROMへの書き込みが含まれる場合、正しくシャットダウンする前にEEPROM書き込みを実行するのに十分な時間を容量性電荷蓄積に与えるために、低電圧検出器閾値を早くトリップするほうがよいでしょう。 現代の電圧検出器は、すべてのエネルギーの正確な使用のために最小0.05Vの電圧分解能を達成することができます。 これは一般的に、マイクロプロセッサでの内部分解能よりもはるかに優れた分解能です。

もう1つ認識すべき点は、最大タイムアウトだけでは必ずしも有効であるとは限らないということです。 ほとんどのウォッチドッグスキームは基本的に、再トリガ可能、単安定マルチバイブレータ(再トリガ可能1ショット)機能を実装します。 ソフトウェアまたはハードウェアサイクルクロックが、最大許容可能タイムフレーム内でタイマをリセットしない場合、ウォッチドッグはプロセッサをトリップし、リセット(または障害回復サービスルーチンを開始)します。

また、最小時間要件は興味の対象となります。 たとえば、サービスルーチンが60Hzのパワーラインゼロクロスと同期されている場合、パルスは8.33ms離れている必要があります。 それらがすぐに到達している場合、ノイズまたはフォールト状態、多くの場合安全上の予期しない結果に対処する必要があります。

マルチプロセッサおよびマルチコア設計には、特別な状況があります。 個々のウォッチドッグは、各プロセッサ、またはその時そのプロセッサで実行しているコードのユニークな条件を持つコアをモニタするために、セットアップされる必要があります。 これは、マルチコア環境でコアを対象とするソフトウェア開発の一部は、それとともに、その特定のコードブロックの障害を示す特定のウォッチドッグ条件を含む必要があることを意味します。

加えて、ウォッチドッグレポートは階層的である必要があります。 各コアは、すべてのサブコアおよびプロセスからレポートされるすべての障害モードをひとまとめにする、より高レベルのウォッチドッグにレポートする必要があります。 上位システム機能として、ウォッチドッグエグゼクティブは、コードブロックを特定のコアに割り当てるメインタスクエグゼクティブとともに動作します。 それはまた、外部ウォッチドッグシステムと緊密に動作する必要があります。

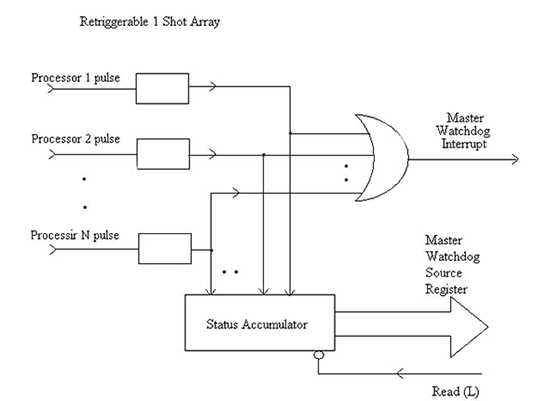

(図2)でレポートするコアに特有のI/Oを使用するために、ワイヤードORタイプのマルチウォッチドッグブロックを容易に拡張することができます。 それは、FPGAまたはCPLD内の独立した論理ブロックで、容易な拡張で複数のプロセッサおよびブロックを扱うことができます。 レジスタは、そのコアを個々に試し回復させるために、すべてのレポートブロックの独立した状態を蓄積することができます。 想像できるように、回復ルーチンは、残りのシステムを実行したままにしながらコアを再起動する方法と同様に、このレベルでより複雑になります。

図2:ウォッチドッグ階層のトップレベルは、すべてのマイクロプロセッサまたはコアが独自のレートでレポートできるために、拡張可能なワイヤードOR機能を使用することができます。 各1ショットにより、それがモニタしているプロセスが接続間隔でプログラムできる必要があります。 各コードブロックは、それとともに、ウォッチドッグパラメータを含む必要があります。

特別なウォッチドッグ機能を備えた部品

複数のマイクロプロセッサは、それらがウォッチドッグをいかにして実装するかに関しては、ユニークなまたはさまざまな機能を備えています。 たとえば、16ビットのMaxim MaxQシリーズについて考えてみましょう。この製品は、有用性を高めるために、柔軟性に富む各種の豊富なタイマをインテリジェントな回路と組み合わせています。 MaximのMAXQ2000-RBX+などの部品は、2次レベルのアラートを備えています。 サービスされない場合、そしてMAXQ2000のWDTがオーバーフローすると、それは、512回の付加的なシステムクロックサイクルの付加的なカウントを備えた割り込みをトリガします。 それから、ディスエーブルまたはオーバーライドされない場合に、それはすべてをリセットします。

その割り込みは、デバッギング情報を保存する「最後のチャンス」を提供します。このチャンスは、回路開発およびトラブルシューティング中に有用であるとほとんどの設計者が同意しているものです。 さらに、デバッギング情報を保存する代わりに、割り込みは、エラーから回復し、ウォッチドッグをクリアするのに使用できます。 しかし、後者のアプローチは、システム障害が存在している場合にシステムの信頼性を損なう可能性があります。

他の内部WDTと同様に、MAXQ2000のウォッチドッグは、ソフトウェアによってディスエーブルにすることができます。 しかし、この能力は諸刃の剣であることに注意してください。暴走コードは、ウォッチドッグをディスエーブルにし暴走し続ける可能性があります。

いくつかのマイクロプロセッサは、システムクロックと別個の内部発振器にWDTを接続します。 いくつかは内部または外部R/C発振器を使用し、いくつかは両方を使用することができます。 Maximが提供するMAXQ2000のWDTには興味深い機能が存在します。これは、WDTがシステムクロックからウォッチドッグタイミングを得ますが、メイン発振器に障害が発生すると、バックアップRC発振器に切り替わるという機能です。

ユニークなウォッチドッグ機能を持つもう1つの興味深いMCUとして、STMicroelectronicsが提供するSTM32F100ファミリ マイクロプロセッサがあります。この製品には、2つのウォッチドッグタイマがあります。 STM32F100CBT6Bなどの部品は、信頼できる必要があるスマートグリッドおよびスマートヘルスアプリケーションを対象としています。 ほとんどのマイクロプロセッサと同様に、それは複数のタイマを備えています。この場合は6つのタイマがあり、別の2つの16ビットタイマは、ウォッチドッグ機能専用です。

各ウォッチドッグには、DMAリクエストをトリガし、コンペアチャンネルをキャプチャできるウォッチドッグタイマのクロックに使用できる、選択可能なプリスケーラ(1~64K)があります。 それでも、もう1つの独立したウォッチドッグは、独立した40kHzの内部R/C発振器からクロックされる、112ビットのダウンカウンタおよび8ビットのプリスケーラをベースとしています。 非常に信頼できるバックアップ技術として、これらの部品がいかにしてR/Cコンポーネントに依存しているかにご留意ください。

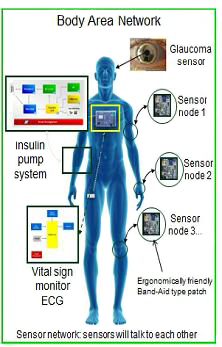

STMicroelectronicsが提供する部品の興味深い特長として、アナログウォッチドッグ機能があります。 A/Dからの1つ以上の変換された電圧レベルの高精度モニタリングは、プログラムされた閾値の外にアナログレベルがある場合、リセットをトリップすることができます。 これは、健康モニタリングまたはアクティブ薬剤分配向けにセンサがボディエリアネットワークに接続される医療用アプリケーションで有用である可能性があります(図3)。 設計支援として、STMicroelectronicsは、ヘルスケアおよびウェルネス設計向けのプロダクトトレーニングモジュールを技術者に提供しています。

図3:医療デバイスがよりアクティブにボディエリアネットワークと統合する中で、いくつかのデバイス(ペースメーカー、除細動器、インシュリンポンプなど)は、生命維持に極めて重要となる可能性があります。 信頼できるウォッチドッグを、これらのシステムに組み込む必要があります。

外部から内部を見る

複数の良好なビルディングブロック外部ソリューションには、シンプルなR/C閾値発生器、バイアストランジスタ、低電力タイマ、および専用パワーオンリセットおよびウォッチドッグコンパニオンプロセッサが含まれます。 加えて、実験や容易なテストを促す開発環境が利用可能です。Texas Instrumentsは、広い1.8~5VCCで30nAを消費するTPL5000ナノパワープログラム可能タイマで興味深いソリューションを提供しています。 TPL5000EVM評価キットにより、優れた小型の自己完結型モジュールでこの機能をテストし、最適化することができます。

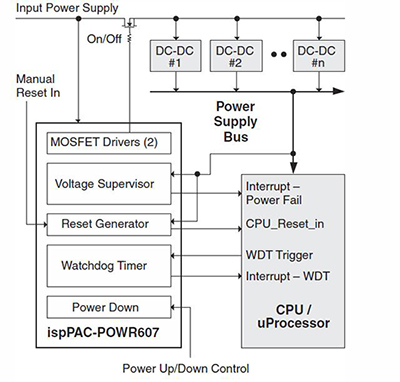

リアルタイムクロックおよび監視機能などの他の有用な機能を組み合わせた複数のディスクリートウォッチドッグが利用可能です。 興味深い組み合わせは、ISPPAC-POWR607-01SN32I電源スーパーバイザ、ウォッチドッグ、およびリセット発生器を持つLattice Semiconductorから提供されます(図4)。 ステートマシンおよび組み合わせのカスタマイズ向けの1パーセントアナログトリップポイントステップサイズ、およびインシステムプログラム可能マクロセルにご留意ください。

図4:インシステムユーザープログラム可能パラメータにより、組み合わせのおよびステートマシンベースのユーザー構成可能論理の使用を通したウォッチドッグ機能の動的決定が可能です。

結論

システムの復元に役立つものは何もない時があることを覚えておいてください。 いくつかの障害モードは、復元できません。 たとえば、システムメモリが破損している場合、信頼できるものは他に何もありません。

もう1つの例は、ノイズのレベルが非常に高い場合です。 ウォッチドッグがプロセッサをリセットしたとしても、ウォッチドッグステージのプロセッサの初期化にノイズが干渉する可能性があります。 ウォッチドッグ機能を初期化できない場合は、まるで全くウォッチドッグがないかのようです。

100パーセント完璧なMCU動作に常時頼ることは誰もできません。 マイクロプロセッサは誤動作する可能性があります。 しかし、内部および外部リソースのインテリジェントな利用により、軽度の障害、壊滅的な特性破損または人命の喪失において違いを生むことができます。

この記事で扱っている部品の詳細については、このページにあるリンクを使用して、DigiKeyウェブサイトの製品ページにアクセスしてください。

免責条項:このウェブサイト上で、さまざまな著者および/またはフォーラム参加者によって表明された意見、信念や視点は、DigiKeyの意見、信念および視点またはDigiKeyの公式な方針を必ずしも反映するものではありません。