位相ロックループ周波数シンセサイザの基礎

DigiKeyの北米担当編集者の提供

2021-02-03

高速シリアル通信バスにおけるデータレートの上昇に伴い、より高い周波数、より優れた安定性、より高い周波数分解能、より高い信号純度を持つシステムクロックが必要とされています。ダイレクトデジタルシンセサイザはこれらの特性を備えていますが、使用できる周波数は2または3ギガヘルツ(GHz)以下のみです。数十ギガヘルツまでの周波数に対応したソリューションが必要なのです。

まず、このソリューションには、最大30GHzのクロック周波数を生成するPLL(位相ロックループ)ベースのアナログ周波数シンセサイザが使用されます。また、基準周波数に整数値を乗算する整数Nシンセサイザと、基準周波数に非整数の分数値を乗算する分数Nシンセサイザには、位相ノイズや類似する不純な信号を最小化する特殊な技術を採用しています。

この記事では、Analog Devicesのデバイスを例に用いて、整数Nと分数Nの周波数シンセサイザの設計について説明します。また、この記事では、これらのデバイスを高速シリアルデータリンクや周波数アジャイルレーダに使用することを可能にする技術革新にも注目します。

整数N位相ロックループシンセサイザ

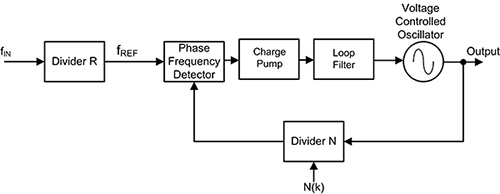

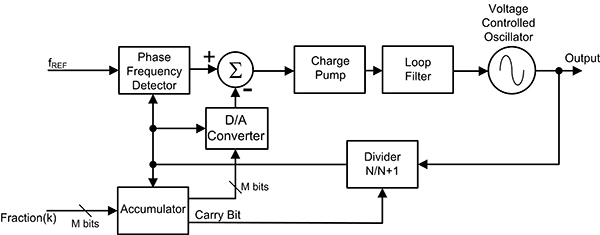

PLL回路は、周波数と位相の制御に使います。それらは、クロックソース、周波数逓倍器や復調器、トラッキングジェネレータ、クロック回復回路として構成することができます。これらの各アプリケーションで必要な特性はそれぞれ異なりますが、いずれも同じ基本的な回路の概念を用いています。図1は、周波数逓倍器として構成された基本的なPLLのブロック図を示したものです。

図1:古典的な整数N位相ロックループ周波数シンセサイザのブロック図。(画像提供:DigiKey)

図1:古典的な整数N位相ロックループ周波数シンセサイザのブロック図。(画像提供:DigiKey)

この回路の動作は、すべての位相ロックループで典型的なものです。基本的には、電圧制御発振器(VCO)の位相を制御するフィードバック制御システムです。入力信号は、入力周波数を係数Rで分周するプリスケーリング分周器に印加され、プリスケーリング分周器の出力は、位相周波数検出器(PFD)の1つの入力を形成する基準周波数となります。

もう1つのPFD入力は、N分周カウンタの出力からのフィードバック信号です。通常、PLLがロックされている場合、これら2つの信号の周波数はほぼ同じです。位相検出器の出力は、これら2つの入力の位相差に比例した電圧です。起動時のようにループがアンロックされている場合や、入力の周波数に瞬間的に大きなシフトがある場合は、位相周波数検出器が動作してPLLの動作周波数を希望の設定に変更します。その周波数に到達すると、PFDは位相検出モードに戻り、基準周波数とフィードバック信号の位相差に比例した出力になります。

位相周波数検出器は、バイポーラスイッチング電流源であるチャージポンプを駆動します。つまり、PLLのループフィルタに正負の電流パルスを出力することができるのです。

ループフィルタは位相誤差信号を平滑化するとともに、PLLのダイナミック特性を決定します。このフィルタ処理された信号が、VCOを制御します。VCO出力の周波数は、位相周波数検出器への周波数リファレンス入力に供給された入力のN倍であり、周波数入力のN/R倍であることに注意してください。この出力信号は、N分周カウンタを介して位相検出器に戻されます。

通常、ループフィルタはそのPLLの用途に必要な特性に一致するように設計されます。PLLが信号を受け入れてトラッキングする場合、ループフィルタの帯域幅は、固定入力周波数を想定している場合より大きくなります。PLLが引き込んでロックオンする周波数範囲は、「キャプチャレンジ」と呼ばれます。PLLがロックされ信号をトラッキングしているときにPLLが追従する周波数の範囲は、「トラッキングレンジ」と呼ばれます。一般に、トラッキングレンジはキャプチャレンジよりも広くなります。信号周波数がどれだけ速く変化できるか、またその場合にもロックを維持できるか、つまり最大スルーレートも、PLLのループフィルタで決まります。ループフィルタの帯域幅が狭いほど、位相誤差は小さくできます。これは、応答を遅くすることとキャプチャ範囲を狭めることの引き換えで得られます。クロックアプリケーションで使われるPLLは、主に固定周波数で動作します。一般的に、ループフィルタの帯域幅は、基準周波数よりもはるかに小さいことが望ましいです。

PLLの出力周波数は基準周波数の整数倍であるため、その周波数分解能は基準周波数と等しくなります。より精細な周波数分解能を得るためには、プリスケールカウンタRで基準周波数を減少させる必要があります。

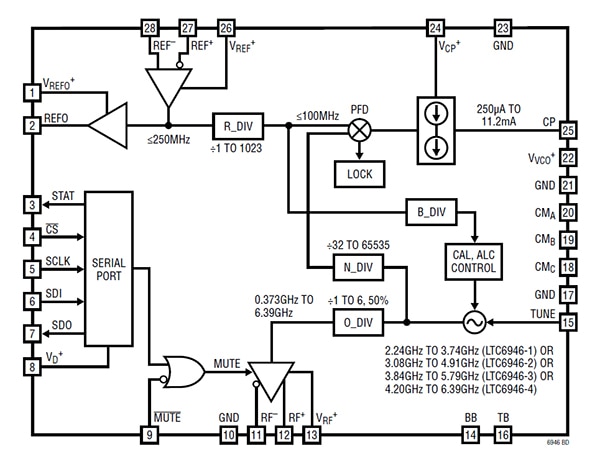

整数N周波数シンセサイザの市販例としては、Analog DevicesのLTC6946IUFD-3#PBFがあり、これはVCOを内蔵し、優れたスプリアス性能を備えた0.64~5.790GHzの低ノイズシンセサイザです(図2)。4種類のシンセサイザICのファミリに属しており、それぞれの周波数範囲が異なるため、合計で0.373~6.390GHzの範囲をカバーします。

図2:Analog DevicesのLTC6946IUFD-3#PBF整数N周波数シンセサイザおよび統合されたVCOのブロック図。(画像提供:Analog Devices)

図2:Analog DevicesのLTC6946IUFD-3#PBF整数N周波数シンセサイザおよび統合されたVCOのブロック図。(画像提供:Analog Devices)

このシンセサイザでは、特定の用途に合わせて最適化できるループフィルタをユーザーが外部から供給する必要があります。プリスケールカウンタの分周器が内蔵されており、分周範囲は1~1023までとなっています。ループ分周器は、32から65535までの範囲を備えています。チャージポンプ電流は、ループフィルタの要件に合わせて250μAから11.2mAまで調節可能です。

分数N位相ロックループシンセサイザ

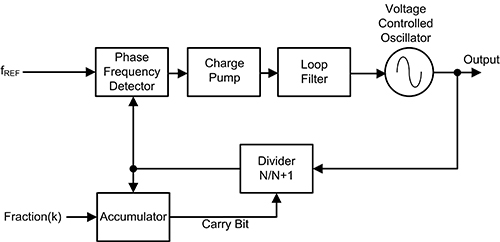

PLLシンセサイザの周波数分解能は、ステップサイズを整数値以下にすること、すなわち、ループ分周器(N)のステップを分数にすることで向上させることができます。これは、カウントダウン値を動的に変化させたり、「ディザリング」させたりすることで実現します。つまり、分周器の設定はPLL出力周波数の一定サイクルの間で値Nを保持し、N+1のように異なる値に周期的に変更されます。例えば、3回の基準周期について分周器の設定を4、4回目の基準周期を5とした場合、有効なカウントダウンは4.25となります。これを実現する方法の1つは、図3に示すようにアキュムレータを使用することです。

図3:分周器のカウントを変調するためにアキュムレータを使用する分数N PLLシンセサイザのブロック図。(画像提供:DigiKey)

図3:分周器のカウントを変調するためにアキュムレータを使用する分数N PLLシンセサイザのブロック図。(画像提供:DigiKey)

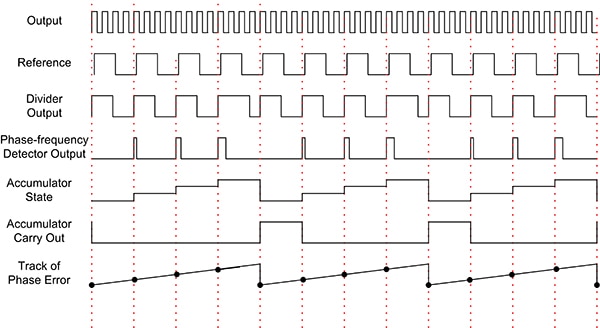

アキュムレータは、分周器からの出力パルスをカウントし、M(アキュムレータのモジュラス)ごとに、分周器の入力を変化させるキャリービットを出力します。図4は、フラクショナル分周器の設定値を4.25に設定した例を継続して示しています。

図4:アキュムレータを用いた分数Nシンセサイザのタイミング図。(画像提供:DigiKey)

図4:アキュムレータを用いた分数Nシンセサイザのタイミング図。(画像提供:DigiKey)

アキュムレータは分割出力で駆動され、モジュロ4(Mは4に等しい)をカウントします。4つ目のパルスごとにキャリー出力を生成し、分周器のカウントを1つ増加させます。アキュムレータがリセットされ、再びカウントを開始します。分周器の設定が大きくなると出力周波数がシフトし、位相オフセットの累積誤差が発生します。位相誤差の軌跡は、時間関数としてのパルス値を示しています。

平均的な分周器の設定は4.25ですが、シンセサイザの出力は位相変調されているため、出力にスプリアストーンが発生します。アキュムレータの状態を見ると、位相誤差を追跡していることは明らかです。これにより、図5に示すように変調を除去することができます。

図5:分数Nのディザリングによる位相変調を打ち消すために、D/A変換されたアキュムレータの状態を使用。(画像提供:DigiKey)

図5:分数Nのディザリングによる位相変調を打ち消すために、D/A変換されたアキュムレータの状態を使用。(画像提供:DigiKey)

アキュムレータの状態は、デジタル/アナログ(D/A)コンバータでアナログに変換され、位相周波数検出器の出力からスケーリングして減算することで、分数Nのディザリングによる位相変調を打ち消すことができます。補正信号が位相誤差と正確に一致しないと、出力にスプリアストーンが発生するため、細心の注意が必要です。

シグマデルタ変調器の挿入

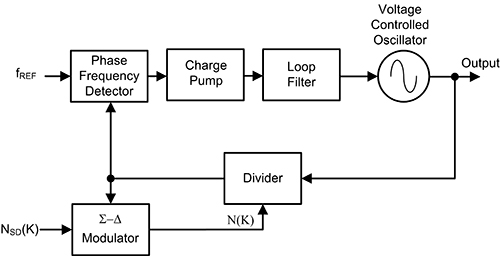

アキュムレータの周期性は、シンセサイザからのスプリアス出力の原因となります。アキュムレータをシグマデルタ変調器に置き換えれば、デジタル手法を適用して、スプリアス応答とノイズを最小化する方法で分周器のカウントを変調することができます。この置き換えを図6に示します。

図6:アキュムレータをシグマデルタ変調器に置き換えることで、スプリアス応答を低減するために分周器のカウントを変化させるデジタル手法を適用することができます。(画像提供:DigiKey)

図6:アキュムレータをシグマデルタ変調器に置き換えることで、スプリアス応答を低減するために分周器のカウントを変化させるデジタル手法を適用することができます。(画像提供:DigiKey)

シグマデルタ変調トポロジで採用されている一般的なデジタル手法は、実際には2つあります。1つ目は、平均分周係数が希望のフラクショナル分周器の値を生成するように、より広い範囲の値にわたってN分周器のカウント数を増加させる手法です。これにより、1次フラクショナルスプリアスが減少します。アキュムレータベースのシンセサイザは、2つの状態の間でカウントを変化させます。これは、1次変調方式です。n次のシグマデルタ分数PLLは、2n個の異なる値の間でN個のカウンタを変調します。例えば、3次変調器は8つの異なる分周値の間で交互に動作し、4次変調器は16の異なる分周値の間で交互に動作します。

ディザリングとも呼ばれる2つ目のデジタル手法は、擬似乱数になるように2N配列を乱数化することを目的としています。平均フラクショナル分周比を維持しながら、フラクショナルスプリアスをPLLでフィルタリングできるような形でランダムノイズに変換します。

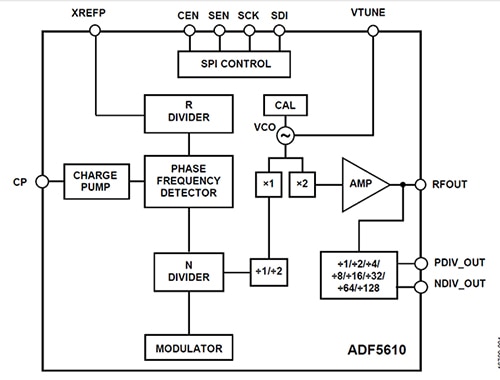

シグマデルタ分数Nシンセサイザの市販バージョンは、Analog DevicesのADF5610BCCZ であり、これはVCOを内蔵した低ノイズで0.57MHz~14.6GHzの分数Nシンセサイザです(図 7)。

図7:Analog DevicesのADF5610BCCZ のブロック図。分数Nまたは整数シンセサイザ構成の両方をサポートします。(画像提供:Analog Devices)

図7:Analog DevicesのADF5610BCCZ のブロック図。分数Nまたは整数シンセサイザ構成の両方をサポートします。(画像提供:Analog Devices)

ADF5610には、外部リファレンス発振器とループフィルタが必要です。基本周波数が3650MHz~7300MHzのVCOを内蔵しています。これらの周波数は内部で2倍になり、RFOUTピンに送られます。2倍のVCO周波数を1、2、4、8、16、32、64、または128で分周することができ、最小57MHzのRF出力周波数の生成を可能にする差動出力があります。

ADF5610は24ビットの分数モジュラスを備えた先進のシグマデルタ変調器を採用しており、非常に低いスプリアスレベルを実現しています。シグマデルタ変調器を使用するすべてのシンセサイザと同様に、このデバイスではデジタル信号処理技術を使用して、希望の平均フラクショナル分周比を見つけ出します。このプロセスでは、PFDレートでクロックされ、ハイパス周波数特性を持つ量子化ノイズと呼ばれる出力変調ノイズが生成されます。外部ローパスループフィルタは、この量子化ノイズをVCOの位相ノイズよりも下のレベルまでフィルタリングし、ノイズがシステム全体の位相ノイズの一因になることを防止するために使用されます。

ADF5610には、0Hzの周波数誤差を実現するための正確な周波数モードも搭載されています。このモードでは、完全な24ビット位相アキュムレータのモジュラスを使用しながら、隣接する整数Nの境界ステップ間で正確な周波数を生成することができます。高い位相検出器比較レートで正確な周波数ステップを実現し、このモードではPLLが優れた位相ノイズとスプリアス性能を維持できるようにします。

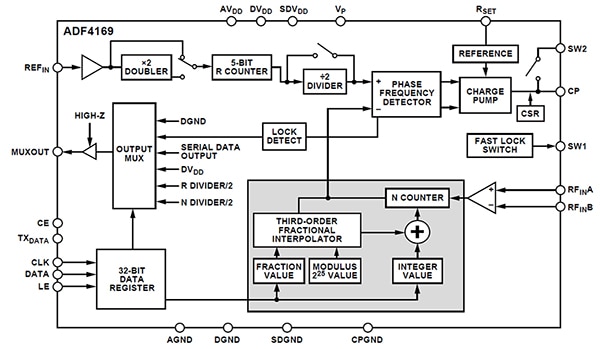

Analog DevicesのADF4169CCPZ-RL7は、整数Nまたは分数Nのデバイスとして構成可能なもう1つのPLLシンセサイザです。変調と波形生成を行い、最大13.5GHzのRF帯域幅で動作します。外部リファレンス周波数入力、VCO、ループフィルタを使用しています。分数N合成用の3次シグマデルタ変調器を備えており、これを無効にすることで、デバイスを整数Nモードで動作させることができます(図8)。

図8:Analog DevicesのADF4169CCPZ-RL7には、3次シグマデルタ変調器を使用しています。(画像提供:Analog Devices)

図8:Analog DevicesのADF4169CCPZ-RL7には、3次シグマデルタ変調器を使用しています。(画像提供:Analog Devices)

ADF4158WCCPZ-RL7シンセサイザは、周波数変調連続波(FMCW)レーダに使用することを意図しています。のこぎり波や三角/ランプ波など、周波数領域において様々なタイプの変調波形に対応しています。これは、レーダ用途で必要な特別な機能です。

結論

高速シリアル通信バスのデータレート上昇に伴い、設計者は、3GHz以下で最適に動作するダイレクトデジタルシンセサイザを超えたシステムクロックソリューションに目を向ける必要があります。整数Nおよび分数Nのトポロジを使用したPLLベースの周波数シンセサイザは、数十ギガヘルツまでの周波数の高周波クロック、シリアルデータ通信、レーダアプリケーション向けに安定した低ノイズ信号を提供します。

免責条項:このウェブサイト上で、さまざまな著者および/またはフォーラム参加者によって表明された意見、信念や視点は、DigiKeyの意見、信念および視点またはDigiKeyの公式な方針を必ずしも反映するものではありません。