Taking the RISC Out of CISC

Electronic Products の提供

2014-03-05

There has been a blurring between the definitions of RISC (reduced instruction set computing) and CISC (complex instruction set computing) architectures to the point where in many cases the terms are almost meaningless. Many modern RISC processors are far more complex than some CISC processors. In fact, it is no longer the number of instructions that define the differences between RISC and CISC, but rather the way they perform memory accesses.

Even though examples of RISC-style architectures can be found in the 1960s and 1970s, the real history of RISC goes back to the 1980s. The idea behind it was that having a more simplified set of instructions meant that those instructions could be performed faster if the architecture was not burdened by instructions that were rarely, if ever, performed.

The two initial RISC architectures were MIPS and Power Architecture, developed, respectively, at Stanford University and the University of California at Berkeley. A key aspect was that RISC systems used a load-store architecture. Here memory is normally accessed through specific instructions, rather than accessed as part of other instructions. Today, when RISC systems have become more complex than some CISC architectures, that memory access system is seen as more of a defining factor when distinguishing between RISC and CISC. Early examples of the two initial architectures were the Hewlett-Packard PA-RISC and Sun Microsystems’ Sparc processor.

CISC products, on the other hand, are typified by the x86 architectures, mainly from Intel but also from others such as AMD. Intel’s Pentium range is one of the best examples of CISC chips, Motorola’s 68000 series is another. However, CISC chips, despite the name, do not always use a complex architecture and these days many are less complex than RISC chips. Basically anything that does not use the load-store memory access system is often classed as CISC, whatever the architecture looks like. There is no doubt that a floating-point RISC architecture is much more complex than, say, an 8-bit CISC processor. Even the addressing modes on RISC chips are often more complex than with many CISC processors. Good examples of modern RISC processors are Microchip’s PIC® range and the devices from many manufactures that are based on ARM™ cores.

PIC chips

PIC, or peripheral (sometimes referred to as programmable) interface controller, has its origins in the 1970s, with the first 8-bit PIC developed in 1975 to offload I/O from the General Instruments CP1600 16-bit CPU. It was only later, as RISC became more widely known, that the PIC design was classified as part of the RISC family.

In 1987, General Instruments spun off its microcontroller business to create what became known as Microchip Technology, which also declared that the acronym PIC now stood for programmable intelligent computer.

ARM cores

Among the most popular RISC designs today are those based on ARM cores. These date back to Acorn Computers in the 1980s, which designed the architecture to power its desktop computers. The technology was later spun off into its own company – ARM Holdings. Like PIC, ARM has seen its acronym rewritten from initially standing for Acorn RISC Machine to today’s Advanced RISC Machine.

ARM’s success has been due to the proliferation of mobile devices and its cores can be found in almost all mobile phones as well as tablets and PDAs. The architecture itself typifies modern RISC devices in that it is complex but still classified as RISC because it uses the load-store memory access method.

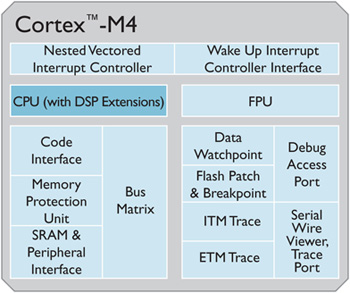

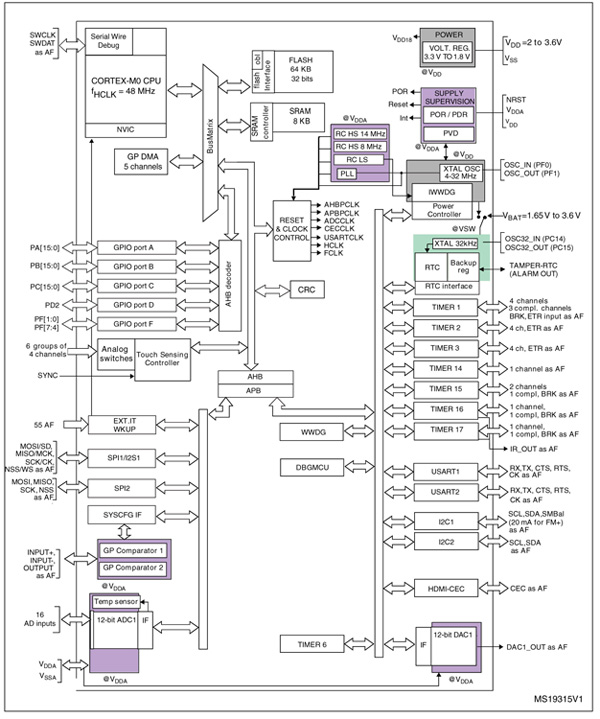

Typical of the ARM products is the Cortex®-M series, which consists of are extremely powerful RISC chips. The Cortex-M0, as used in the STM32F051K8U6 from STMicrolectronics, provides 32-bit performance yet has a smaller code size than many 8-bit devices. The reduced memory requirements allow it to make full use of the on-chip flash memory. Like all the processors in the Cortex-M range, its base of 16-bit instructions can be extended to include 32-bit instructions. The Cortex-M0 is also upwards compatible with even more powerful Cortex-M3 and Cortex-M4 processors, the latter of which can be found for example in the TM4C123BE6PZI from Texas Instruments. This brings complex digital signal processing techniques to the low-power 32-bit market.

Examples and applications

As mentioned, a good example of a RISC chip is the STM32F051K8U6 from STMicrolectronics. This uses an ARM Cortex-M0 32-bit RISC core operating at 48 MHz. The Cortex-M0 was developed to provide a low-cost platform that meets the needs of MCU implementations, with reduced pin count and low power consumption, while still delivering the necessary computational performance and an advanced system response to interrupts. Though a 32-bit RISC processor, it has the performance one would expect but with a memory size usually associated with 8- and 16-bit devices.

A typical application would be a smartcard interface using the STM32F05xx USART peripheral. This application is based on STMicroelectronics’ STM320518-EVAL evaluation board with some additional hardware.

The smartcard interface was developed using the USART smartcard mode, which supports asynchronous protocol smartcards, as defined in ISO 7816-3 (Class A).

With the smartcard mode enabled, the USART must be configured as either 8 data bits plus parity, 0.5, or 1.5 stop bits. A 5-bit prescaler and the smartcard clock generator provided the clock to the smartcard. GPIO pins were used to provide the rest of the functions required to interface to the smartcard.

The STM32F0xx microcontrollers also have a high-definition multimedia interface consumer electronics control (HDMI-CEC) controller that supports the HDMI-CEC v1.4 protocol. The HDMI-CEC controller provides hardware support for this protocol, and it supports the whole set of features offered with CEC devices. Therefore, another application can implement the CEC protocol software and hardware based on the HDMI-CEC controller.

The CEC bus is a single-wire protocol that can connect up to ten audiovisual devices through standard HDMI cabling. All transactions on the CEC line consist of an initiator and one or more followers. The initiator is responsible for sending the message structure and the data. The follower is the recipient of any data and is responsible for setting any acknowledgement bits. A message is conveyed in a single frame that consists of a start bit followed by a header block and, optionally, an opcode and a variable number of operand blocks.

The STM32F0xx HDMI-CEC controller provides hardware support for the CEC protocol and, thus, an easy platform on which to build CEC firmware applications. However, to be fully compliant with the HDMI 1.4 specification, especially when the CEC device is in the power-off state, a fully-integrated ESD protection should be added externally to the STM32F0xx.

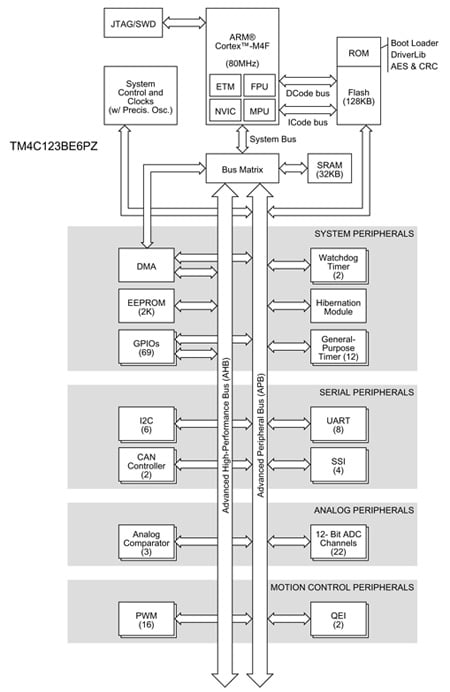

Also using a 32-bit ARM core, but this time the Cortex-M4 89 MHz processor, is the TM4C123BE6PZI from Texas Instruments. This microcontroller is for industrial applications, including remote monitoring, electronic point-of-sale machines, test and measurement equipment, network appliances and switches, factory automation, HVAC and building control, gaming equipment, motion control, transportation, and fire and security.

Core features include system timer (SysTick), integrated nested vectored interrupt controller (NVIC), wake-op interrupt controller (WIC) with clock gating, memory protection unit (MPU), IEEE754-compliant single-precision floating-point unit (FPU), embedded trace macro and port, and system control block (SCB).

It is possible to migrate working designs from Stellaris® LM3S microcontrollers (which used the Cortex-M3 architecture) to these microcontrollers. Software migration is straightforward when using the driver library APIs in the StellarisWare® and TivaWare™ for C series software. Both families are based on the Cortex-M core, and the peripherals are generally very similar, and in some cases identical.

The MCUs have a high level of connectivity and sensor aggregation, which make them suitable for connected applications, such as home, building, and industrial automation. The Cortex-M4 core expands the instruction set of the Cortex-M3 by adding DSP extensions and single instruction, multiple data (SIMD) instructions. The DSP operations include single-cycle 32-bit or dual 16-bit multiply-accumulate (MAC) instructions and saturating arithmetic instructions. Optimized SIMD instructions can perform four 8-bit or two 16-bit arithmetic operations in a single cycle and are therefore effective at performing arithmetic operations on large arrays of data.

Besides providing a performance boost for math-intensive operations, floating-point support simplifies the implementation and programming of floating-point routines. An engineer can spend a week developing a digital filter in Matlab and a month converting the filter to a fixed-point implementation to ensure it is precise and stable. This time is not required when programmers can program their filters in the native floating-point format.

The integrated high-resolution 12-bit ADC can sample as fast as 1 MSPS, a sample rate that supports both the full resolution and accuracy of the ADCs. This means the quality of the readings does not have to be degraded to achieve higher sample rates. Two of these converters are on-chip and can be fed from twenty-four independent inputs.

To improve precision, a differential external reference voltage can be applied to dedicated inputs. The ADCs can generate processor interrupts that are based on a conversion completion and a match to one of eight digital comparators. Readings from the ADCs can be queued, compared and averaged within the ADC.

The on-chip direct memory access controller can feed ADC readings from the ADC FIFOs to RAM or another peripheral without waking up or distracting the ARM core. There are also three on-chip analog comparators that can be used with a programmable internal voltage reference to detect when an input analog signal has crossed a specific threshold. These comparators, along with the digital comparators, remove the requirement of polling incoming ADC values continuously, freeing up the CPU to focus on real-time applications.

One application that can take advantage of the ADCs’ fast, accurate floating-point performance is motion control for running algorithms that are more sophisticated and on-chip comparators. The more quickly and precisely the motor driver can track the dynamics of a motor during operation, the less pushback resistance the generated PWMs will encounter and the control signals will be more efficient. This uses less energy and the shaft will spin smoother and maintain speed or accelerate at varying loads. The on-chip comparators can be used to check for fault conditions in the system, which require immediate response.

PIC range

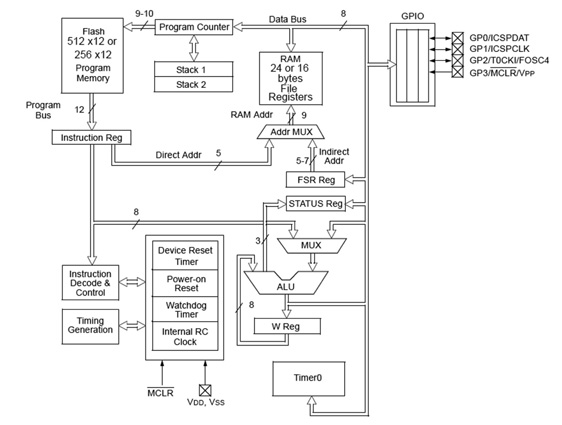

Even though ARM has become a major player in RISC architectures, it is not the only company. In fact, more traditional RISC products can be found in the PIC range from Microchip, the PIC10F200T-I/OT being a good example. This is a low-cost, high-performance, 8-bit, static, flash-based CMOS microcontroller. The RISC architecture has only thirty-three single-word or single-cycle instructions. All instructions are single cycle (1 µs) except for program branches, which take two cycles. The easy-to-use and easy-to-remember instruction set is said to reduce development time significantly.

The PIC10F20x devices include features to reduce system cost and power requirements. The power-on reset (PoR) and device reset timer (DRT) eliminate the need for external reset circuitry. Additionally, the internal oscillator mode preserves the limited number of I/O available. Other features include power-saving sleep mode, watchdog timer, and code protection.

Applications range from personal-care appliances and security systems to low-power remote transmitters and receivers. The flash technology makes customizing application programs, such as transmitter codes, appliance settings, and receiver frequencies, fast and convenient. The small footprint, for through-hole or surface mounting, makes them suitable for applications with space limitations. They can even be used where no microcontroller has previously been considered, for example timer functions, logic, and PLDs in larger systems and coprocessor applications.

They also have an onboard comparator that can be used for capacitive sensing in touch-control applications. This is done by using the comparator as a relaxation oscillator where the output is used to charge and discharge the sensing capacitor, which is formed by a pad on the circuit board. The charge rate can be determined by the RC time constant, which can be created by an external resistor and the capacitance of the pad.

Introducing extra capacitance when a person’s finger touches the key, creating a route to ground, causes the frequency to change. This change can be measured by the PIC MCU to detect a finger press.

Another application can be found in the kitchen where adjustable mechanical thermostats are often used to vary the heat output of electric ranges, skillets, and fryers. These thermostats tend to be expensive and problematic. They have to be calibrated at the factory, they have poor simmer performance because control is not precise enough at low temperatures, their accuracy is generally poor and, being mechanical, they wear out.

The PIC MCU can be used as the heart of a lower-cost microcontroller-based replacement. The PIC can take inputs from a potentiometer and control current to the heating element via a triac. Therefore, because this application uses a triac, it can be adapted for other applications that interface to AC lines, such as light switches, vacuum cleaners, and various household appliances. Power to the PIC is supplied directly from the AC lines via a resistive power supply.

A useful characteristic of the triac is that it is triggered by current rather than voltage in that the amount of current injected at the gate, not the magnitude of voltage applied to the gate, determines whether the triac is turned on. This makes triacs useful in the digital realm where voltages are significantly less than 115 or 220 VAC. PIC microcontrollers operate in the 2.5 to 5 V range, yet can sink and source 25 mA on their I/O pins. During any half-cycle of the AC waveform, a negative current pulse of sufficient width and magnitude will trigger the triac, which will conduct current until the half-cycle is completed, then revert to the non-conductive or blocking state.

This kind of phase control is common in light dimmers. An alternative is zero cross switching, which eliminates most EMI problems because an entire cycle is either on or off. To vary the average current sent to the load, alternating cycles can be skipped. This is not suitable for light dimmers because the intensity of the light will noticeably fluctuate. However, this method is better for a resistive heating element because EMI is lower. In this application, the zero cross is detected by tying a pin of the microcontroller directly to the anode of a Zener diode. Compared with the mechanical thermostat, this application provides design flexibility, including extra features such as a status LED indicating whether the range is on or off and an automatic shutdown that turns the range off after two hours if left unattended.

RISC versus CISC in the future

The mobile device arena is becoming the battleground now for RISC and CISC, typified by the two big players of ARM and Intel. ARM has taken control of the smartphone and tablet market because the powerful chips made by its licensees are also very low power. Intel has tried to battle back by moving into the low-power arena, notably with its Atom range, but is still making few inroads into ARM territory. On the other side, the quest for lower power in more powerful computers has led some to consider ARM devices, whereas in the past the x86 range was the only place they would look. Intel, though, has a lot of clout and is fighting back.

The whole growth of connected devices, the so-called Internet of Things, is seeing intelligence in smaller and smaller devices where power consumption is key. Here, the likes of Microchip’s PIC architecture are already doing well. With ARM’s RISC cores in the more intelligent devices, there seems little room for x86 in this fast-growing segment. In the larger computer market, ARM will struggle to displace the x86 dominance, but will try. There are interesting times ahead.

免責条項:このウェブサイト上で、さまざまな著者および/またはフォーラム参加者によって表明された意見、信念や視点は、DigiKeyの意見、信念および視点またはDigiKeyの公式な方針を必ずしも反映するものではありません。