モジュール式小型DC/DCコンバータを使って電源レールノイズを最小限に抑える方法

DigiKeyの北米担当編集者の提供

2021-06-23

ノイズは、ほぼすべてのシステム設計につきもので、通常は必ず検討事項となります。外部にあるノイズ源は回路設計者が直接制御することはできませんが、回路自体がノイズ源になる場合もあります。多くの場合、設計者がノイズ源、特に電源レールのノイズを最小限に抑える必要があります。電源レールのノイズが、高感度のアナログ&デジタル回路に影響する可能性があるためです。

その結果、回路の性能が不安定になり、分解能や精度が低下します。最悪を免れたとしても、ビットエラーレート(BER)が高くなる程度までの状態にはなります。最悪の場合は、システム全体の誤動作や、性能上の問題を頻繁に、または断続的に起こす可能性があります。いずれもデバッグは困難です。

スイッチングDC/DCレギュレータとその出力レールには、リップルノイズと放射ノイズという2つの大きなノイズ問題があります。回路内で発生するノイズは、電磁両立性(EMC)規制の対象となり、様々な周波数帯で規定レベル未満であることが求められます。

設計者にとっての課題は、内部から発生するノイズとその発生源を識別し、「ノイズを出さないように設計する」か、あるいは設計後にノイズを軽減することです。この記事では、Monolithic Power Systems, Inc.のDC/DCレギュレータを使用してレギュレータのノイズ問題を最小限に抑える際に取れる選択肢について説明します。

ノイズの発生源とタイプ

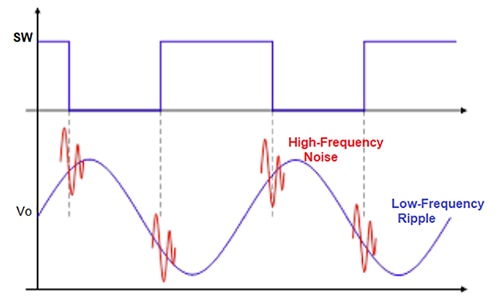

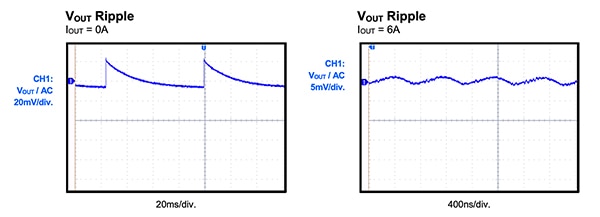

最も観察しやすいと同時に回路性能に直接影響を与えるノイズは、スイッチング周波数のリップルです。このリップルは通常、約10〜20ミリボルト(mV)です(図1)。リップルは、ランダムではありませんが、システムの性能に影響を与えるノイズの一種です。このようなミリボルトレベルのリップルは、5ボルト以上のレールで動作する高電圧のデジタルICでは通常問題になりませんが、3ボルト未満で動作する低電圧のデジタル回路では問題になることがあります。また、電源レール上のリップルは、精密なアナログ回路/コンポーネントで大きな問題となります。そのため、このようなデバイスの電源電圧変動除去比(PSRR)の仕様は非常に重要となります。

図1:レギュレータのスイッチング動作によるDCレールのリップルは、回路の基本性能や結果の精度に影響を与えます。(画像提供:Monolithic Power Systems, Inc.)

図1:レギュレータのスイッチング動作によるDCレールのリップルは、回路の基本性能や結果の精度に影響を与えます。(画像提供:Monolithic Power Systems, Inc.)

さらに、DC/DCレギュレータのスイッチング動作は、無線周波数(RF)ノイズを放射する可能性もあります。DCレール上のリップルのミリボルト数が許容できるものであった場合でも、EMCを損なう電磁放射の問題もあります。このノイズは、スイッチングコンバータに応じて数キロヘルツから数メガヘルツ(MHz)の間の既知の基本周波数を持ち、また多くの高調波を持っています。

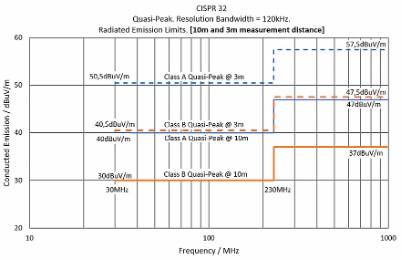

EMC関連の規制規格で最もよく引用されるのは、CISPR 22とCISPR 32の「情報技術機器 - 無線妨害特性 - 測定の方法および限界値」です(CISPRは「国際無線障害特別委員会」の略)。また、欧州規格「EN 55022」は、主に製品規格「CISPR 22」から派生したもので、厳密に定義された条件の下で検査が行われます。

CISPR 22は、欧州共同体のほとんどの加盟国で採用されています。米国のFCC Part 15とCISPR 22は比較的調和がとれるように調整されてきていますが、いくつかの違いがあります。CISPR 22/EN 55022はCISPR 32/EN 55032に「吸収」されました。CISPR 32/EN 55032は、マルチメディア機器(MME)の新しい製品ファミリ規格であり、EMC指令に準拠した整合規格として有効です。

主に住宅環境での使用を目的とした機器はクラスBの制限を満たす必要があるのに対し、その他の機器はクラスAに準拠する必要があります(図2)。北米市場向けに設計された製品は、米国連邦通信委員会(FCC)パート15、サブパートBの15.109項で定められた、意図しない放射に対する制限に準拠する必要があります。したがって、DCレギュレータから放射される電気ノイズが製品自体に悪影響を及ぼさない場合でも、様々な規制上の規定を満たすにはそのノイズが高すぎて許容できないことがあります。

図2:これはCISPR 32/EN 55032に記載されている数多くのグラフの1つで、様々なクラスの民生品の周波数に対する放射限界を規定しています。(画像提供:Academy of EMC、「EMC Standards」)

図2:これはCISPR 32/EN 55032に記載されている数多くのグラフの1つで、様々なクラスの民生品の周波数に対する放射限界を規定しています。(画像提供:Academy of EMC、「EMC Standards」)

EMC問題への対処は複雑なテーマであり、単純な解決策はありません。これらの放射の測定値と許容限界が回路の動作周波数、距離、電力レベル、アプリケーションクラスの関数であることに注意してください。このような理由から、多くのテクニカルリソースを確認したり、専門知識の提供や指導を行ってくれるコンサルタントに相談することは意味のあることです。

とは言え、回路性能の問題を回避し、かつ該当するノイズ規定を満たすため、設計者には、ノイズを最小限に抑えるための以下の3つの基本戦略があります。

- 低ドロップアウトレギュレータ(LDO)を使用する。

- スイッチングレギュレータに外付けフィルタを追加して、DCレール上の負荷から発生するノイズを低減する。

- スイッチングレギュレータモジュールは、インダクタやコンデンサなど、レギュレータICの外付け部品を内蔵したものを選定する。選定したモジュールは、低ノイズレールを実装するように設計・保証されているため、外付けフィルタは最小限またはゼロで済みます。

LDOについての説明

LDOには、アーキテクチャとしてクロックやスイッチングがないため、EMCノイズが元々少なく、出力レールのリップルがないという特徴があります。このため、年間数億個のLDOが使用されています。LDOを適する設計に適用すれば、効果的なソリューションとなります。

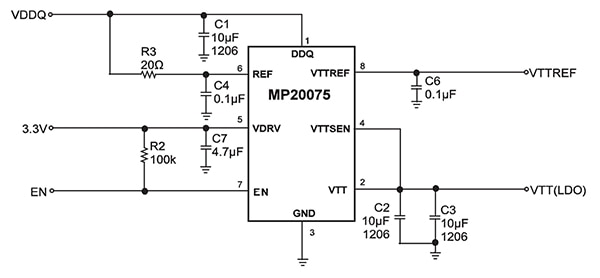

たとえば、Monolithic Power SystemsのMP20075 LDOは、ダブルデータレート(DDR)2/3/3L/4同期型DRAM(SDRAM)のアクティブバス終端に特化して製造されています(図3)。このLDOは、8ピンMSOPハウジングに収納されており、1.05~3.6ボルトの間でユーザー設定可能な電圧で最大3アンペア(A)のシンクおよびソースが可能であり、正確な終端のための精密なVREF/2トラッキング電圧を備えています。

図3:MP20075 LDOは、最大3Aのシンクまたはソースが可能で、様々なクラスのDDR SRAMの終端ニーズ用に最適化されています。(画像提供:Monolithic Power Systems)

図3:MP20075 LDOは、最大3Aのシンクまたはソースが可能で、様々なクラスのDDR SRAMの終端ニーズ用に最適化されています。(画像提供:Monolithic Power Systems)

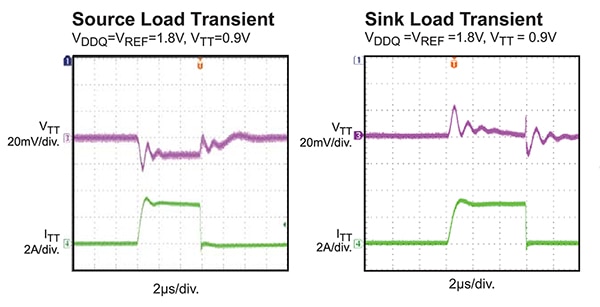

MP20075の内蔵分圧器は、基準電圧(REF)を追跡し、VTTとVTTREFの出力電圧を正確に保ちます。また、同分圧器は、ケルビンセンシングにより、VTTで±30mV、VTTREFで±18mVの精度を実現しています。さらに、一般的なLDOと同様に、アナログのみの閉ループトポロジを採用しているため、出力負荷の過渡現象に対してわずか約数マイクロ秒という非常に高速の応答を実現しています(図4)。このような過渡応答は、このLDOの設計対象となったDDR SRAMの終端部のような高速回路ではしばしば重要です。

図4:LDOのアナログ閉ループ設計により、負荷による過渡的な要求に対し、非常に高速な応答が可能になっています。このような高性能は、DDR SRAMの終端処理などのアプリケーションに必要なものです。(画像提供:Monolithic Power Systems)

図4:LDOのアナログ閉ループ設計により、負荷による過渡的な要求に対し、非常に高速な応答が可能になっています。このような高性能は、DDR SRAMの終端処理などのアプリケーションに必要なものです。(画像提供:Monolithic Power Systems)

このLDOは、元々低ノイズで使いやすい特性を持っていますが、限界もあります。まず、スイッチングレギュレータに比べて効率が圧倒的に悪いため、システムの熱負荷が大きくなる問題と、バッテリ駆動ポータブル機器の駆動時間が影響を受ける問題があります。このような理由から、LDOは出力電流が1〜3A程度までの場合に使用されるのが最も一般的(MP20075の図を参照)で、3Aを超えて使用される場合は効率への「ペナルティ」が大きくなります。

また、LDOに固有の限界がもう一つあります。それは、LDOが提供できるのは降圧安定化のみであり、安定化されていない入力DC電源を公称値を超える値に昇圧することはできないということです。昇圧モードの出力が必要な場合、LDOはDC/DCレギュレータの選択肢から自動的に除外されます。

レイアウトの微調整とフィルタの追加

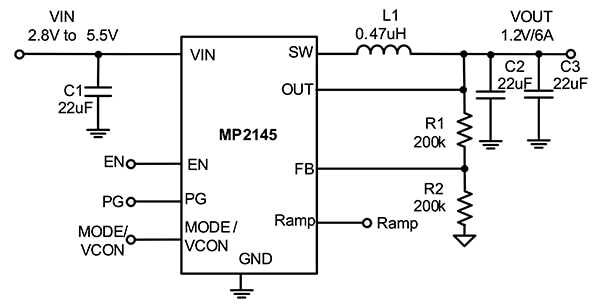

スイッチングレギュレータを使用する場合、昇圧モードでも降圧モードでも、そのスイッチング動作はノイズ源として付き物であり、避けられません。レギュレータが固定周波数で動作する場合、出力フィルタを追加することは簡単です。20mΩと12mΩのMOSFETを内蔵し、2 × 3ミリメートル(mm)の12ピンQFNパッケージに収められている5.5ボルト、6Aの同期降圧スイッチングレギュレータ「MP2145」について考えてみましょう(図5)。

図5:MP2145は、2 × 3mmのQFNパッケージに20mΩと12mΩのMOSFETを内蔵した、5.5ボルト、6Aの同期降圧スイッチングレギュレータです。(画像提供:Monolithic Power Systems)

図5:MP2145は、2 × 3mmのQFNパッケージに20mΩと12mΩのMOSFETを内蔵した、5.5ボルト、6Aの同期降圧スイッチングレギュレータです。(画像提供:Monolithic Power Systems)

MP2145などの同期降圧コンバータは、入力コンデンサCIN、ボディダイオードを備えた2つのスイッチ(S1、S2)、蓄電用パワーインダクタ(L)、出力コンデンサ(COUT)で構成されています。出力には、定常状態での出力電圧を平滑化するための出力コンデンサ(COUT)が配置されています。これらは初段フィルタを構成し、高周波電圧成分がグランドに戻るための低インピーダンス経路を提供することで、出力電圧リップルを低減します。一般に、このようなシャント出力コンデンサは、出力電圧のリップルを1mVまで効率的に低減することができます。

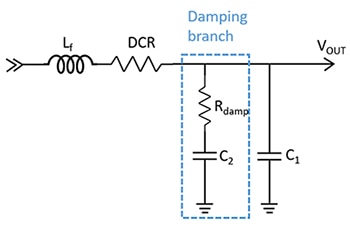

出力電圧のリップルをさらに低減するためには、2段目の出力フィルタが必要で、1段目の出力コンデンサにインダクタコンデンサ(LC)フィルタをカスケード接続します(図6)。フィルタインダクタ(Lf)は、意図した高周波領域では抵抗となり、ノイズエネルギーを熱として放散します。このインダクタは、追加のシャントコンデンサと組み合わせて、ローパスLCフィルタネットワークを形成します。

図6:MP2145などのスイッチングレギュレータの出力に2段目のLCフィルタを追加することで、出力リップルを低減することができます。(画像提供:Monolithic Power Systems)

図6:MP2145などのスイッチングレギュレータの出力に2段目のLCフィルタを追加することで、出力リップルを低減することができます。(画像提供:Monolithic Power Systems)

このフィルタを構成するインダクタ、コンデンサ、ダンピング抵抗のサイズを決めるための式やガイドラインが、ベンダーのデータシートやアプリケーションノートに記載されています。また、インダクタの直流抵抗(DCR)の最大値や飽和電流、コンデンサの等価直列抵抗(ESR)の最大値など、重要な2次パラメータも定義されています。インダクタンスの標準値は0.22マイクロヘンリー(μH)~1μHです。

また、上記の部品のレイアウトも最高の性能を実現するうえで重要です。誤ったレイアウトは、ラインや負荷の不安定やリップルの増加など安定性に関する問題を引き起こす可能性があります。MP2145の入力コンデンサ(Cin)は、できるだけIC端子の近くに配置してください(図7)。

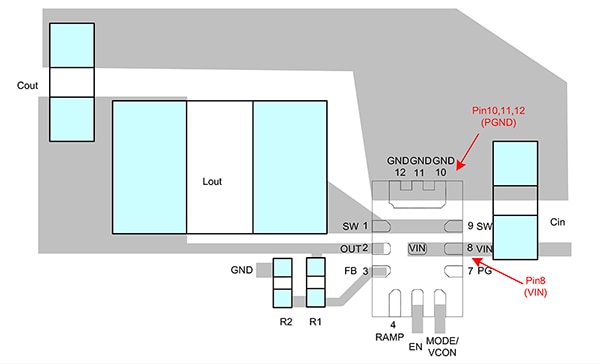

図7:MP2145の入力コンデンサ(ここでは右下のCin。図5の回路図ではC1)は、8番端子(電源入力端子)と10/11/12番端子(電源/設置端子)のできるだけ近くに配置してください。(画像提供:Monolithic Power Systems)

図7:MP2145の入力コンデンサ(ここでは右下のCin。図5の回路図ではC1)は、8番端子(電源入力端子)と10/11/12番端子(電源/設置端子)のできるだけ近くに配置してください。(画像提供:Monolithic Power Systems)

性能を保証するモジュール

モジュールにより、DC/DCレギュレータの実装はシステム統合の次の高みへと導かれます。これにより、外付け部品の選定や配置に関する懸念を最小限に抑えるか取り除き、品質が仕様どおりであることを保証することができます。モジュールには、厄介だった従来からの外付けインダクタを中心とした追加部品が内蔵されています。このため、EMCやリップル関連の性能に影響を与える受動部品のサイズ、配置、向きに関する問題を緩和することができます。

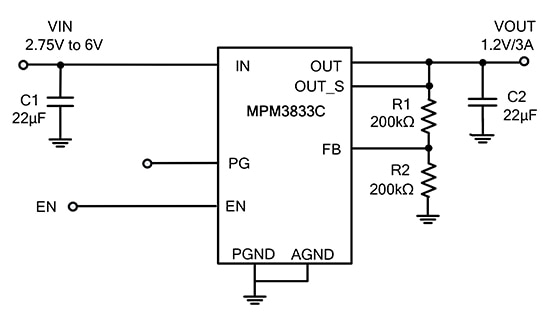

たとえば、MPM3833Cは、パワーMOSFETとインダクタを内蔵した降圧モジュールであり、2.75V〜6Vの入力電圧から最大3Aの連続出力電流を供給するとともに、負荷およびラインを大いに安定化します(図8)。設計に必要なのは、フィードバック抵抗、入力コンデンサ、出力コンデンサのみです。通常、外付け部品の中で指定や配置が最も難しいとされるインダクタは、本モジュールでは内蔵されているため、電磁干渉(EMI)やリップルを最小限に抑えるために必要な配置に関しては問題になりません。

図8:MPM3833C DC/DCモジュールは、従来は外付けだっため厄介な問題を引き起こす可能性のあったインダクタを設計および性能仕様により内蔵しています。(画像提供:Monolithic Power Systems)

図8:MPM3833C DC/DCモジュールは、従来は外付けだっため厄介な問題を引き起こす可能性のあったインダクタを設計および性能仕様により内蔵しています。(画像提供:Monolithic Power Systems)

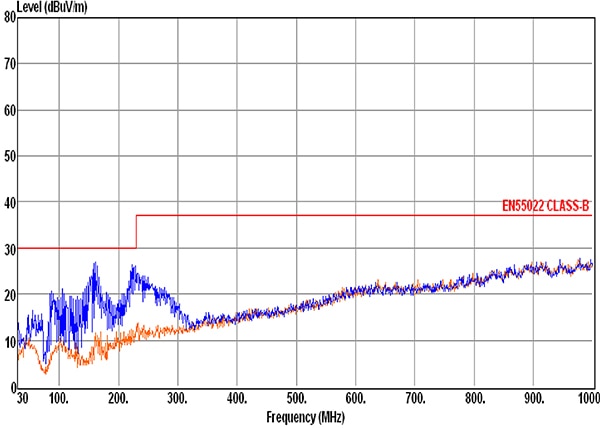

本モジュールは、超小型のQFN-18(2.5mm × 3.5mm × 1.6mm×mm)パッケージに収められており、リップル電圧は5mV(標準値)です。その低レベルの放射エミッション(EMI)は、EN55022クラスB規格に準拠しています。この規格は、図9では25℃においてVIN = 5ボルト、VOUT = 1.2ボルト、IOUT = 3A、CO = 22ピコファラッド(pF)の条件下で示されています。

図9:MPM3833C DC/DCモジュールのデータシートを見ると、放射エミッションに関するEN55022クラスB規格を十分に満たしていることが分かります。(画像提供:Monolithic Power Systems)

図9:MPM3833C DC/DCモジュールのデータシートを見ると、放射エミッションに関するEN55022クラスB規格を十分に満たしていることが分かります。(画像提供:Monolithic Power Systems)

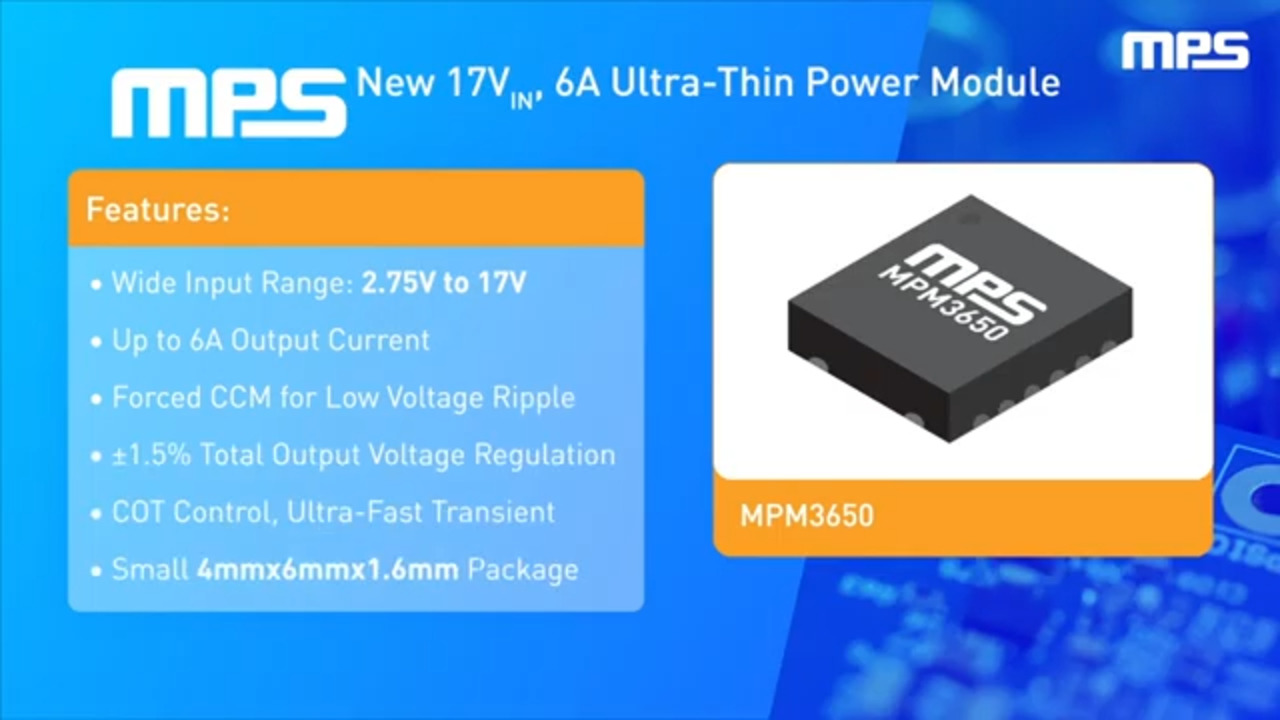

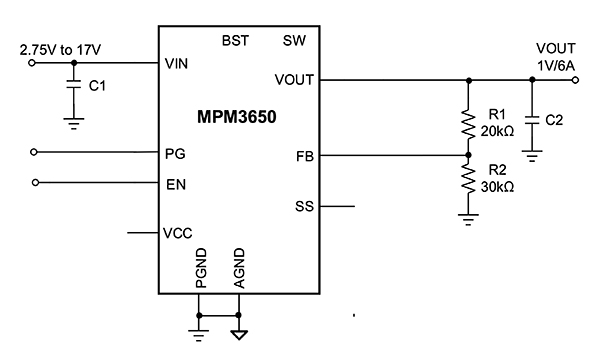

最新のマイクロパッケージ技術では、モジュールの全体的なサイズは、内部のダイよりもわずかに大きいか高いだけであり、低背化はますます重要な要素となっています。MPM3650は、1.2MHzの同期整流式降圧電源モジュールであり、インダクタを内蔵した完全一体型になっています(図10)。2.75~17ボルトの広い入力範囲にわたって、0.6~1.8ボルトの出力に最大6A、1.8ボルトを超えた出力に最大5Aの連続出力電流を供給し、高い負荷およびライン安定化を実現します。QFN-24パッケージは、MOSFETとインダクタを内蔵しながら、わずか4mm × 6mm × 1.6mmのサイズを実現しています。

図10:インダクタを内蔵したMPM3650モジュールは、4mm × 6mm × 1.6mmのパッケージに収納されており、最大1.8ボルトで最大6A、1.8ボルト超で5Aの電流を供給します。(画像提供:Monolithic Power Systems)

図10:インダクタを内蔵したMPM3650モジュールは、4mm × 6mm × 1.6mmのパッケージに収納されており、最大1.8ボルトで最大6A、1.8ボルト超で5Aの電流を供給します。(画像提供:Monolithic Power Systems)

モジュール式のもう一つの利点は、リップルノイズが無負荷時には約20mVに抑制され、6Aの全負荷時には約5mVにまで低下することです(図11)。これにより、多くの場合、外部フィルタを追加する必要がなくなり、設計の簡素化、フットプリントの縮小、BOM(部品表)の削減が可能になります。

図11:MPM3650モジュールのリップルノイズは、ゼロ負荷時に約20mV、全負荷時に約5mVと規定されています。(画像提供:Monolithic Power Systems)

図11:MPM3650モジュールのリップルノイズは、ゼロ負荷時に約20mV、全負荷時に約5mVと規定されています。(画像提供:Monolithic Power Systems)

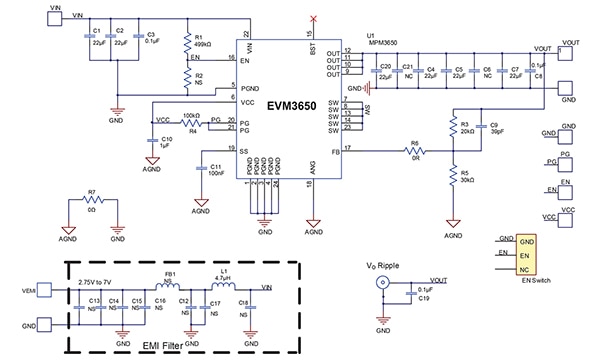

DC/DCレギュレータモジュールの静的および動的性能がシステム要件を満たしているかどうかを評価するために、データシートの記載内容を超えて実際に動かしてみると役に立つ場合がよくあります。この評価プロセスを短縮するために、Monolithic Power Systemsは、MPM3650用の63.5mm × 63.5mm × 1.6mmの4層構造の評価ボード「EVM3650-QW-00A」を提供しています(図12)。

図12:EVM3650-QW-00A評価ボードを使用することで、MPM3650 DC/DCモジュールの潜在的ユーザーは、自分のアプリケーションにおける性能を迅速に評価することができます。(画像提供:Monolithic Power Systems)

図12:EVM3650-QW-00A評価ボードを使用することで、MPM3650 DC/DCモジュールの潜在的ユーザーは、自分のアプリケーションにおける性能を迅速に評価することができます。(画像提供:Monolithic Power Systems)

本評価ボードとそのデータシートは、複数の用途に役立ちます。第一に、データシートには明示または記載されていないMPS3650の多くの性能特性を幅広い動作条件の下で簡単に評価することができます。次に、本評価ボードのデータシートには、完全な回路図、BOM、ボードレイアウトの詳細がすべて記載されているため、MPS3650のユーザーはそれらを自分の設計に利用することで、リスクを減らし、不確実性を最小限に抑えることができます(図13)。

図13:EVM3650-QW-00A評価ボードパッケージには、リスクと不確実性を低減するために、完全な回路図、BOM、ボードレイアウトの詳細が含まれています。(画像提供:Monolithic Power Systems)

図13:EVM3650-QW-00A評価ボードパッケージには、リスクと不確実性を低減するために、完全な回路図、BOM、ボードレイアウトの詳細が含まれています。(画像提供:Monolithic Power Systems)

この評価ボードを使用することで、設計者は本モジュールの性能をより深く理解することができるので、デザインインの信頼性を高め、市場投入までの時間を最短に抑えることができます。

もうひとつのタイプのノイズがあります。

設計者が「ノイズ」と言う場合、ほとんどの場合、リップルやEMIなど、回路内で発生する電子ノイズのことを指しています。しかし、スイッチングレギュレータでは、さらに別のタイプのノイズである「音響ノイズ」が発生する可能性があります。このようなノイズは、人間の可聴域(一般的には20kHz)を超えて動作するレギュレータでは問題になりません。しかし、可聴域で動作するスイッチングレギュレータもありますが、はるかに高い周波数で動作するスイッチングレギュレータでも、アイドル時やスタンバイ時には低い可聴域で動作することで消費電力を抑える場合があります。

この可聴域のノイズ(可聴ノイズ)は、圧電効果と磁気ひずみ効果というよく知られた2つの物理現象のいずれか、または両方によるものです。圧電効果による場合は、クロックによる回路の電気的振動により、セラミックコンデンサなどの部品がスイッチングクロックに同期して振動します(電気エネルギーがコンデンサの結晶材料によって機械的な動きに変換される)。圧電効果とやや並行している磁気ひずみ効果の場合、インダクタやトランスのコアなどの磁性体は、クロック駆動による磁化サイクルの中で、その形状や寸法が変化します。そして、影響を受けたコンデンサやインダクタ/トランスが機械的な「ドライバ」として作用し、回路基板全体を共振させ、音の振動を増幅し、送信します。

これらの影響により、耳の良い人が電子機器の近くにいると、小さな音でハムノイズが聞こえると訴えることがよくあります。なお、この音響ノイズは、低周波の50/60Hzの電源回路の部品からも発生することがあるので、高音域の聴力がない人でもハムノイズが聞こえることがあります。

音響ノイズへの対応には、電子ノイズの減衰の場合とは異なるアプローチと技術が必要です。

まとめ

LDOは、DCレールのリップルとEMIの両問題を解決するために、無ノイズまたは低ノイズのソリューションを提供しますが、数アンペアを超えるレギュレータとしては、一般的には有効な選択肢ではありません。そのような選択肢としては、適切なフィルタを施したスイッチングレギュレータや、低ノイズ性能に特化して設計されたスイッチングレギュレータがあります。

また、もう一つのソリューションとしては、インダクタなどの部品を小型パッケージに組み込んだ一体型のDC/DCレギュレータモジュールがあります。これらはレイアウトや部品の選定に関する設計の不確実性を低減すると同時に、そのサブシステムの性能も完全にテストされてはっきりと数値化されています。

お勧めの記事

免責条項:このウェブサイト上で、さまざまな著者および/またはフォーラム参加者によって表明された意見、信念や視点は、DigiKeyの意見、信念および視点またはDigiKeyの公式な方針を必ずしも反映するものではありません。